Trench type silicon carbide reverse blocking MOSFET device and production method thereof

A silicon carbide, trench-type technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

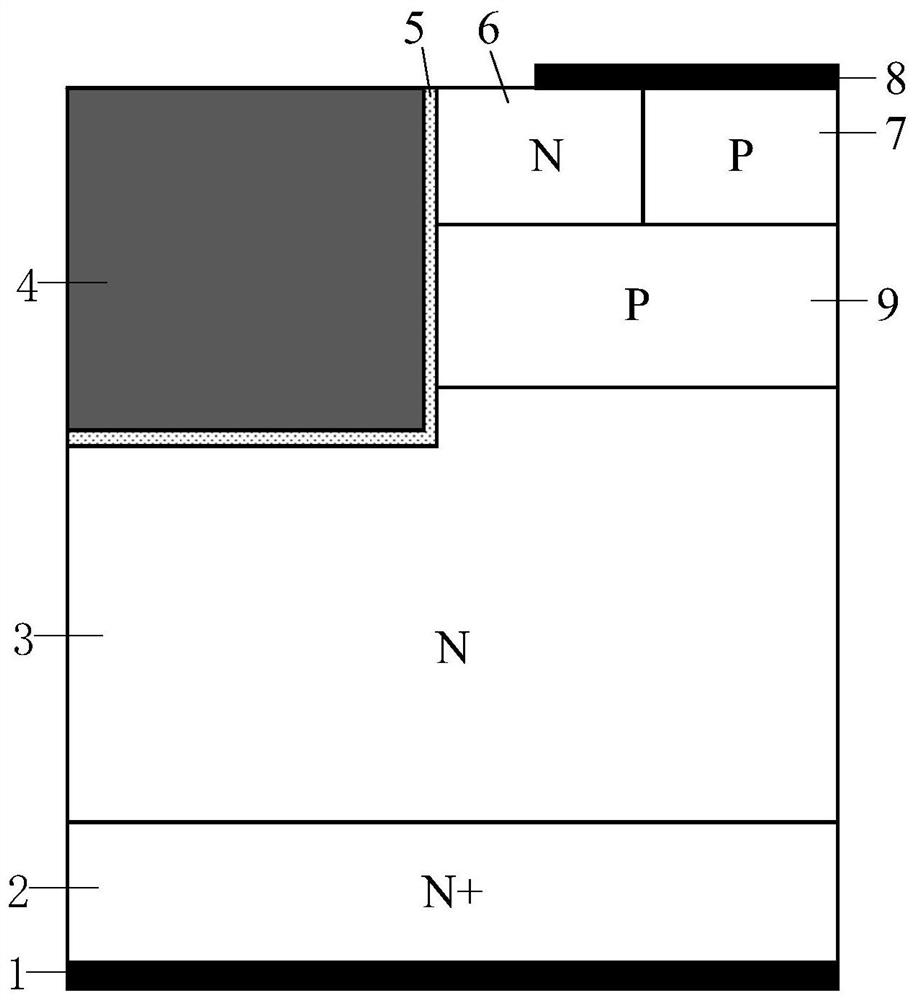

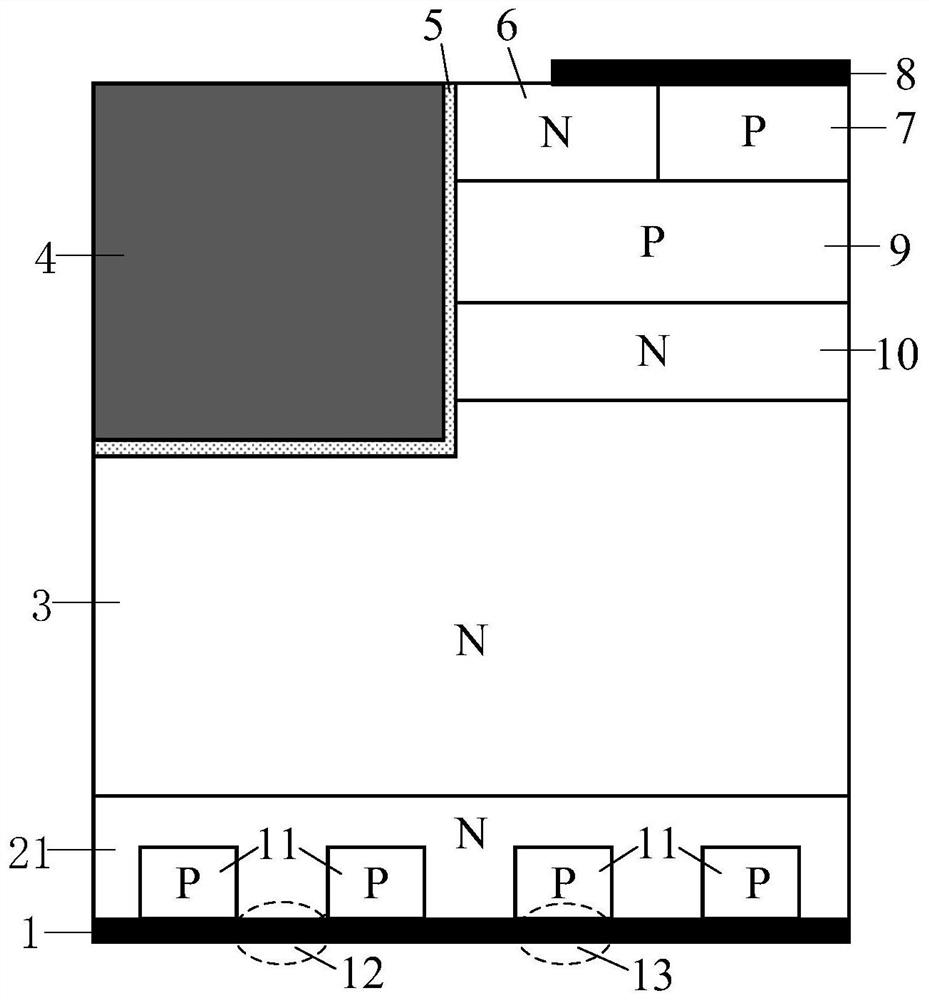

[0087] A trench type silicon carbide reverse resistance MOSFET, its semi-cellular structure is as follows figure 2 As shown, it includes: a back drain metal 1, a second N-type silicon carbide buffer layer 21, and an N-type silicon carbide epitaxial layer 3, which are stacked sequentially from bottom to top.

[0088] The gate 4 and the first N-type silicon carbide buffer layer 10 are arranged above the N-type silicon carbide epitaxial layer 3, the first N-type silicon carbide buffer layer 10 is located on the right side of the gate 4, and the first N-type silicon carbide buffer layer 10 is arranged above the first N-type silicon carbide buffer layer 10 A P-type silicon carbide base region 9, an N-type silicon carbide source region 6 and a P-type silicon carbide source region 7 are arranged above the P-type silicon carbide base region 9; the N-type silicon carbide source region 6 and the P-type silicon carbide The silicon source region 7 is connected left and right; the source ...

Embodiment 2

[0103] A trench type silicon carbide reverse resistance MOSFET, its semi-cellular structure is as follows image 3 As shown, the difference between this embodiment and Embodiment 1 is that: the second N-type silicon carbide buffer layer 21 has a non-adjacent P-type floating region 17; the bottom of the P-type floating region 17 is not connected to the back drain. Contact is formed between the pole metals 1, that is, the P-type floating region 17 is completely floating in the second N-type silicon carbide buffer layer 21; a Schottke is formed between the second N-type silicon carbide buffer layer 21 and the back drain metal 1. base contact.

[0104] Preferably, all silicon carbide materials are replaced with gallium nitride, gallium oxide, boron nitride, and silicon materials.

[0105] This embodiment also provides a method for preparing the trench-type silicon carbide reverse resistance MOSFET device, including the following preparation steps:

[0106] Step 1: using an epita...

Embodiment 3

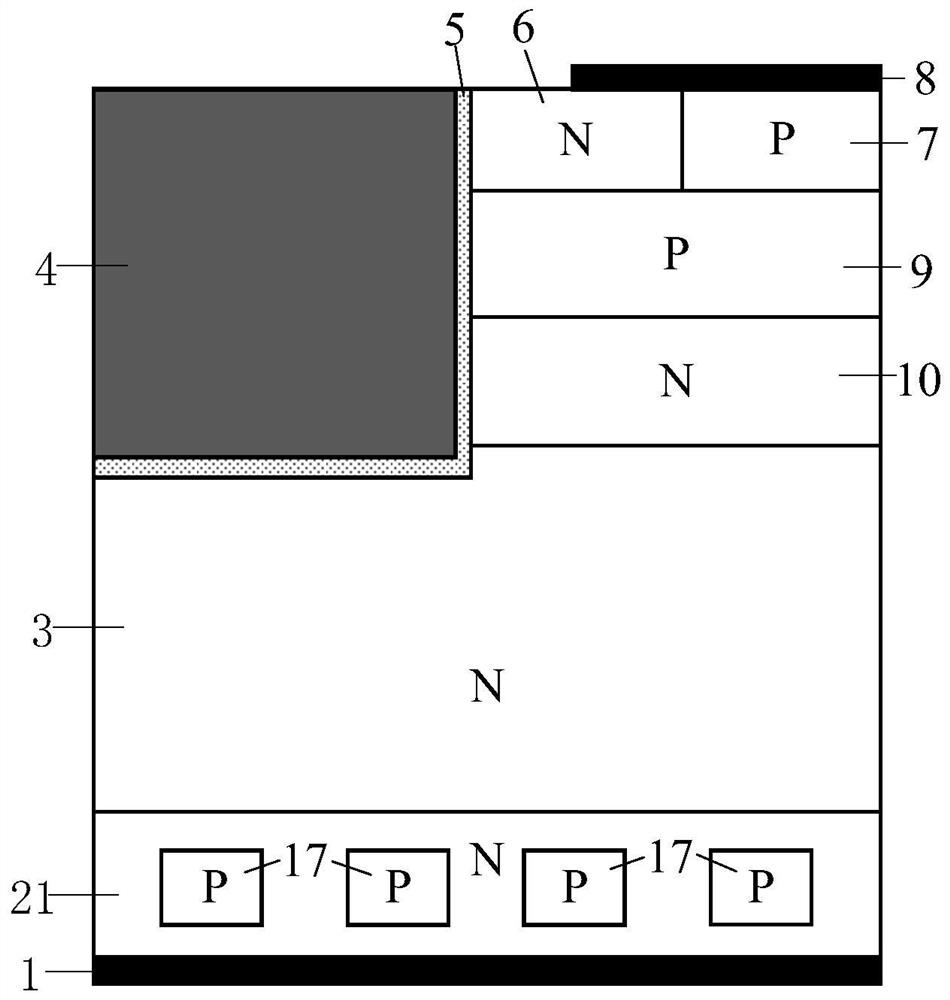

[0116] A kind of derivation structure of embodiment 1, its semicellular structure such as Figure 4 As shown, the difference between this embodiment and Embodiment 1 is that: a P-type buried layer 14 is provided at the bottom of the gate dielectric layer 5 . The specific principle is: since silicon carbide has a higher critical breakdown electric field than silicon, the higher critical breakdown electric field causes the electric field in the gate dielectric layer of the silicon carbide MOSFET device to be much larger than that of the silicon-based MOSFET gate when it breaks down. The electric field in the dielectric layer reduces the reliability of the gate dielectric layer. The P-type buried layer 14 introduced in this embodiment can effectively reduce the magnitude of the electric field in the gate dielectric layer at the bottom corner of the trench and improve the forward withstand voltage capability.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More