MOSFET with high-resistance layer, preparation method of MOSFET, and power transistor module

A high-resistance layer and epitaxial layer technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of increasing on-resistance, decreasing power quality factor, and decreasing device power quality factor. The effect of electron concentration, increasing breakdown voltage, and reducing leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

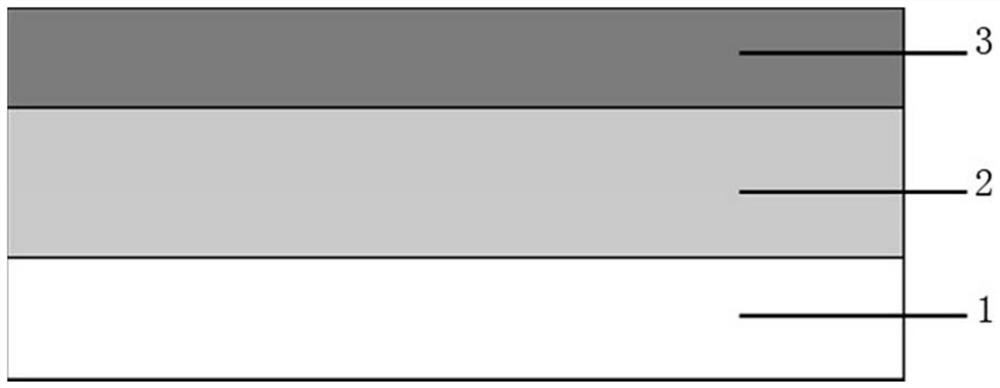

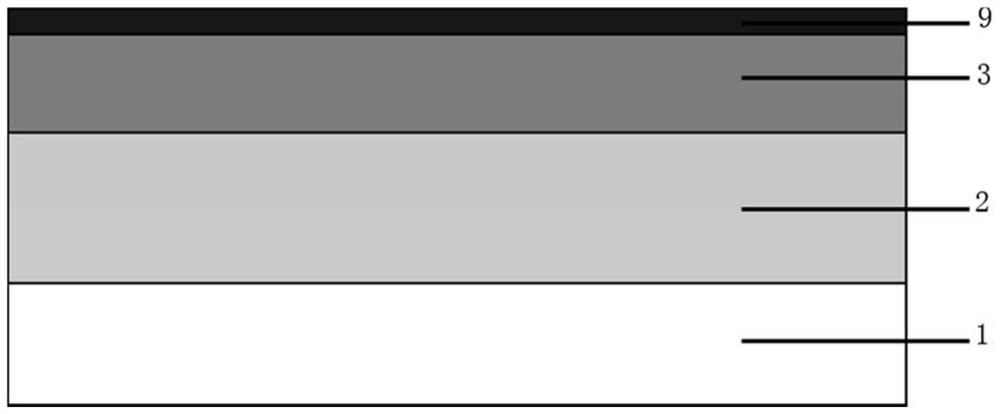

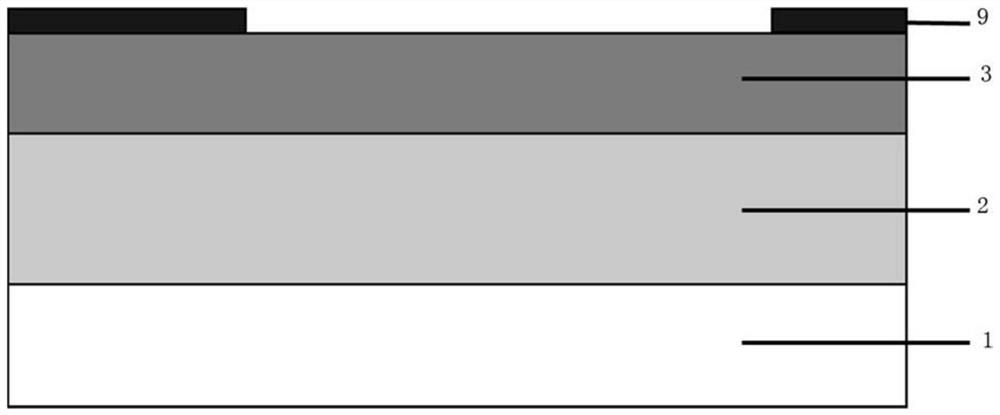

[0024] The invention provides a MOSFET with a high resistance layer, Figure 8 A schematic diagram of the structure of a MOSFET with a high-resistance layer is schematically shown. Including semi-insulating substrate layer 1, buffer layer 2, epitaxial layer 3, high resistance layer 4; source electrode 5, drain electrode 6, gate electrode 7; wherein, semi-insulating substrate layer 1, buffer layer 2, epitaxial layer 3 from bottom to top Arranged in sequence; the source electrode 5 and the drain electrode 6 are arranged on the upper surface of the epitaxial layer 3, and the source electrode 5 and the drain electrode 6 form ohmic contact with the epitaxial layer 3; a gate dielectric 8 is arranged on the upper surface of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More