Current tolerance type multi-layer PCB and preparation method thereof

A current withstand, adhesive layer technology, used in multilayer circuit manufacturing, printed circuit manufacturing, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0062] Another embodiment of the present invention provides a method for manufacturing a current-resistant multilayer PCB 100 . The preparation method comprises the steps of:

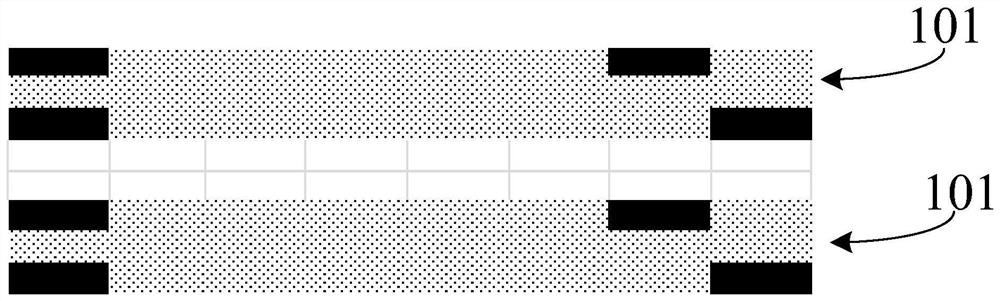

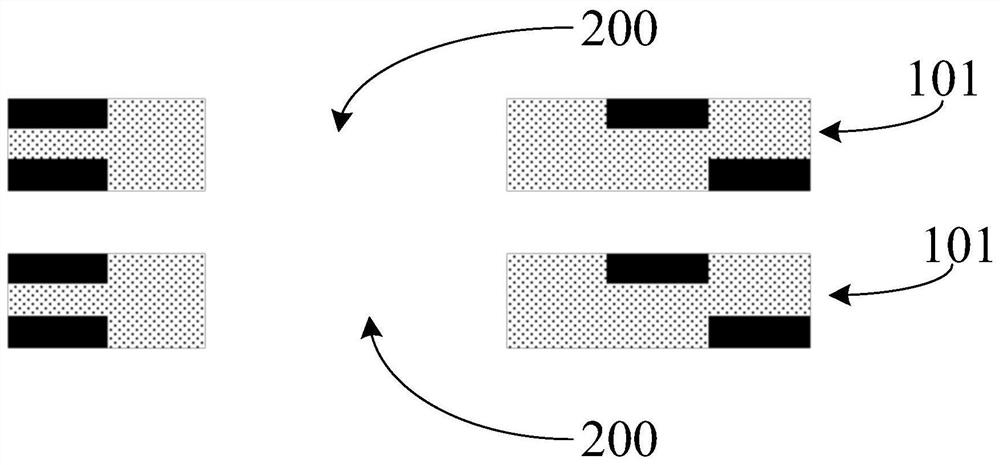

[0063] S101: Opening holes 200 on multiple inner core boards 101 and multiple prepregs to obtain through-hole core boards and through-hole prepregs respectively. For example, two inner core boards 101 are used to prepare the PCB, and the structures of the two inner core boards 101 are as follows: figure 2 As shown, after the through hole 200 is opened, a through-hole core board is obtained, and the structure of the through-hole core board is as follows image 3 shown.

[0064] S102 : Stack the through-hole core boards and the through-hole prepregs so that the through-hole prepregs are arranged between adjacent through-hole core boards, and the respective through holes 200 are connected to obtain a pre-arrangement board.

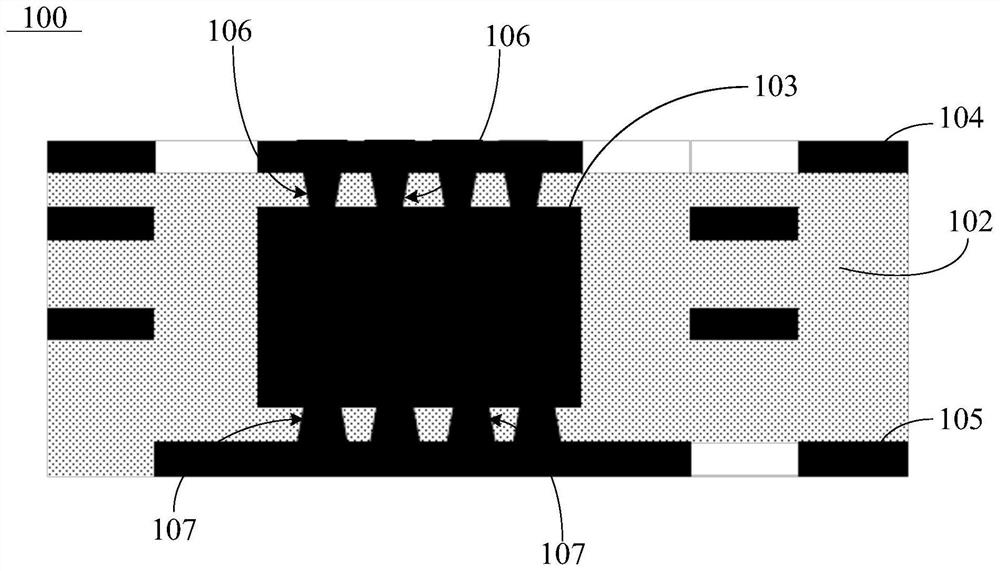

[0065] S103: Put the conductive medium 103 into the connected through holes 20...

Embodiment 1

[0091] The preparation method of PCB in the present embodiment is:

[0092] S201: Take two copper-clad laminates with a copper thickness of 3 oz, cut the inner core board as required, and make the inner layer graphics. The steps of making the inner layer graphics are grinding, rolling, exposure and development in sequence. The roll film process uses 1.5mil dry film, and the exposure process uses negative film. After the inner layer graphics are made, the inner layer circuit is inspected by graphic inspection (AOI optical inspection) to check whether the inner layer graphic circuit has open circuit, short circuit, erosion and other problems.

[0093] S202: Carry out browning treatment on the inner layer core boards that pass the pattern inspection. The steps of browning treatment are: board loading, degreasing, water washing, presoaking, browning, water washing, board drying, cooling, and board removal in sequence.

[0094] S203: Open holes for multiple prepregs: take two 30...

PUM

| Property | Measurement | Unit |

|---|---|---|

| frequency | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| pore size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More