Rear-end integrated structure of memristor unit and CMOS (complementary metal oxide semiconductor) circuit and preparation method of rear-end integrated structure

A memristor and circuit technology, applied in the field of microelectronic device technology and integrated circuits, to achieve the effect of realizing electrical connection, saving quantity, and saving process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

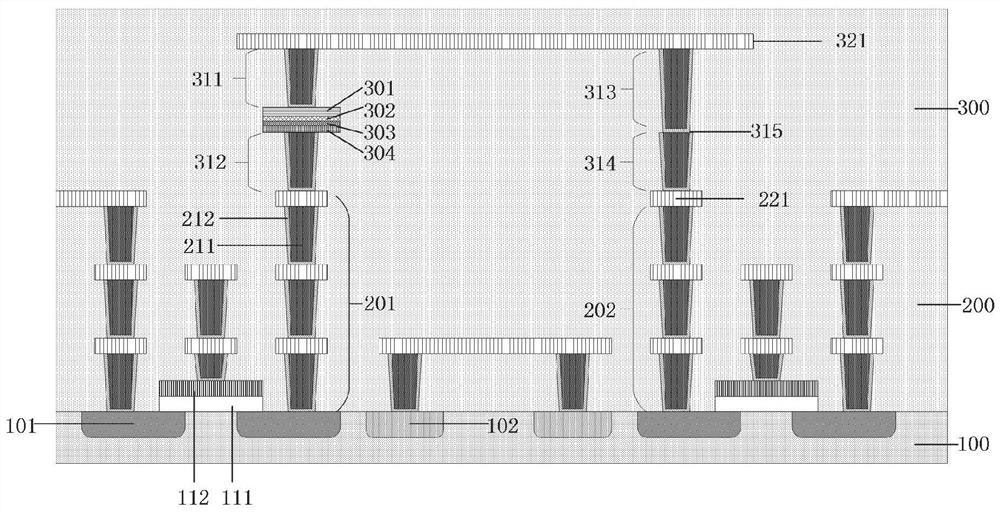

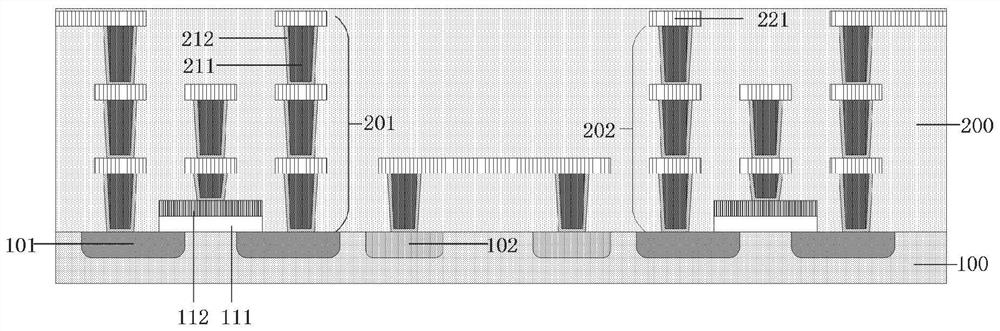

[0056] A back-end integrated structure of a memristor unit and a CMOS circuit, such as figure 1 As shown, including: MOSFET structure, metal interconnection layer and memristor layer distributed sequentially from bottom to top;

[0057] The MOSFET structure includes a substrate 100 and a first transistor and a second transistor prepared on the substrate 100; wherein, the first transistor and the second transistor are transistors in a CMOS circuit; in some optional implementation manners, the MOSFET structure is in the form of Based on the single crystal silicon substrate, including transistors and other electronic components based on CMOS front-end technology, together constitute a basic planar bulk silicon MOSFET structure; wherein, the transistor includes source / drain doped regions 101, substrate heavily doped Region 102, gate oxide layer 111, polysilicon gate 112 and so on. It should be noted that the MOSFET structure may also be other MOSFET structures such as an advanced...

Embodiment 2

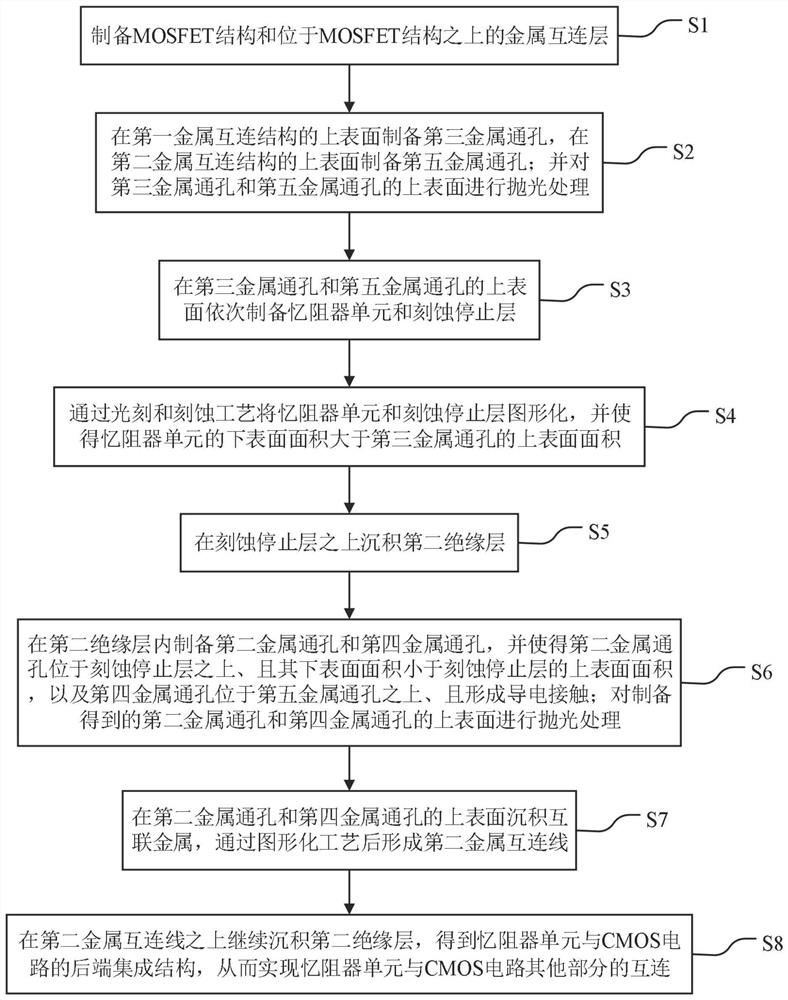

[0070] A method for preparing a back-end integrated structure of a memristor unit and a CMOS circuit, such as figure 2 shown, including the following steps:

[0071] S1. Prepare a MOSFET structure and a metal interconnection layer located on the MOSFET structure; wherein, the MOSFET structure includes a substrate and a first transistor and a second transistor prepared on the substrate; the first transistor and the second transistor are in a CMOS circuit The transistor; the metal interconnection layer includes a first insulating layer, and a first metal interconnection structure and a second metal interconnection structure located inside the first insulating layer;

[0072]Wherein, the metal interconnection layer includes a first insulating layer, and a first metal interconnection structure and a second metal interconnection structure located inside the first insulating layer; in some optional implementation manners, the number of layers of the above metal interconnection stru...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More