Solar cell and preparation method thereof

A solar cell and conductive type technology, applied in the field of solar energy, can solve problems such as reducing the conversion efficiency of solar cells, and achieve the effects of reducing losses, increasing effective output, and improving effective output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

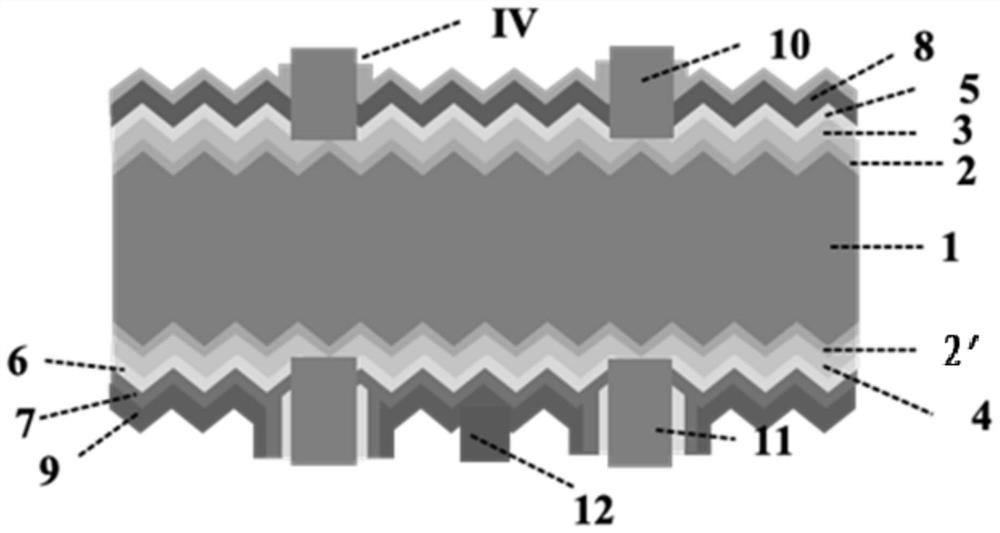

[0057] figure 1 It is a vertical cross-sectional view of a solar cell according to an embodiment of the present application.

[0058] The solar cell provided in this embodiment is a part of a solar module, that is, a component capable of generating photocurrent, and its structure includes a crystalline silicon substrate of the first conductivity type, and the crystalline silicon is single crystal silicon or polycrystalline silicon, and the so-called first conductivity type is the same as A concept corresponding to the second conductivity type that will be described below, where the first conductivity type is n-type, the second conductivity type is p-type, and if the first conductivity type is p-type, the second conductivity type is n type.

[0059] refer to figure 1 As shown, the solar cell in this application is described in detail by taking the first conductivity type as n-type as an example. The crystalline silicon substrate is an n-type crystalline silicon substrate 1, a...

Embodiment 2

[0069] This embodiment also provides a preparation method for preparing the solar cell of the previous embodiment, such as Figure 2a~2q As shown, this embodiment takes an n-type crystalline silicon substrate as an example to describe the preparation process of the solar cell as follows.

[0070] Step 1: For n-type 158.78*158.75mm with a resistivity of 0.5-3Ω.cm 2 The single crystal silicon wafer 1 is cleaned, the damaged layer is removed, and the texture is made to form a random pyramid structure on the surface of the crystal silicon wafer;

[0071] Step 2: Using the LPCVD method, the first tunneling thin film layer 2 and the second tunneling thin film layer 2' are grown on both sides of the n-type textured silicon wafer 1, and the first tunneling thin film layer and the second tunneling thin film layer are The thickness is 1-3nm;

[0072] Step 3: growing double-sided intrinsic amorphous silicon layers 3' and 4' on the tunneling thin film layer, and the thickness of the int...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More