Contact portion of semiconductor device and manufacturing method thereof including thin film transistor array panel for contact portion display device and manufacturing method thereof

A technology of thin-film transistors and semiconductors, which is applied in semiconductor/solid-state device manufacturing, transistors, semiconductor devices, etc., and can solve problems such as uneven organic insulating layers and inconsistent protrusions of reflective films

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

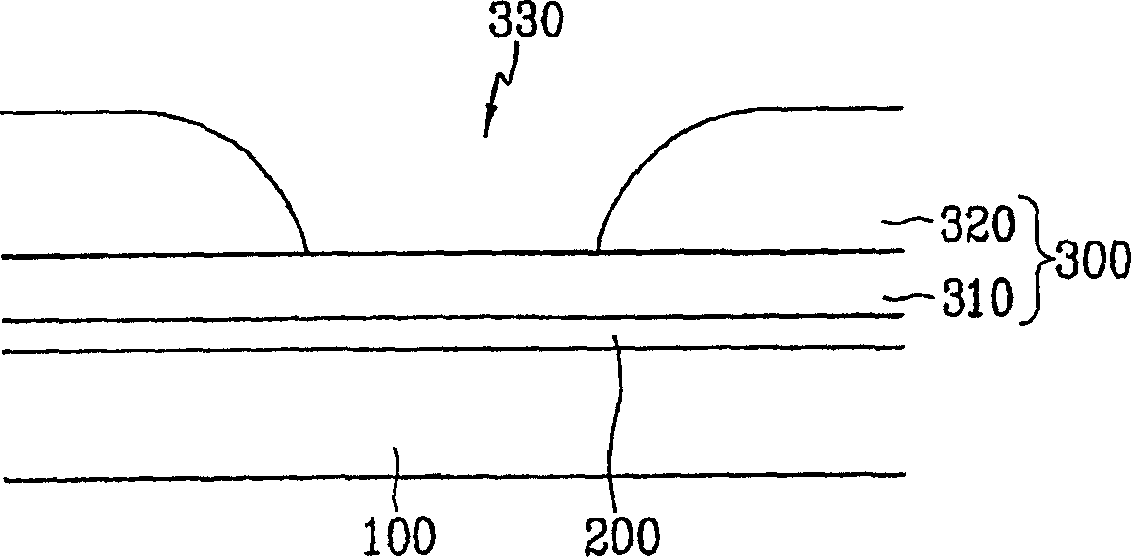

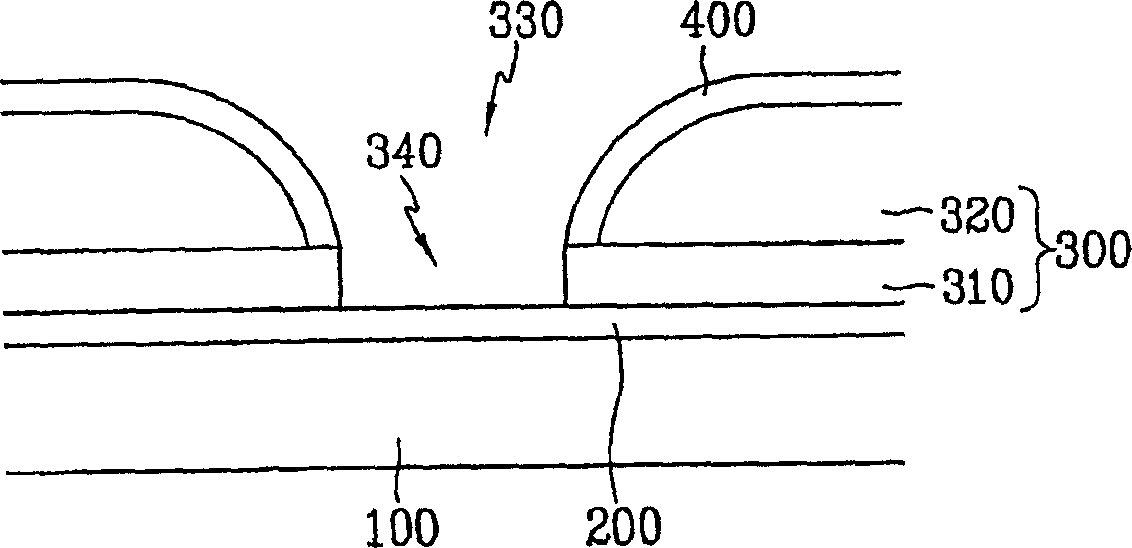

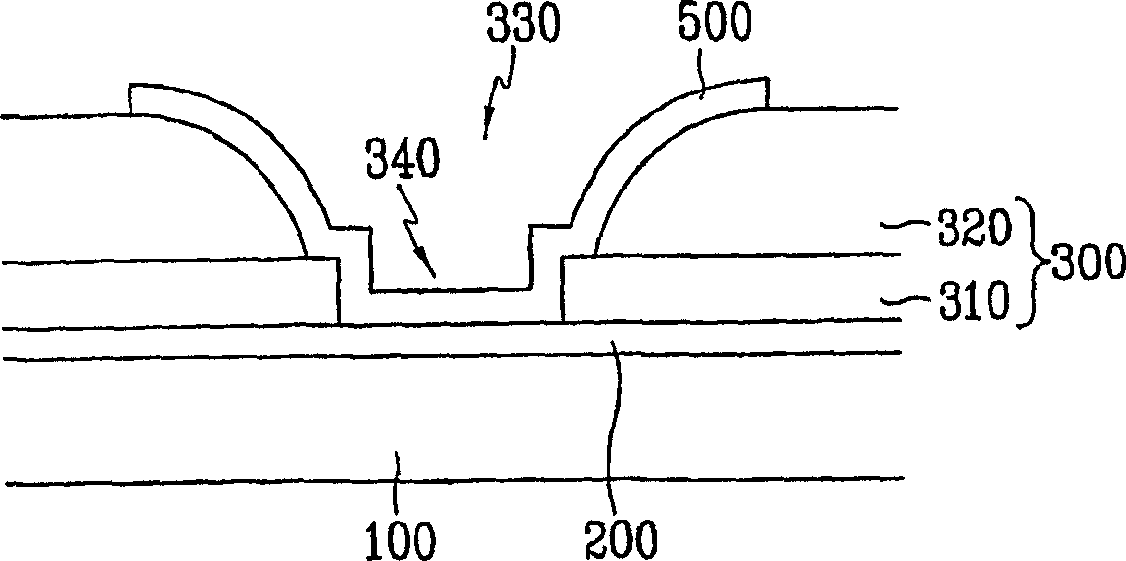

[0045] Now, a contact structure of a semiconductor device and a method of manufacturing the same according to an embodiment of the present invention, a TFT array plate including a contact structure and a method of manufacturing the same will be described with reference to the accompanying drawings, so that those skilled in the art can easily implement the present invention.

[0046] First, a method for manufacturing a contact structure of a semiconductor device according to an embodiment of the present invention will be described.

[0047] Generally, a semiconductor device has multilayer wiring interposed between interlayer insulating layers. The interlayer insulating layer is preferably made of a material with a low dielectric constant in order to minimize interference between signals flowing in different wirings, and to electrically connect different wiring layers transmitting the same signal to each other through a contact hole provided at the interlayer insulating layer. c...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More