Nitride and polysilicon interface with titanium layer

a polysilicon and titanium layer technology, applied in the direction of semiconductor devices, electrical devices, semiconductor/solid-state device details, etc., can solve the problems of low interface resistance, low resistance of the layer including the interface metal, and low nitrogen content, so as to reduce the resistance of the structure, fast destroy the barrier, and reduce the rate of any lateral oxidation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

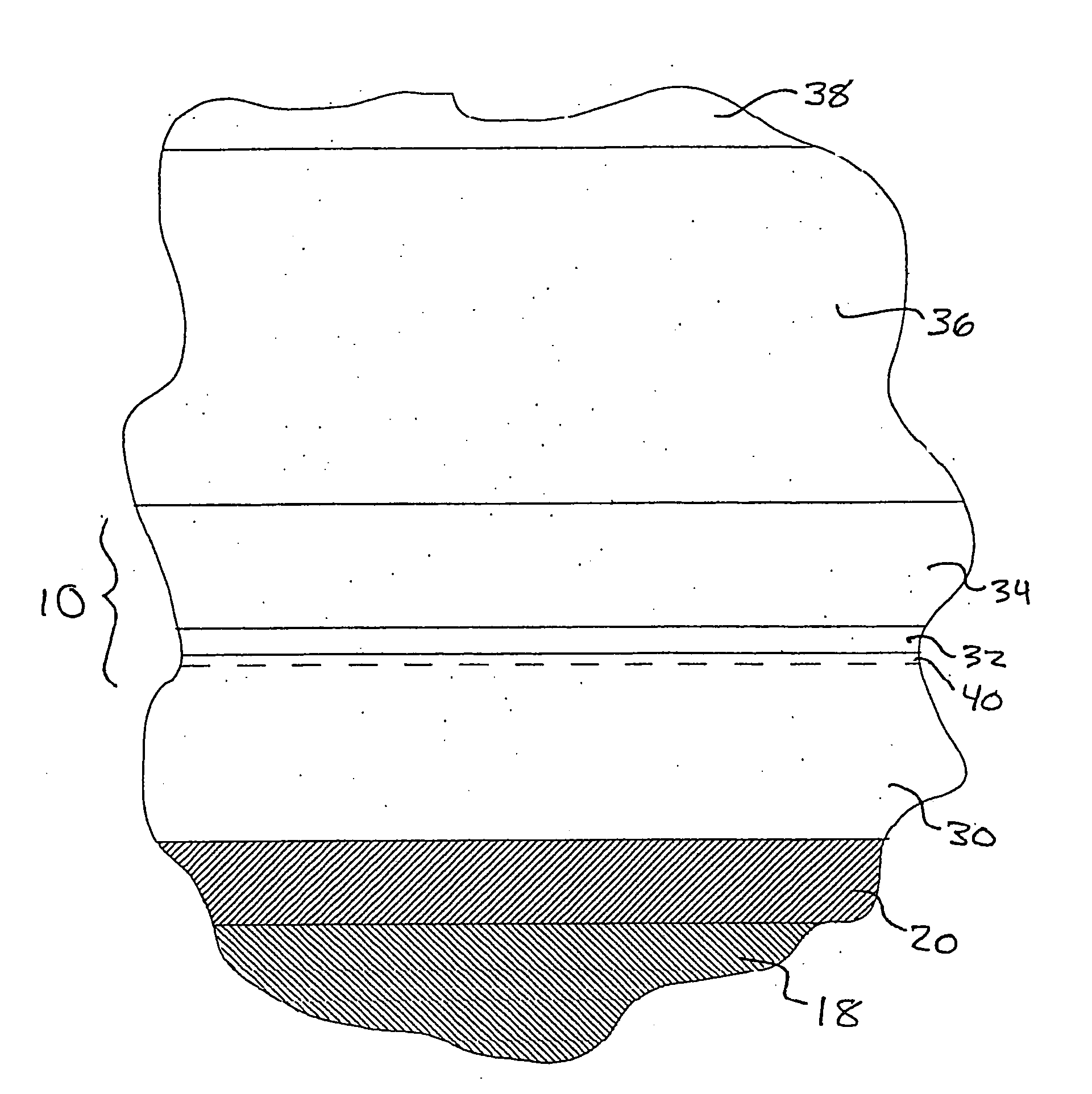

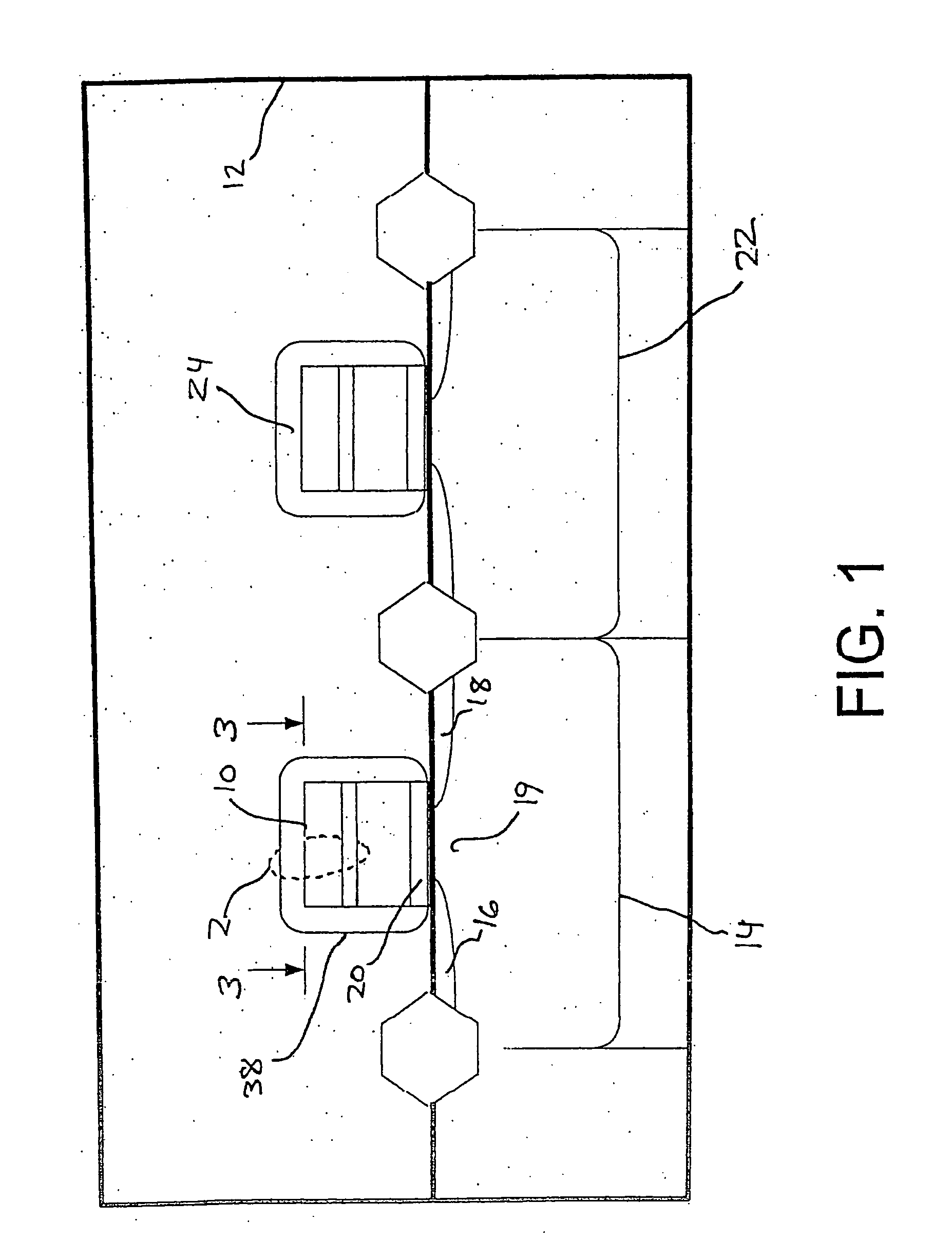

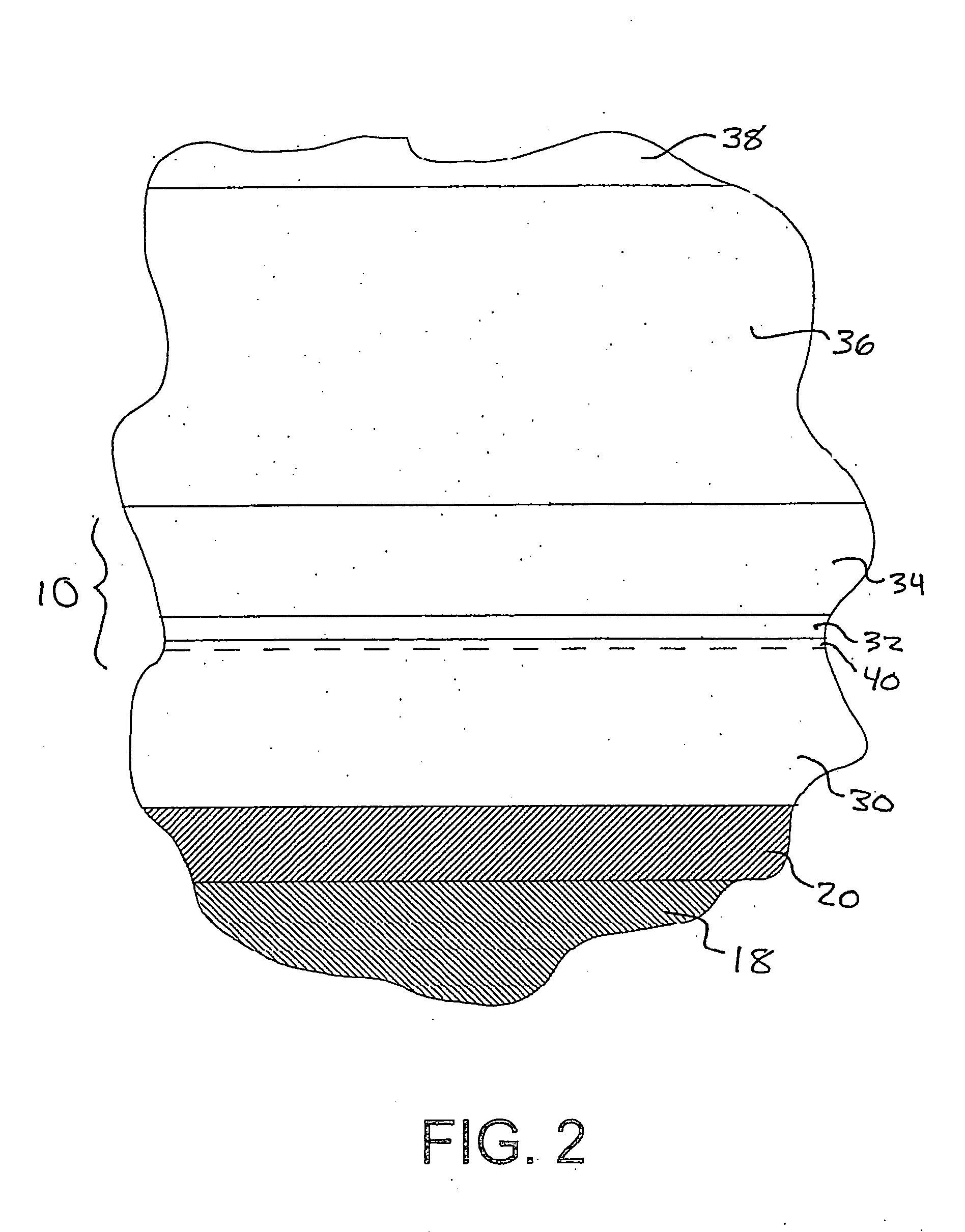

[0026] As depicted in FIG. 1, a conductive structure 10 according to one embodiment of the invention may be incorporated in an integrated circuit. Such a device may include large numbers of electronic elements in a unitary structure such as a chip or wafer. A small fragment of the unitary structure 12 is shown in FIG. 1. In the depicted structure, the conductive element 10 serves as the gate of a field effect transistor or FET 14. The FET includes a pair of n+-doped silicon regions 16 and 18, which serve as the source and drain of the FET, and a p-doped region 19 forming the channel. Conductive structure 10 is separated from the channel region 19 by an insulating layer 20. FET 14 may be part of a CMOS structure including a further FET 22 having opposite doping and associated with a further conductive element 24.

[0027] The gate insulator layer 20 can include various insulating materials such as silicon oxide, silicon oxynitride, silicon nitride, and so-called “high-k” insulators wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More