Ultra low-loss CMOS compatible silicon waveguides

a technology of cmos and silicon, applied in the direction of optical waveguide light guide, instruments, optics, etc., can solve the problems of high optical loss along the rib waveguide, etchant tends to roughen the exposed sidewall surface, and strip waveguides exhibit relatively high optical loss through their (relatively rough) sidewalls, etc., to achieve low loss and lower loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

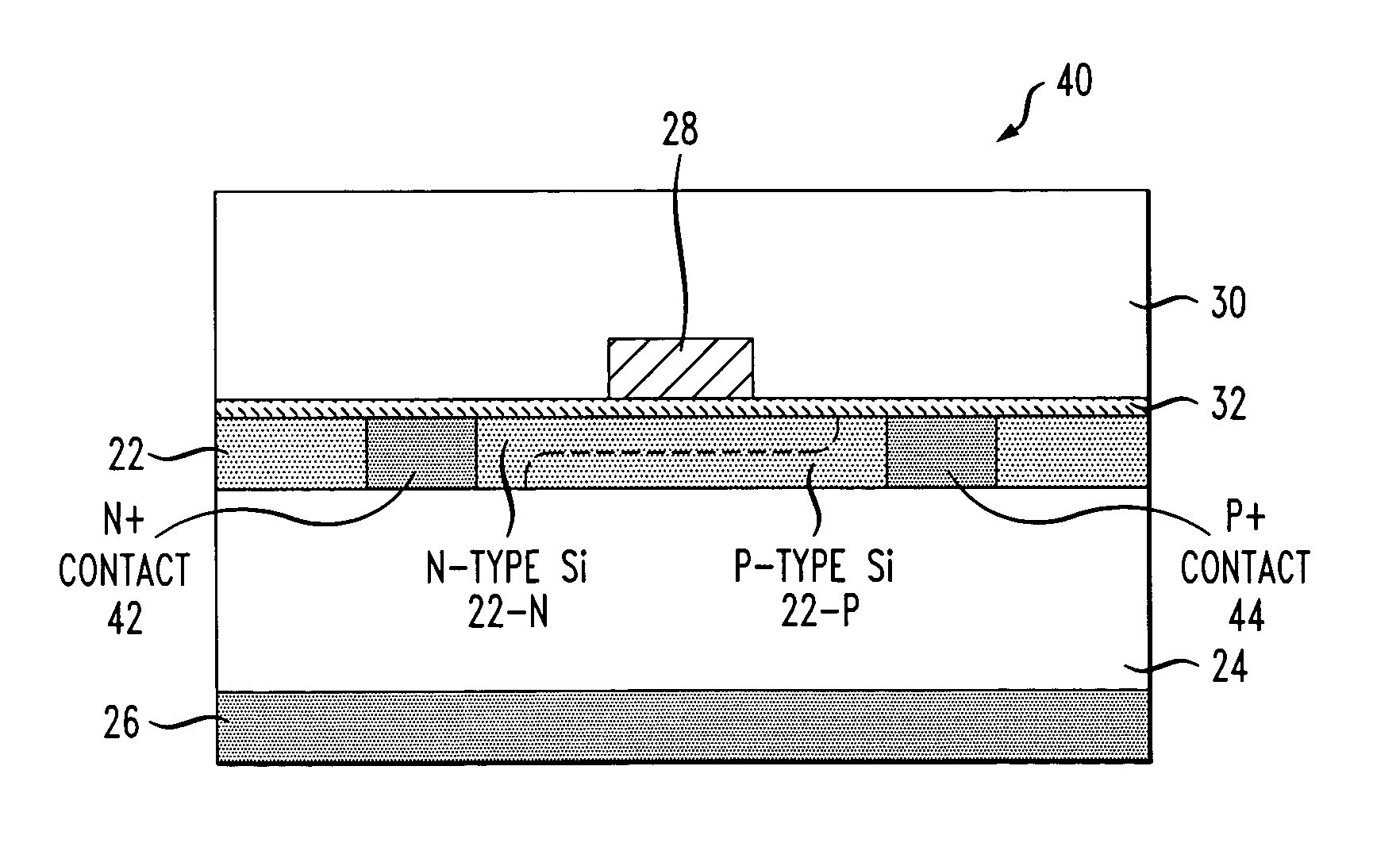

[0023]FIG. 1 illustrates an SOI-based silicon rib waveguide structure 1 as typical in the prior art. The longitudinal z-axis indicates the direction of light propagation, indicated by arrows 2, with the transverse y-direction and x-direction referred to as the “horizontal” and “vertical” directions, respectively. Silicon rib waveguide structure 1 generally consists of a relatively thin single crystal silicon surface layer 3 (generally referred to hereinafter as the “SOI layer”) bonded to a relatively thick silicon substrate 4, with an isolation layer 5 therebetween (thus forming the silicon-on-insulator (SOI) structure). Rib structure 6 is generally fabricated by reactive ion etching (RIE) a pair of parallel trenches 7 in SOI layer 3. Rib structure 6 is defined as having a top surface 8 and opposing sidewalls 9, 10. The optical mode profile O is also shown in FIG. 1. As mentioned above, the use of an etching technique to create sidewalls 9 and 10 results in allowing a significant po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More