CDMA power amplifier design for low and high power modes

a power amplifier and low power mode technology, applied in the direction of amplifier combinations, high frequency amplifiers, gain control, etc., can solve the problems of low power mode response, low power mode operation, etc., to improve the response in hp mode, improve the performance of the power amplifier, and reduce the loss of insertion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

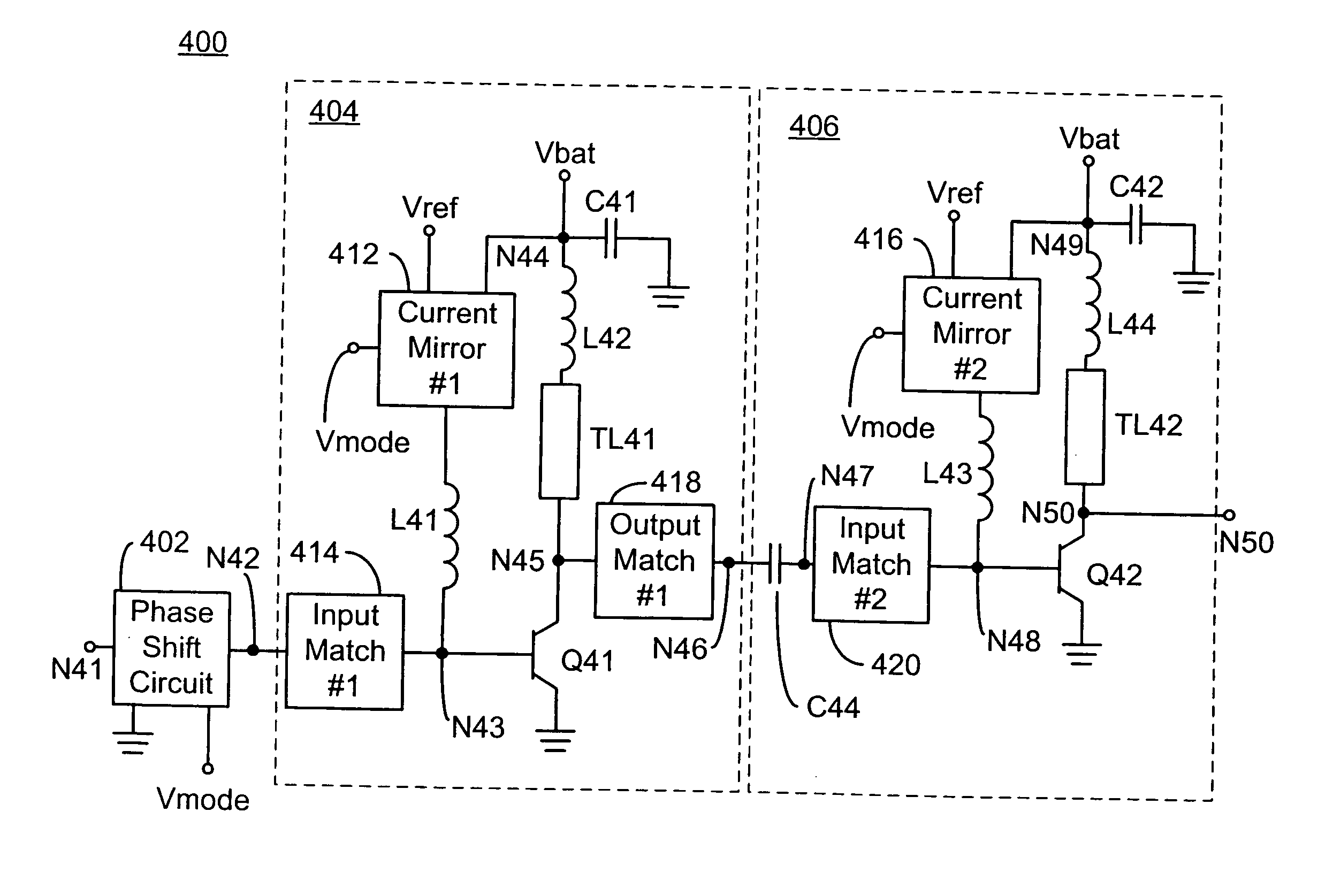

[0061]FIG. 4 shows power amplifier 400 in accordance with the present invention. Power amplifier 400 can serve as the power amplifier portion of power amplifier / load circuit 124 seen in FIG. 1. An RF signal input to power amplifier 400 at input node N41 may be phase shifted by phase shift circuit 402, first amplifier stage 404, and second amplifier stage 406, before exiting at output node N50.

[0062] Phase shift circuit 402 helps minimize phase discontinuity when switching between HP and LP modes in order to preserve phase coherency of the output signal. The RF signal at output node N42 is phase shifted relative to the signal at input node N41 depending on the Vmode signal.

[0063] As is known to those skilled in the art, the Vmode signal is a voltage level controlled by a dictated controller, such as a processor or the like, belonging to the device in which the power amplifier is resident. In the present invention such a controller (not shown) changes the value of the Vmode signal w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More