Solid-state imager and solid-state imaging device

a solid-state imager and imaging device technology, applied in the direction of radio frequency controlled devices, television system scanning details, television systems, etc., can solve the problems of non-uniform sensitivity, modulation of readout circuits, and actualization of problems thereby caused, and achieve the effect of easy miniaturization of pixel siz

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032]Embodiments of the present invention will be described in detail referring to the drawings. In the drawings shown below, the same parts will be denoted by the same numerals or characters, and repetitive description thereof will be omitted. The drawings are schematic, and the relation between thickness and planar dimensions, the thickness ratio of each layer, and the like are different from actual ones. Furthermore, some drawings contain parts having relations or ratios different from those in other drawings.

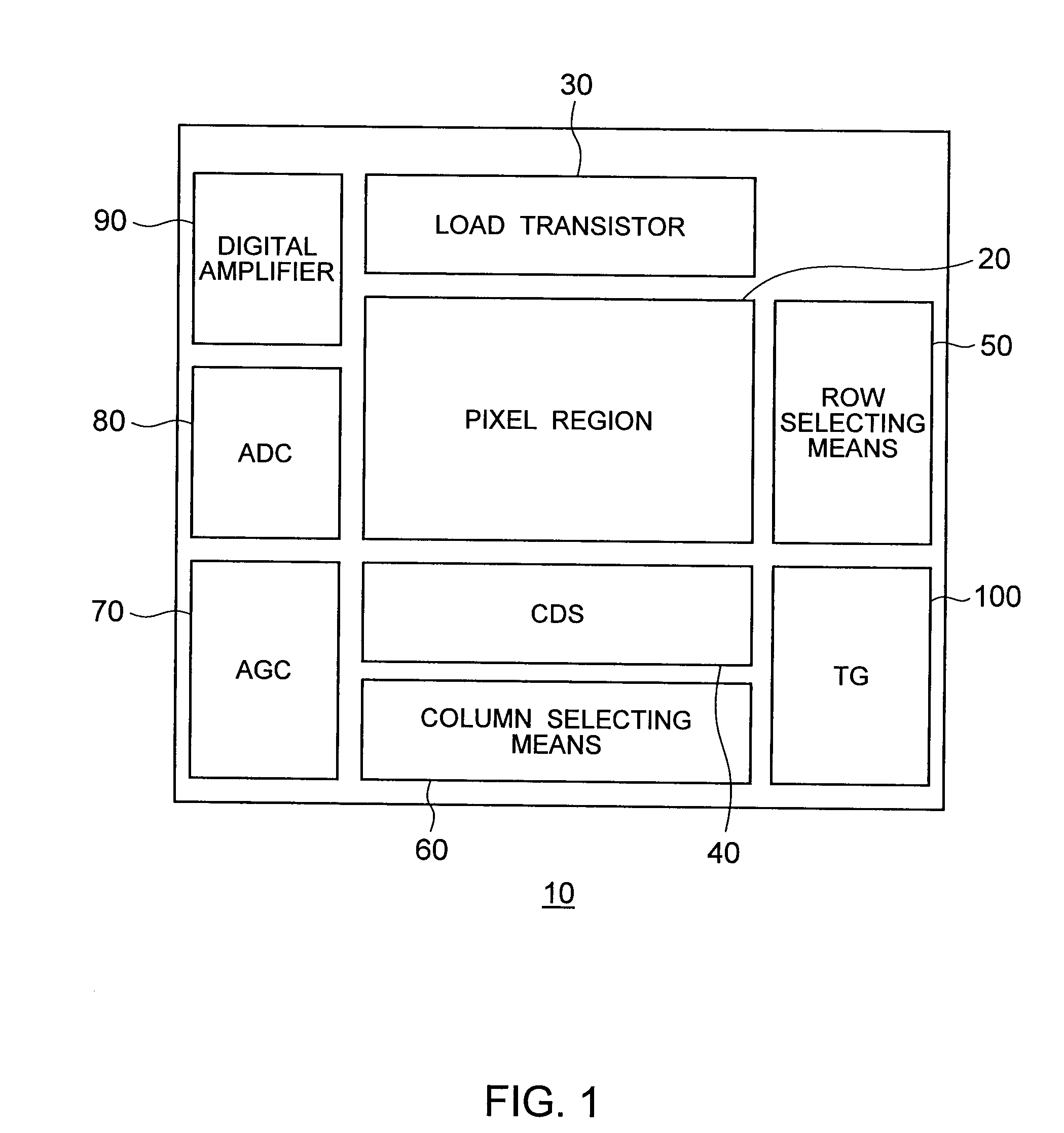

[0033]FIG. 1 is a block diagram for illustrating the schematic configuration of a solid-state imager 10 according to an embodiment of the present invention.

[0034]The solid-state imager 10 is formed by arranging a load transistor 30, a CDS (correlation double sampling) circuit section 40, row selection means 50, column selection means 60, an AGC (automatic gain control circuit) 70, an ADC (A / D converter) 80, a digital amplifier 90, a TG (timing generator) circuit 100 and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More