Stable Gold Bump Solder Connections

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

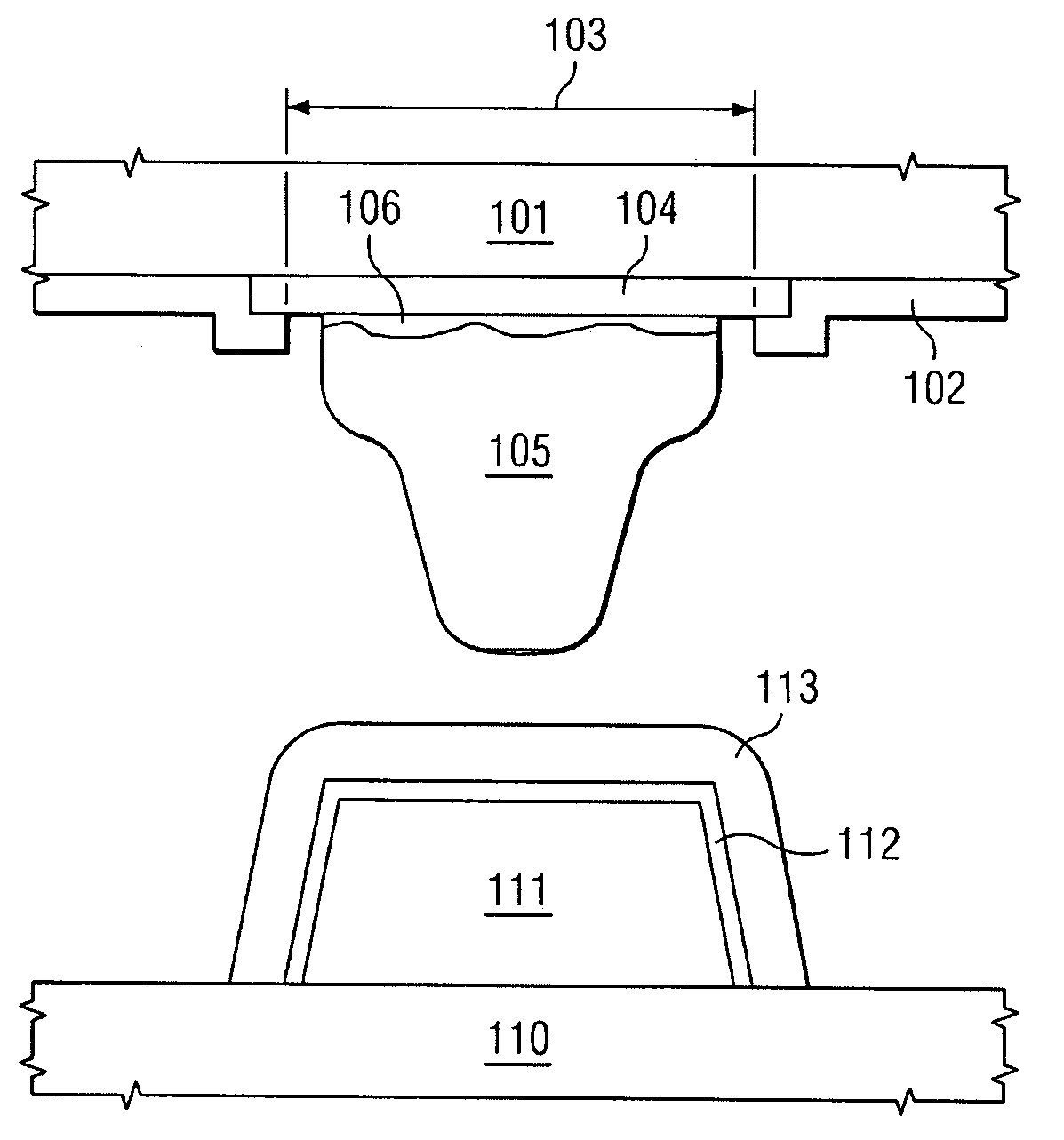

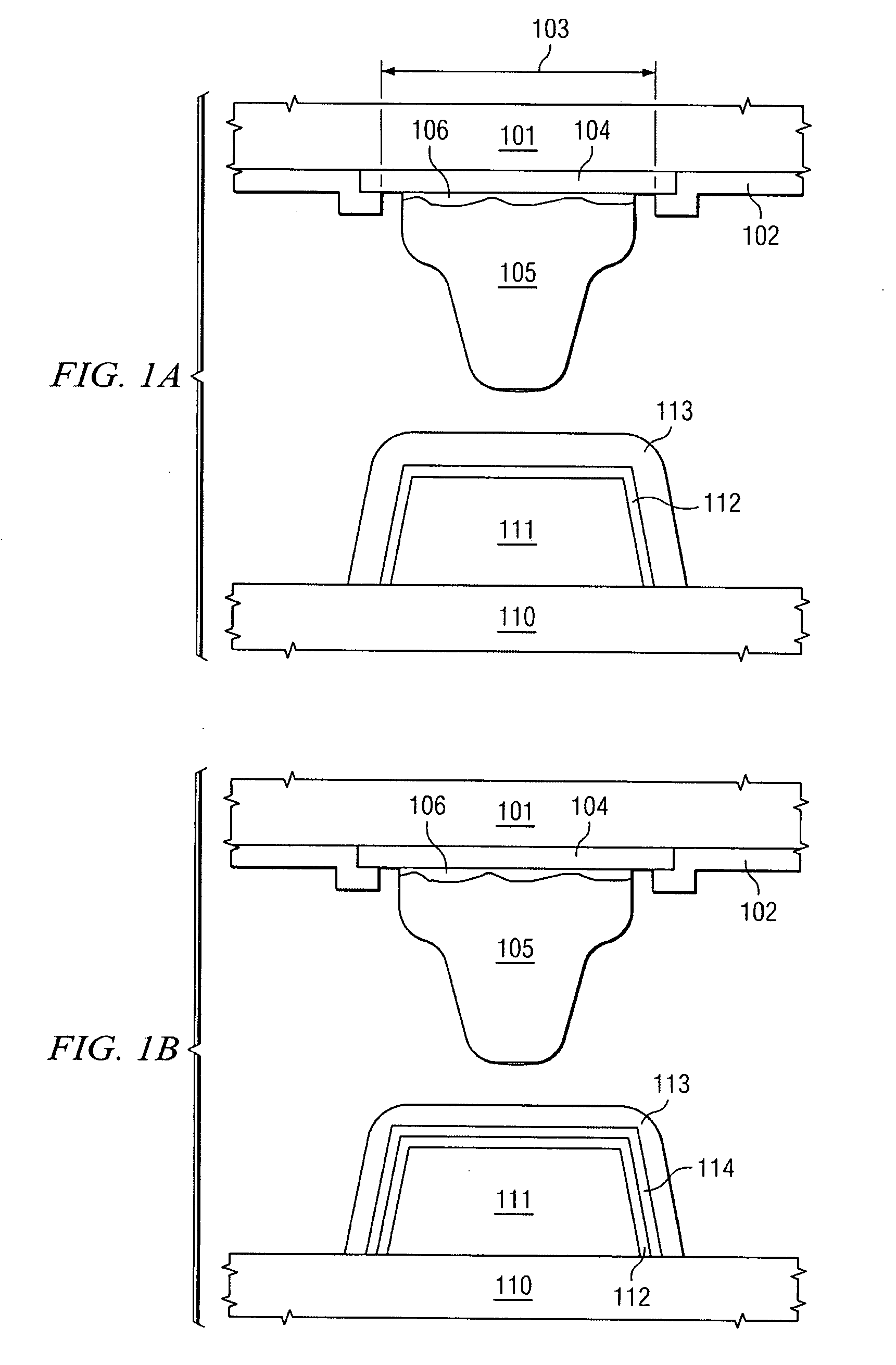

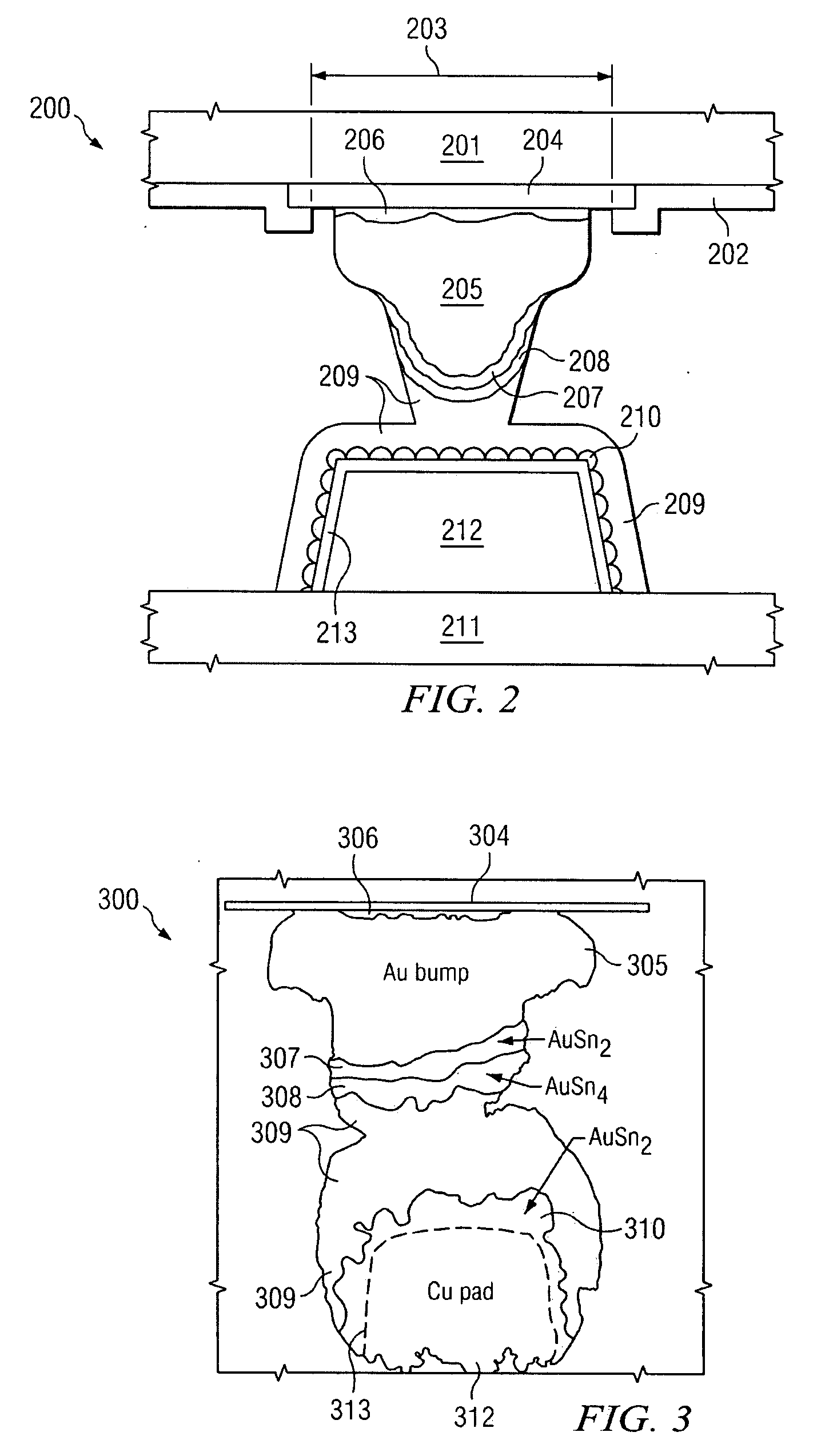

[0023]An embodiment of the invention is a metallic interconnect structure for connecting a gold bump and a copper pad. FIGS. 1A and 1B show the gold bump and the copper pad before forming the interconnect structure. In FIG. 1A, a portion of a semiconductor chip 101 has an insulating overcoat 102 (for example, silicon nitride or oxynitride) with a window 103 in the overcoat. The window exposes a portion of chip metallization 104, which is preferably aluminum or aluminum alloy with a surface bondable to gold. Alternatively, metallization 104 may be made of copper; again, the surface of pad 104 needs to be bondable to gold. For example, the surface of pad 104 may have a thin layer of gold or palladium. The exposed metal in window 103 serves as a pad for electrical and mechanical contact to chip 101.

[0024]Attached to contact pad 104 is a stud, or bump, 105, preferably made of gold. Due to the fabrication method, bump 105 may have the shape of a deformed sphere. At the interface between ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More