Process for chemical vapor phase depositing titaniam nitride containing silicon using titanium containing organic metal material

A deposition and process technology, applied in the field of chemical vapor deposition of titanium-containing silicon nitride TiSiN diffusion barrier layer, can solve the problems of poor material compatibility, rough surface, low coverage, etc., to improve the anti-electromigration level, The effect of uniform film thickness uniformity and uniform resistance distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

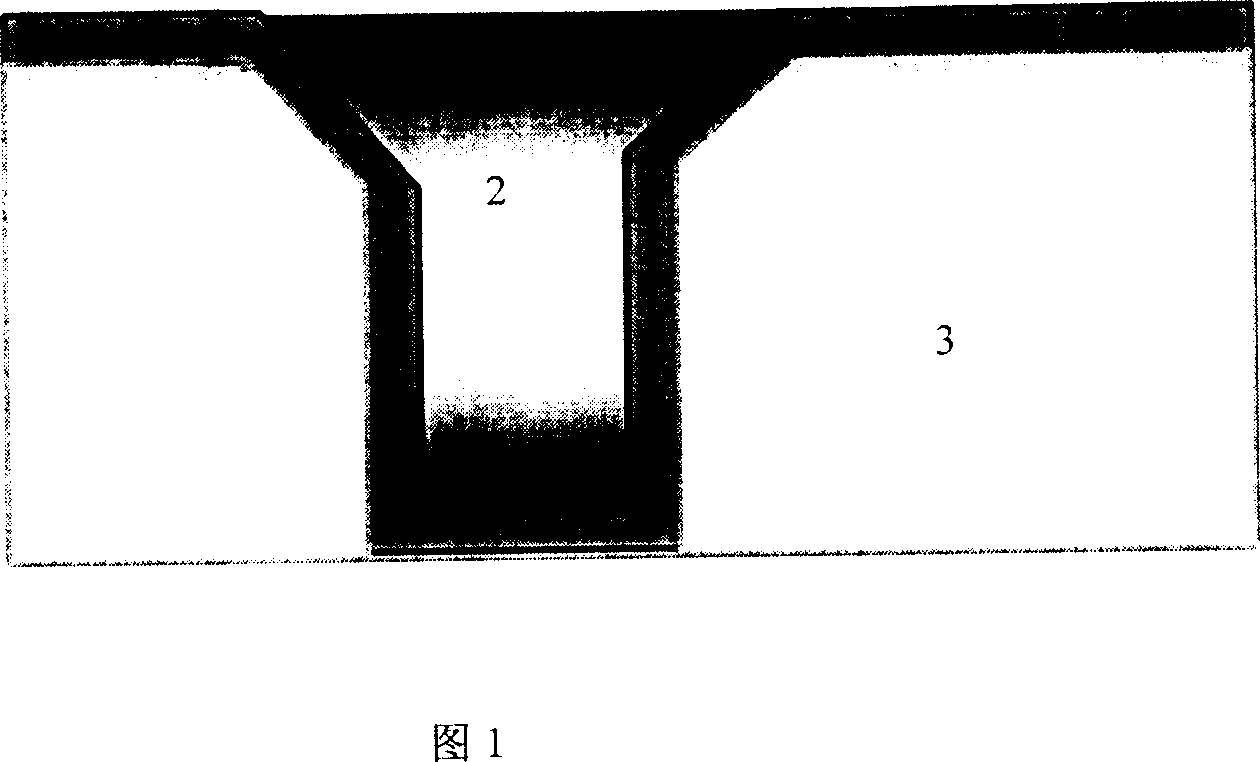

Image

Examples

Embodiment Construction

[0023] 1. Using multi-chamber CVD deposition equipment, such as Endura TxZ & HP TxZ equipment of Applied Materials, using TDMA to add methylsilane (3MS) or SiCH 4 , Chemical vapor deposition TiSiN film.

[0024] 2. First, under the condition that the vacuum is set to 5 Torr, the temperature of the silicon wafer is raised to 450°C.

[0025] 3. Next, TiSiN film was deposited by thermal decomposition with He carrying chemical substance TDMA and 5% methylsilane (3MS). At a deposition temperature of 450°C, a low vacuum of 1.5Torr, a TDMA flow rate of 225 sccm, a 3MS flow rate of 11 sccm, SiCH 4 Flow rate is 4.5 sccm, He flow rate is 275 sccm, N 2 The flow rate is 300 sccm, and the deposition time of each cycle is 15 seconds.

[0026] 4. In Situ H 2 -N 2Radio frequency plasma treatment reduces the content of impurities such as carbon, oxygen, and hydrogen in the TiSiN film deposited by CVD, reduces the resistivity, makes the TiSiN grains grow uniformly, densifies the TiSiN film...

PUM

| Property | Measurement | Unit |

|---|---|---|

| melting point | aaaaa | aaaaa |

| melting point | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More