Preparation method of NROM flash unit

A flash memory unit, N-type technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as consumption, large leakage current, and large additional power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

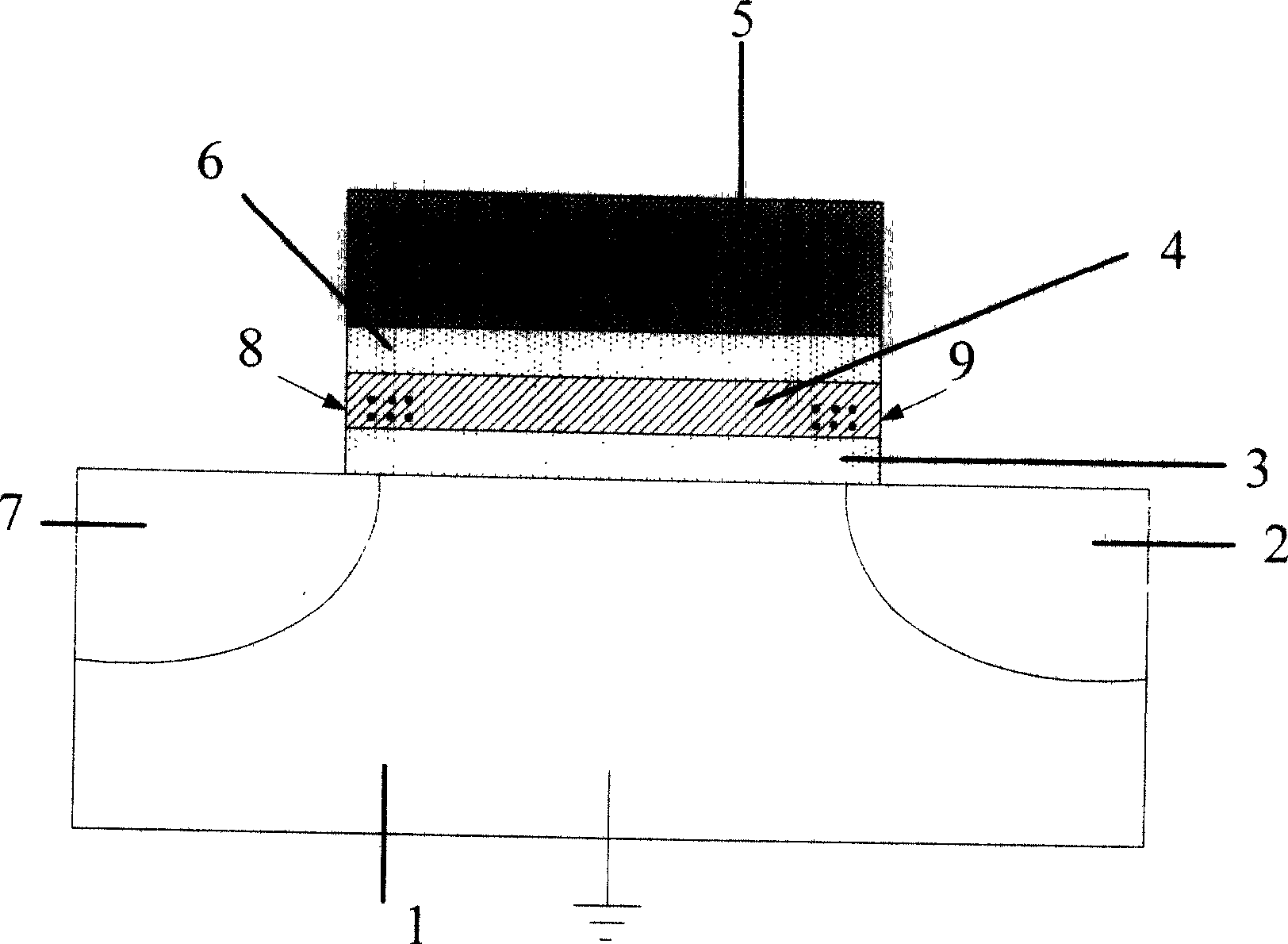

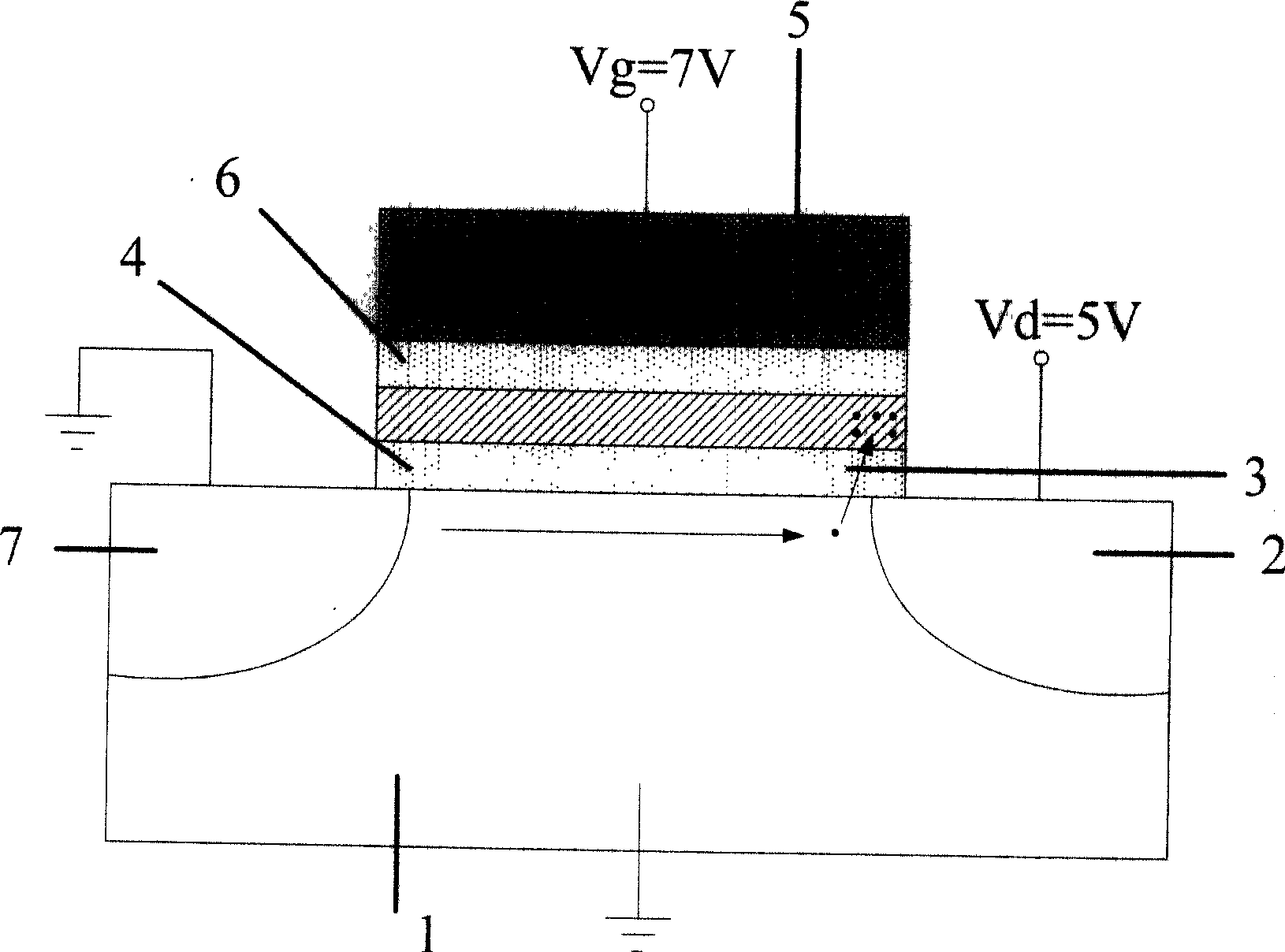

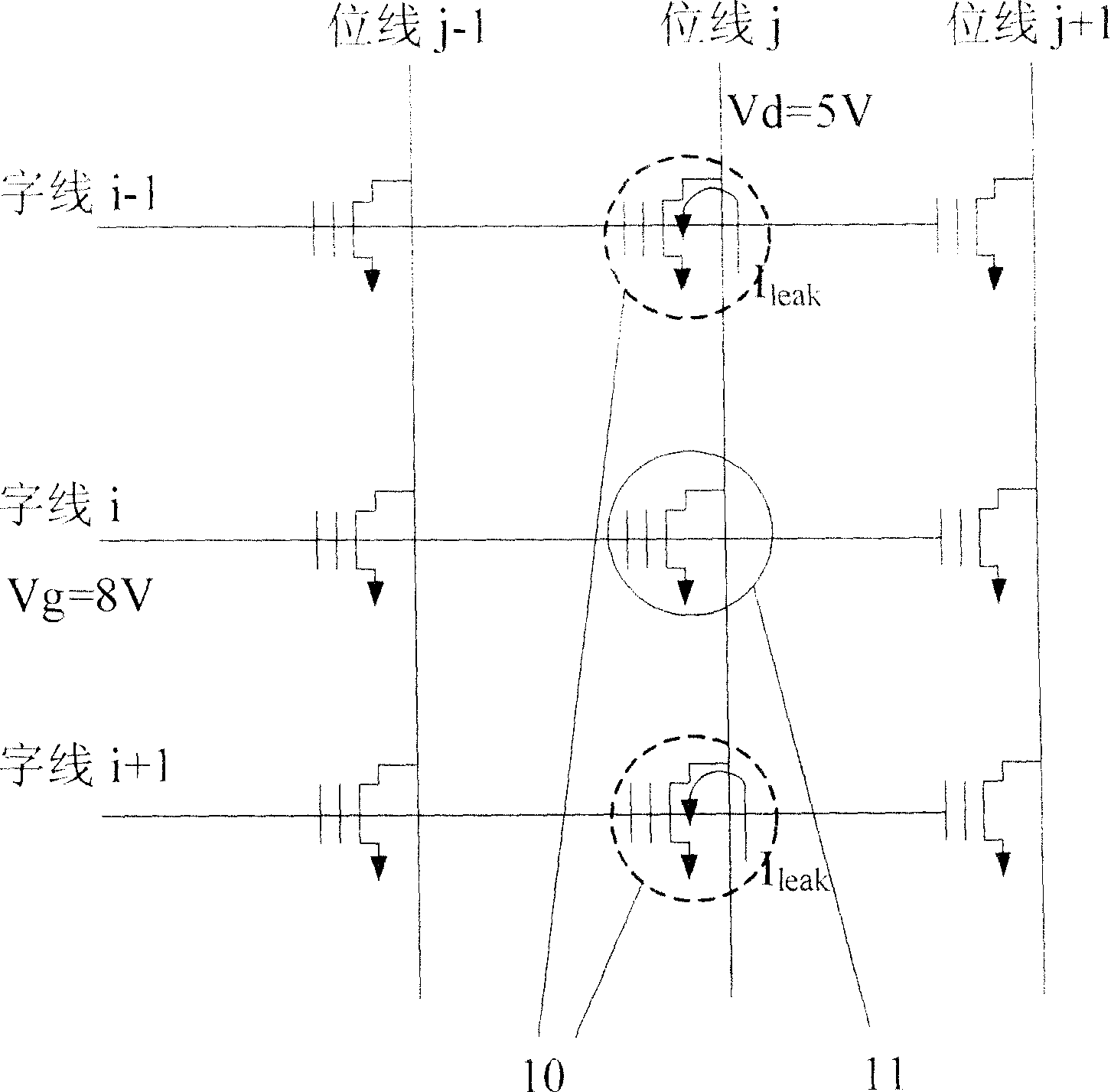

[0108] Embodiment 1: A heterogeneous gate NROM flash memory cell

[0109] Such as Figure 4 As shown, in the flash memory cell of this embodiment, the silicon substrate 1 is p-type, the drain terminal 2 and the source terminal 7 are both N+ doped, and the gate stack adopts a tunnel oxide layer 3 / silicon nitride layer 4 / The structure of the oxide layer 6 is prevented. The control gate is divided into three regions, the middle region is P+ doped polysilicon 12 which is a high work function material, and both sides near the source and drain terminals are N+ type doped polysilicon 5 which is a low work function material. In this embodiment, near The lateral size ratio of N+ doped polysilicon at the source end and P+ doped polysilicon in the middle and N+ doped polysilicon near the drain end is 1:3:1.

[0110] A method for preparing the hetero-gate NROM flash memory is shown in FIG. 5, and the method is described in detail below:

[0111] (1) Using p-type single-polishing silicon subst...

Embodiment 2

[0116] Embodiment 2: a heterogeneous gate NROM flash memory cell

[0117] The flash memory cell of this embodiment is composed of a polysilicon control gate, source and drain regions, a tunneling oxide layer, a silicon nitride layer for storing data, and a blocking oxide layer. Different areas of the control gate are injected with different types of impurities, close to the control of the source and drain The gate is implanted with N-type impurities to form an N+ polysilicon control gate, and the middle control gate is injected with P-type impurities to form a P+ polysilicon control gate. A silicon oxide layer is separated between the N+ region where the N-type impurity is injected into the polysilicon control gate and the P+ area where the P-type impurity is injected into the polysilicon control gate, and a layer of nickel silicon is added to the polysilicon control gate to electrically connect the N+ polysilicon control gate and the polysilicon P+ region. .

[0118] The manufact...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More