Shallow slot preparing method

A technology of shallow trenches and trenches, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that are not conducive to device gate oxide layer thinning effect device leakage current, and achieve the effect of reducing leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

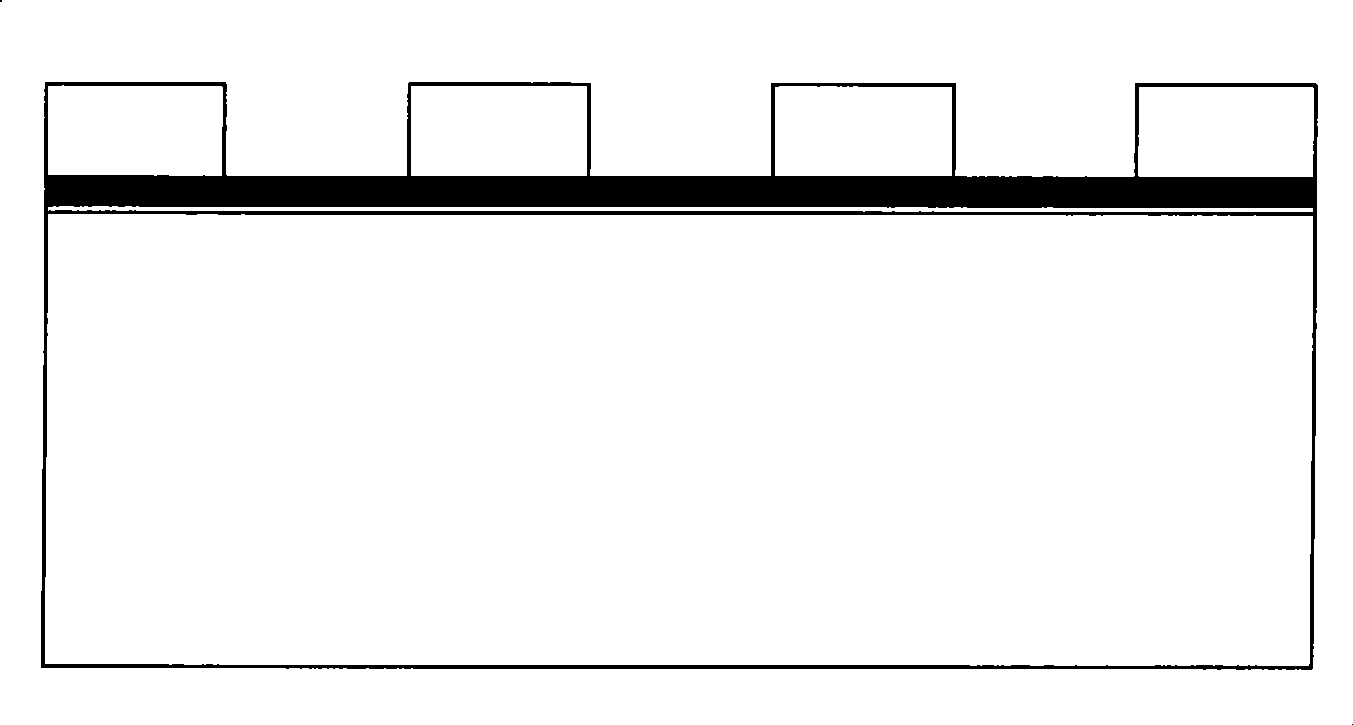

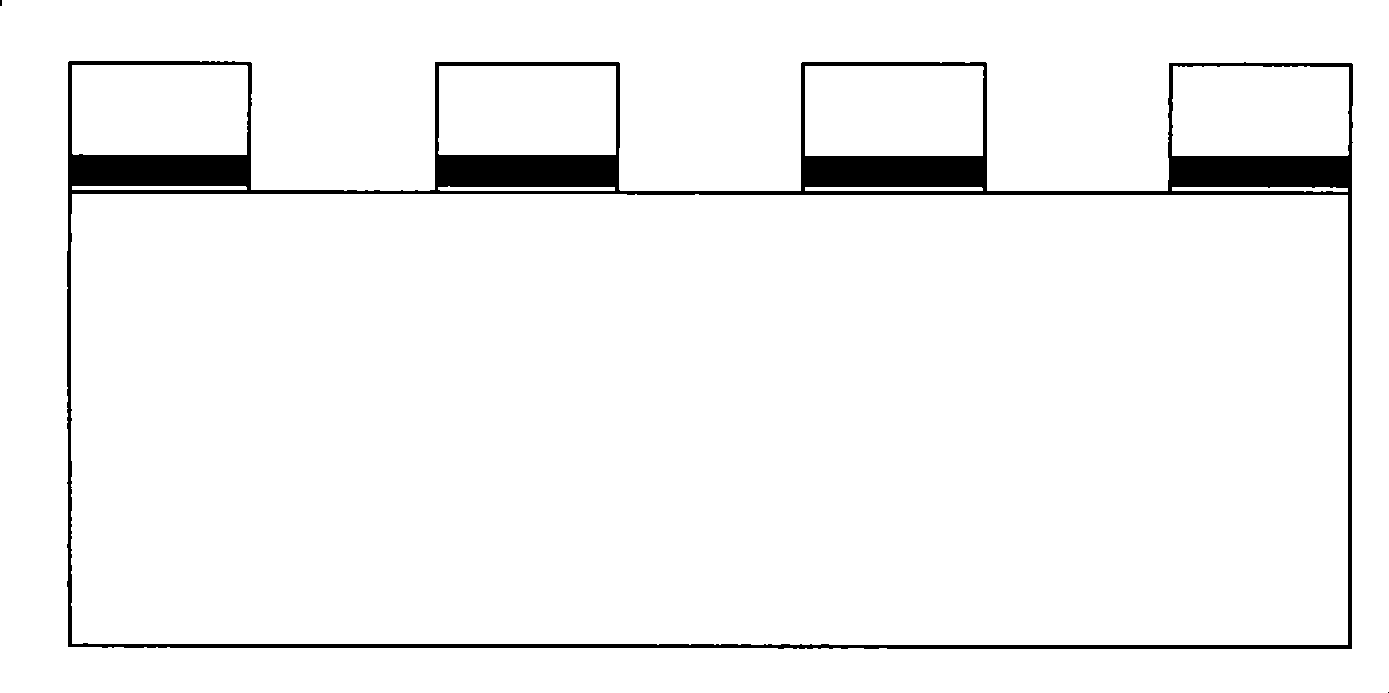

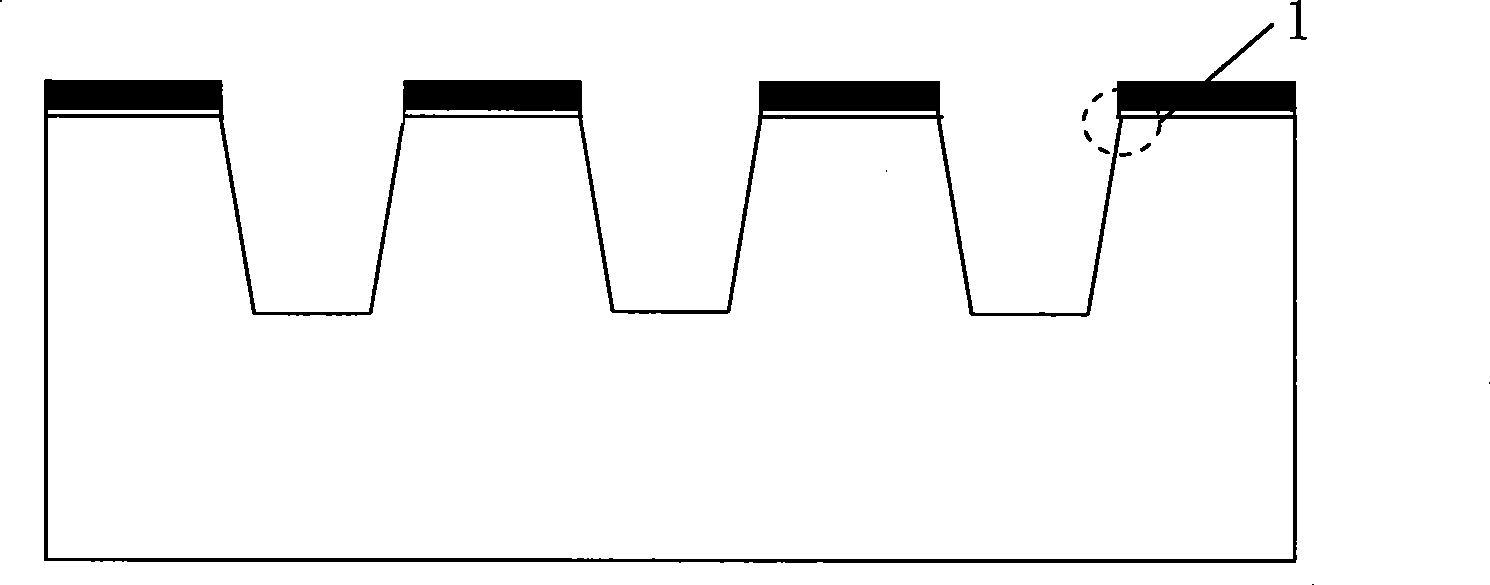

[0042] Such as Figure 16 Shown is the process flow diagram of the present invention, the shallow trench preparation method of the present invention first grows a pad oxide layer (silicon dioxide) on a substrate (silicon wafer), and deposits a hard mask layer (silicon nitride) . Next is the photoresist coating and exposure development of the active area, which will require the area (field area) outside the device to be opened (such as Figure 8 shown). Then the hard mask layer is etched, and the silicon nitride mask (hard mask) in the field area is removed and the photoresist is stripped by etching with silicon nitride plasma. Subsequent anisotropic wet etching of silicon wafers, such as Figure 9 As shown, since the anisotropic etching solution will not react with silicon nitride, the silicon surface will be etched only in the area without silicon nitride. Since the etching rate of the anisotropic etching solution is different in each crystal direction, so A slope of abou...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More