Vertical surrounding grid junction type field effect transistor, preparation method and applications thereof

A technology of field effect transistors and surrounding gates, which is applied in the field of sensors, can solve problems such as increasing process complexity, and achieve the effects of good process compatibility, simple process, and good technical compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

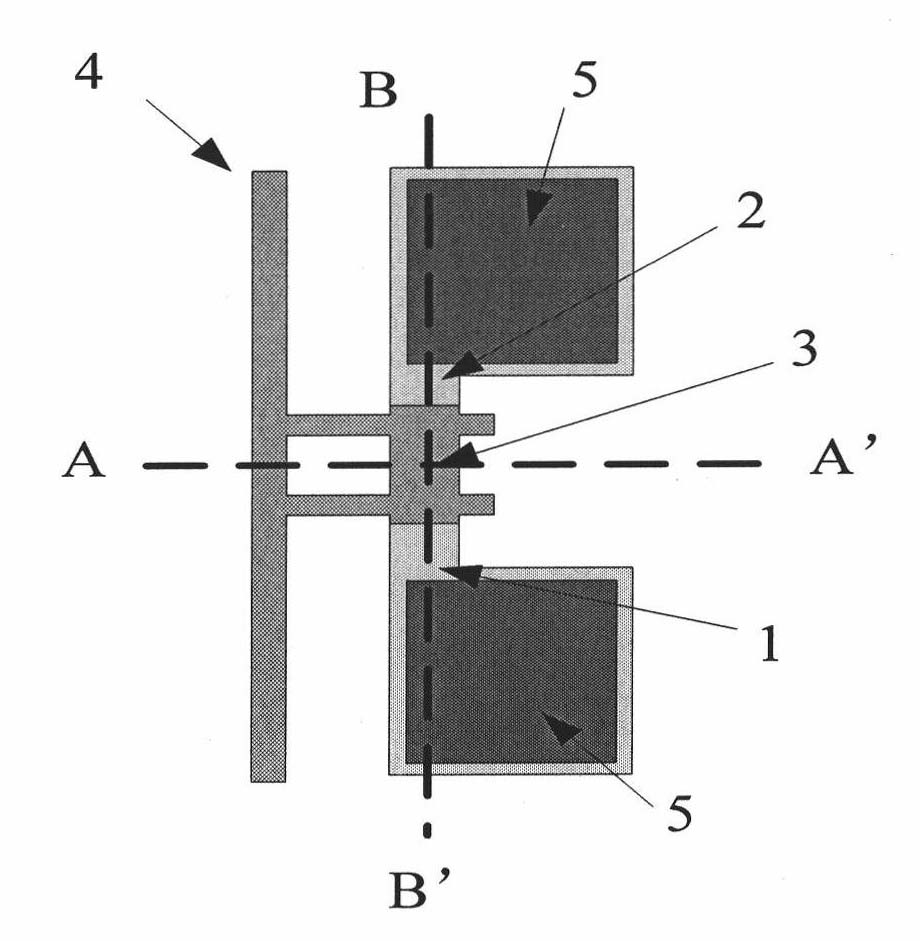

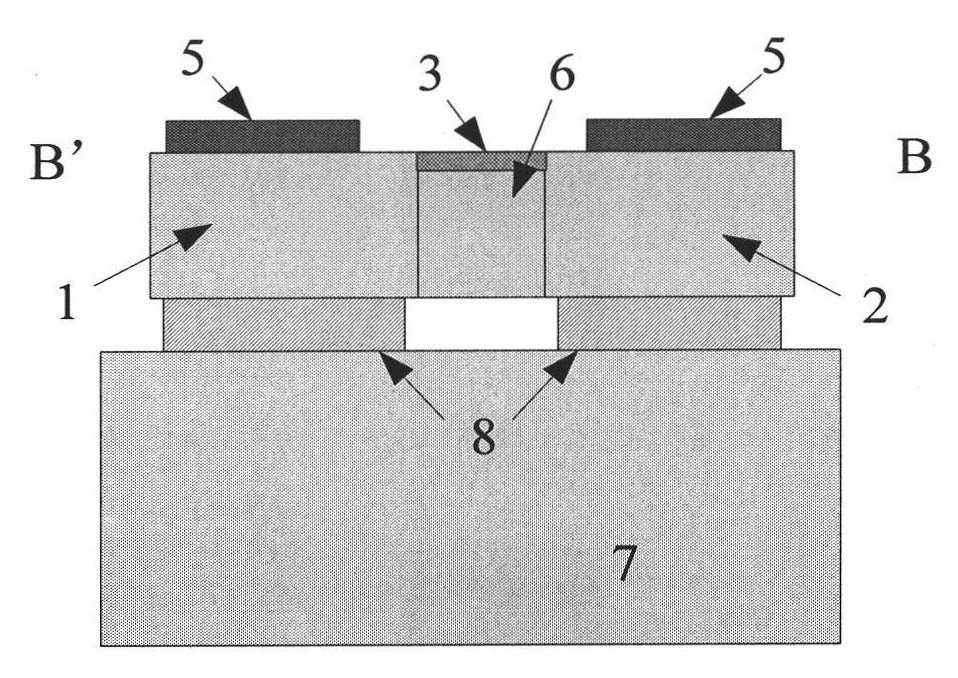

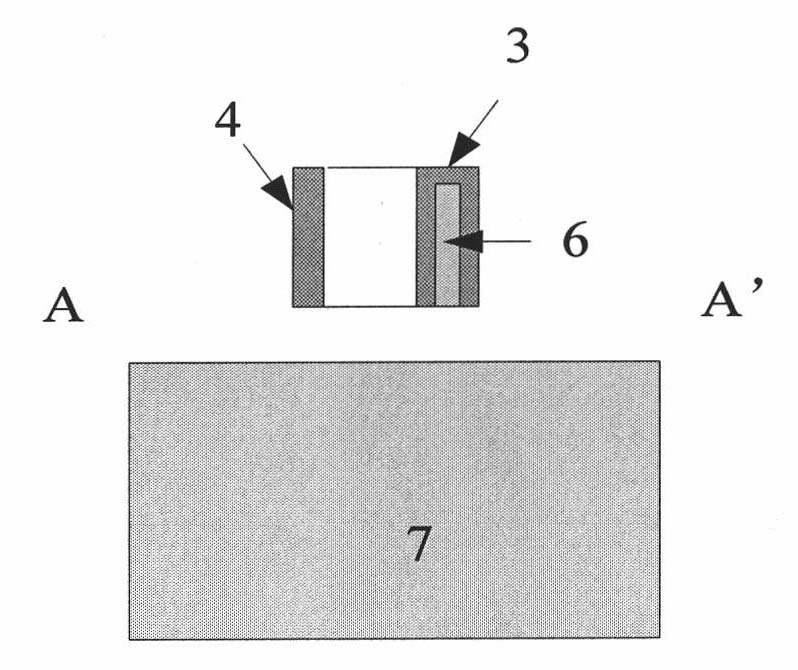

Image

Examples

Embodiment 1

[0035] The manufacturing steps of the vertical surrounding gate junction field effect transistor provided by the present invention are:

[0036] (1) For n-channel field-effect transistors, an SOI silicon wafer whose top layer silicon is n-type is used. A silicon oxide protective layer is thermally grown on top of the silicon. The sensitive structure, the sensitive gate, and the doped window surrounding the gate are etched by photolithography and dry etching process, and the oxide layer on the upper surface of the sensitive structure, the sensitive gate, and the upper surface of the surrounding gate is removed. Such as Figure 6 shown.

[0037] (2) Using the diffusion process of the integrated circuit, the upper surface and sidewall of the sensitive structure, the sensitive gate and the surrounding gate are doped. For n-channel field effect transistors, the doping type is p-type. For p-channel field effect transistors, the doping type is n-type. Doping concentrations up to...

Embodiment 2

[0042] Vertical surround-gate JFETs are offered for displacement detection of sensitive structures:

[0043] Fig. 10 shows a specific example of applying a vertical surrounding grid junction field effect transistor to a cantilever beam-mass structure acceleration sensor. In FIG. 10 , the detection of the displacement of the cantilever beam-mass structure in the plane of the silicon wafer is realized by using the vertical surrounding gate junction field effect transistor. The vertical surround gate field effect transistor can significantly reduce the influence of parasitic capacitance on displacement detection. The differential detection of the displacement of the cantilever beam-mass structure is realized by fabricating a vertical surrounding grid junction field effect transistor on both sides of the cantilever beam-mass structure. The cantilever beam-mass structure serves as the common grid of two vertically surrounding gate junction field effect transistors. The method of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More