Chip design method for multi-chip module of high-performance processor with optical interface

A high-performance processor and multi-chip component technology, applied in the field of computer engineering, can solve problems such as interference and isolation of high-power photoelectric conversion chips MCM chips, and achieve excellent signal integrity guarantee, strong anti-electromagnetic interference ability, and signal transmission characteristics. Good results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

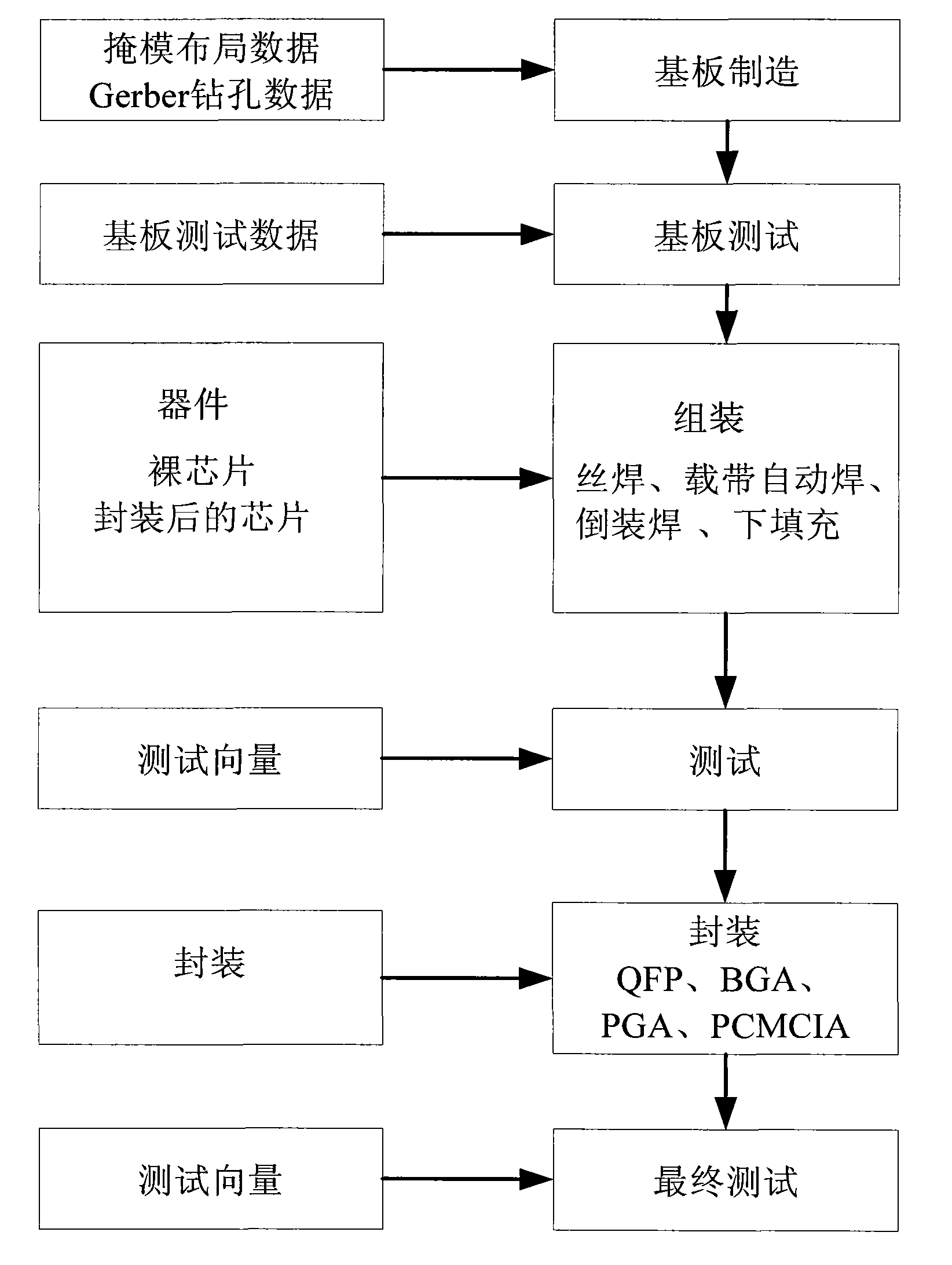

[0059] figure 1 It is the multi-chip module flow chart described in the background technology "MCM Design Manual".

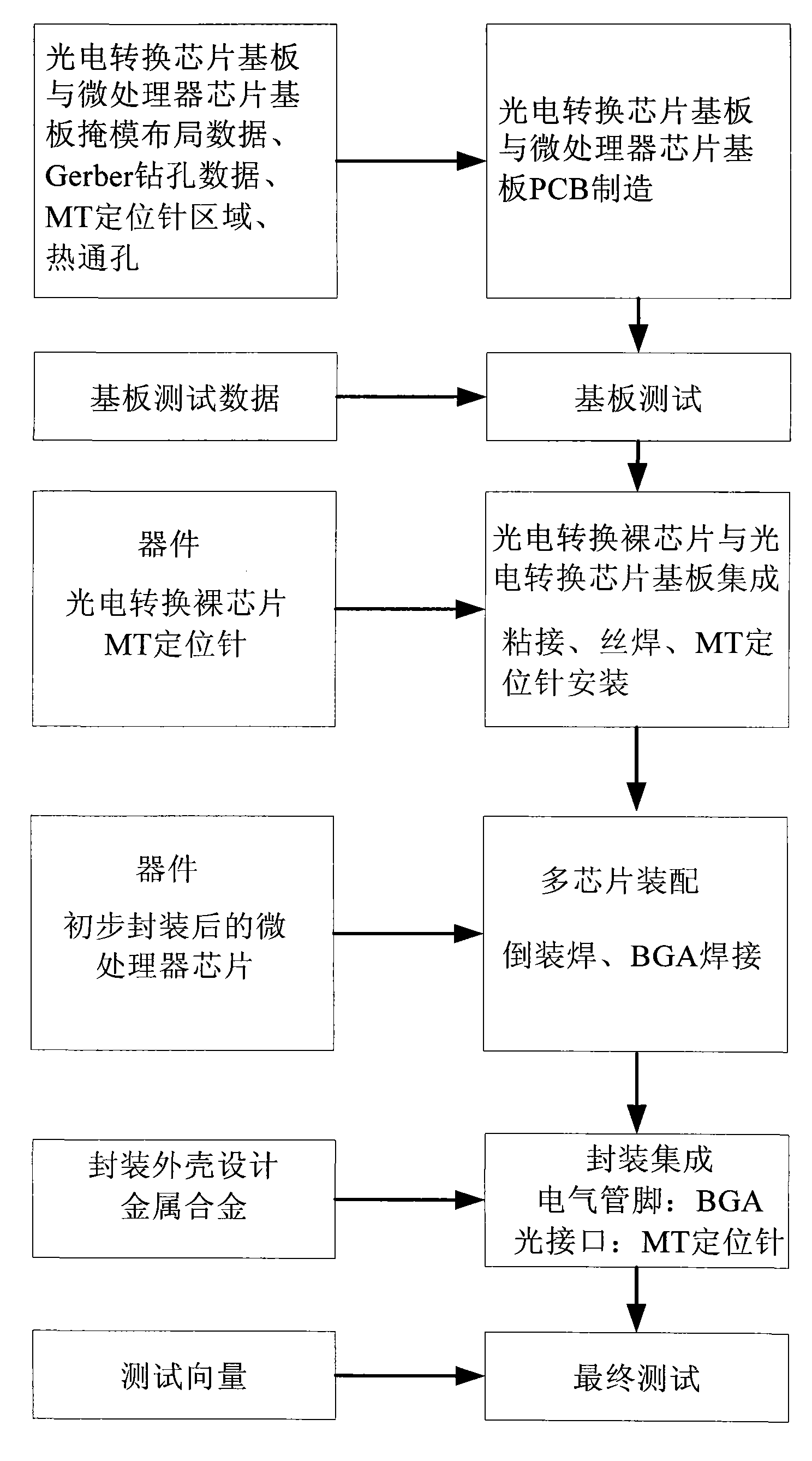

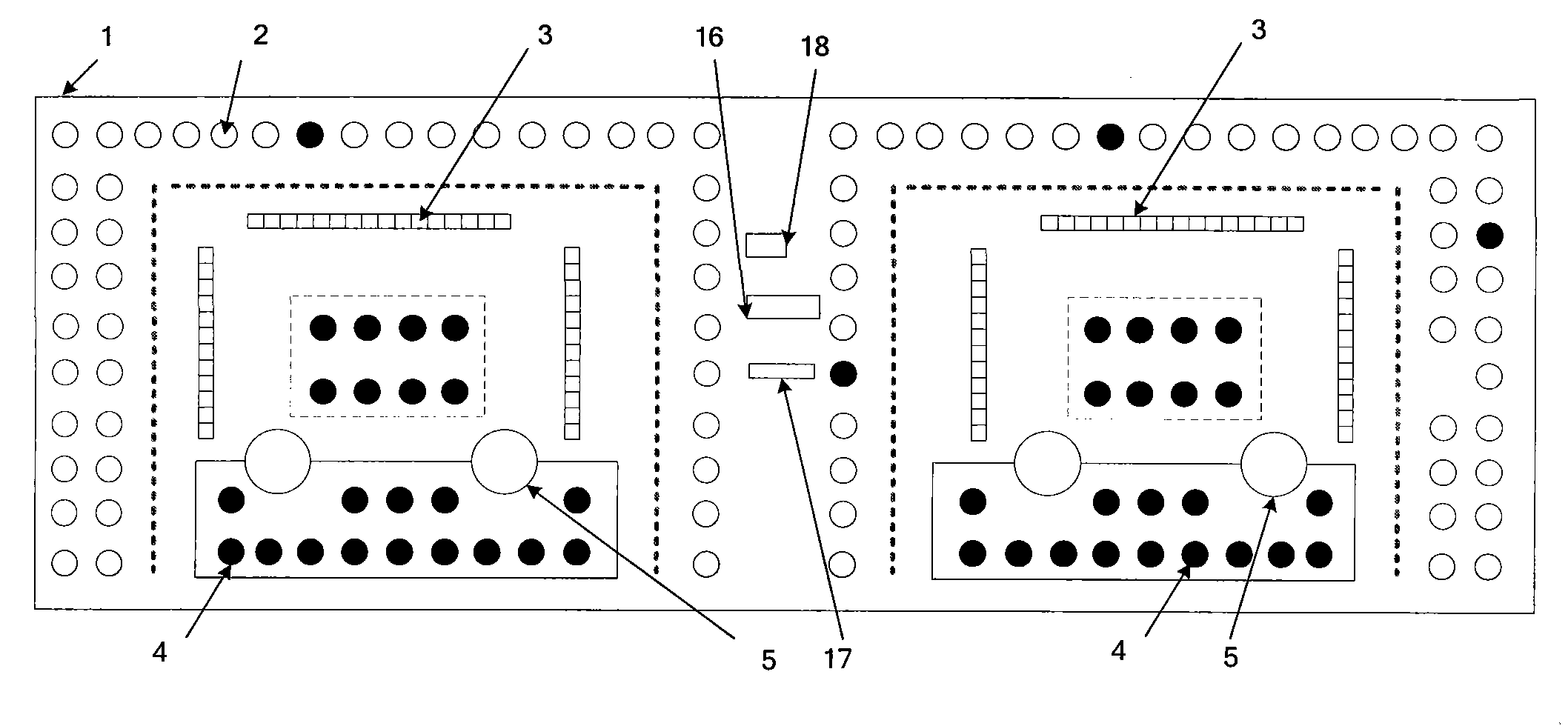

[0060] figure 2 Be the flow chart of the present invention, image 3 It is the PCB block diagram of the photoelectric conversion chip substrate, Figure 4 It is the PCB block diagram of the microprocessor chip substrate, Figure 5 It is a block diagram of a high-performance processor MCM chip with an optical interface prepared by the invention. combine image 3 , Figure 4 , Figure 5 right figure 2 Be explained:

[0061] The first step is to manufacture the photoelectric conversion chip substrate and the microprocessor chip substrate PCB, the method is:

[0062] Such as image 3 As shown, firstly, the photoelectric conversion chip substrate PCB1 is designed by using a high-speed printed circuit board. Wire bonding pads 3 , ball grid array BGA pads 2 and passive device pads are designed on the upper surface of the substrate, including resistor pads ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More