Semiconductor variable capacitor

A technology of variable capacitors and semiconductors, applied in semiconductor devices, circuits, electrical components, etc., can solve the problems of limiting the frequency modulation range of semiconductor variable capacitors, reducing the quality factor Q performance of semiconductor variable capacitors, etc., to increase width and improve frequency modulation range effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

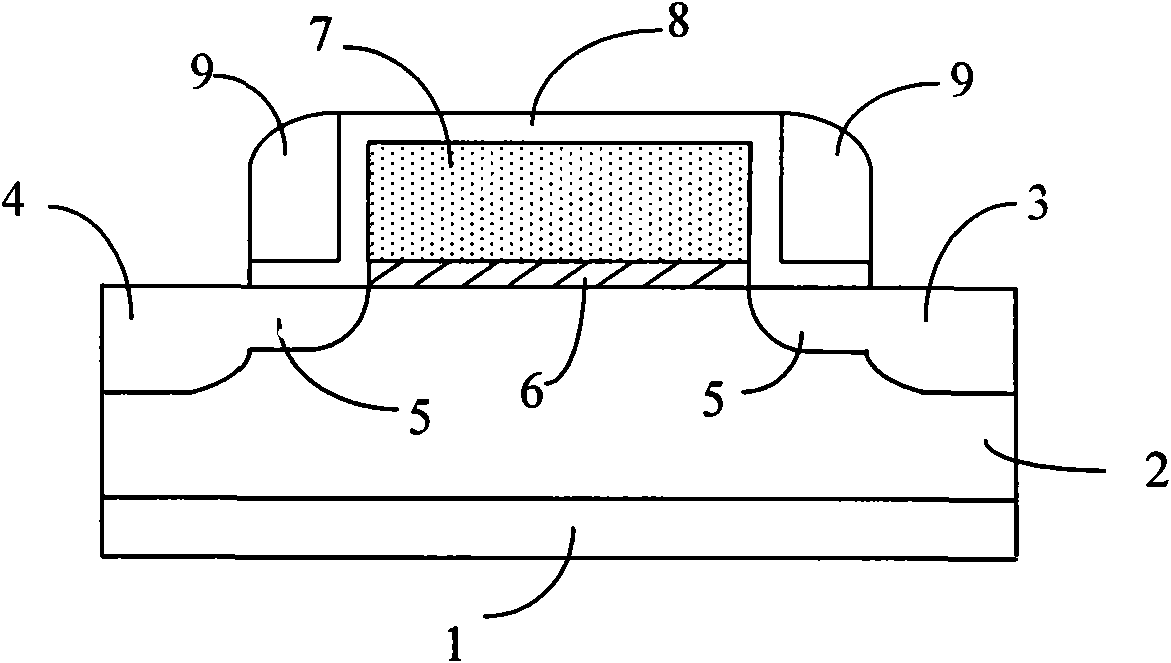

[0060] For the semiconductor variable capacitor provided in the first embodiment, please refer to figure 2 , the semiconductor variable capacitor consists of:

[0061] A semiconductor substrate 1, the semiconductor substrate can be formed by using a P-type substrate.

[0062] The N-type ion trap 2 is located on the semiconductor substrate 1, and a plurality of ion-doped regions are arranged in it, and each region is used as a source 3 or a drain 4 respectively.

[0063] The gate dielectric layer 6 is located on the ion trap 2, and the gate dielectric layer 6 is a nitride or an oxide, such as silicon nitride or silicon dioxide.

[0064] The gate 7 is located between the source 3 and the drain 4 and superimposed on the gate dielectric layer 6. The gate 7 is a polysilicon gate or a metal gate. In this embodiment, N-type polysilicon is selected. as gate 7.

[0065] The insulating layer 8 is located on the upper surface of the N-type ion trap 2 , the sidewall formed by stacking...

Embodiment 2

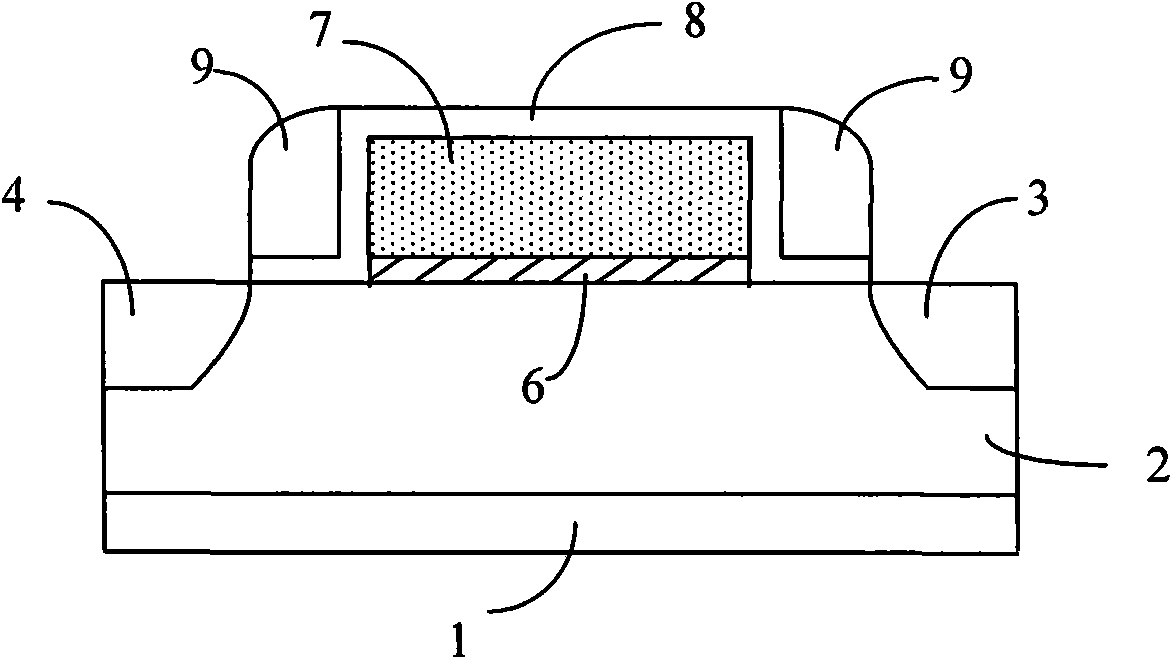

[0073] see figure 2 , the semiconductor variable capacitor consists of:

[0074] A semiconductor substrate 1, the semiconductor substrate can be formed by using a P-type substrate.

[0075] The P-type ion trap 2 is located on the semiconductor substrate 1, and a plurality of ion-doped regions are arranged in it, and each region is used as a source 3 or a drain 4 respectively.

[0076] The gate dielectric layer 6 is located on the P-type ion trap 2, and the gate dielectric layer 6 is a nitride or an oxide, such as silicon nitride or silicon dioxide.

[0077] The gate 7 is located between the source 3 and the drain 4 and superimposed on the gate dielectric layer 6. The gate 7 is a polysilicon gate or a metal gate. In this embodiment, P-type polysilicon is selected. as gate 7.

[0078] The insulating layer 8 is located on the upper surface of the P-type ion trap 2 , the sidewall formed by stacking the gate dielectric layer 6 and the P-type polysilicon gate 7 , and the upper s...

Embodiment 3

[0082] see figure 2 , the semiconductor variable capacitor consists of:

[0083] A semiconductor substrate 1, the semiconductor substrate can be formed by using a P-type substrate.

[0084] The P-type ion trap 2 is located on the semiconductor substrate 1, and a plurality of ion-doped regions are arranged in it, and each region is used as a source 3 or a drain 4 respectively.

[0085] The gate dielectric layer 6 is located on the P-type ion trap 2, and the gate dielectric layer 6 is a nitride or an oxide, such as silicon nitride or silicon dioxide.

[0086] The gate 7 is located between the source 3 and the drain 4 and superimposed on the gate dielectric layer 6. The gate 7 is a polysilicon gate or a metal gate. In this embodiment, N-type polysilicon is selected. as gate 7.

[0087] The insulating layer 8 is located on the upper surface of the P-type ion trap 2 , the sidewall formed by stacking the gate dielectric layer 6 and the N-type polysilicon gate 7 , and the upper s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More