Gain cell eDRAM for programmable logic device

A technology for programming logic and devices, applied in the field of embedded dynamic random access memory, can solve the problems of low destructive readout degree, weak turn-on and turn-off degree, destructive read operation, etc., and achieve the effect of reducing the chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

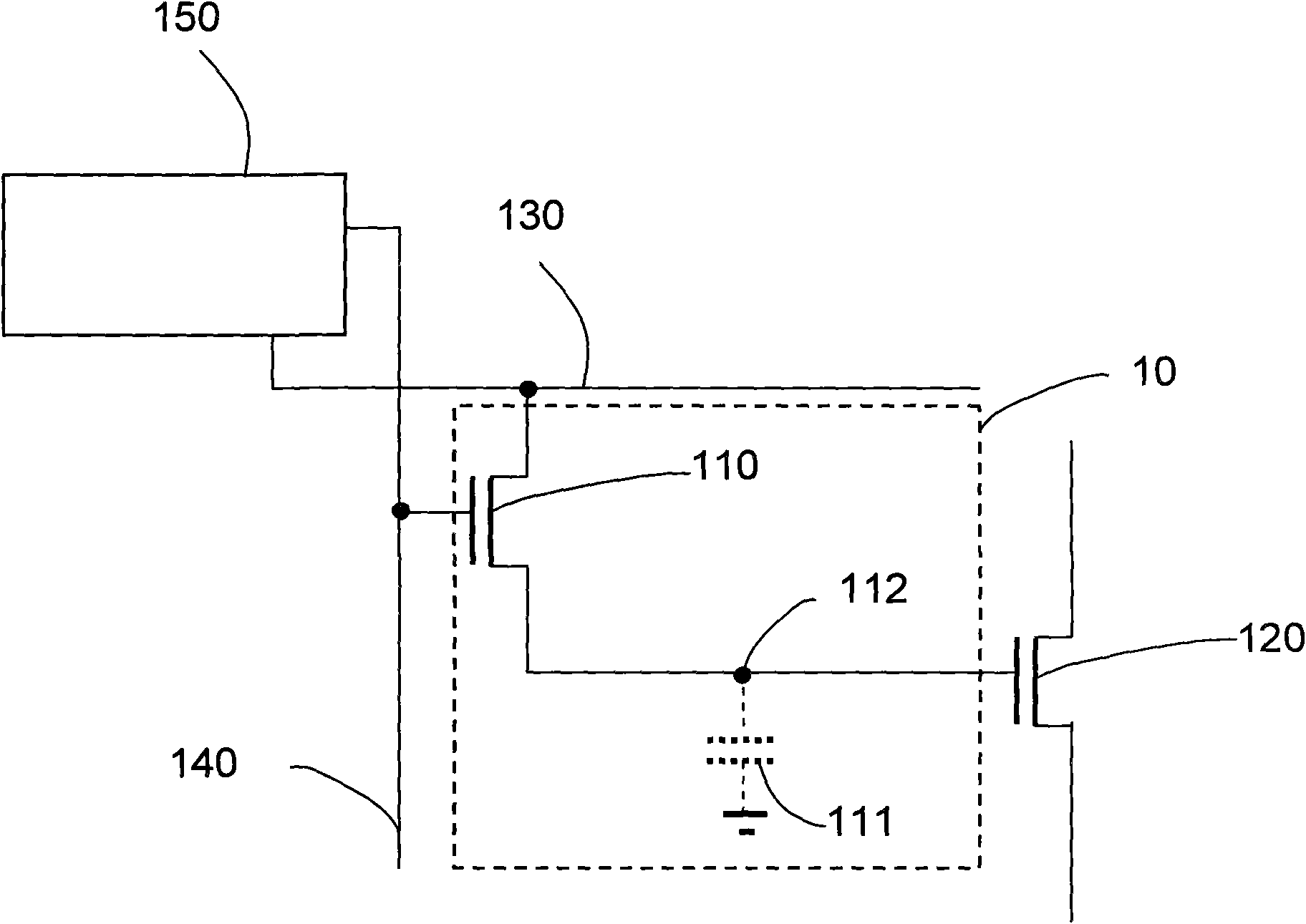

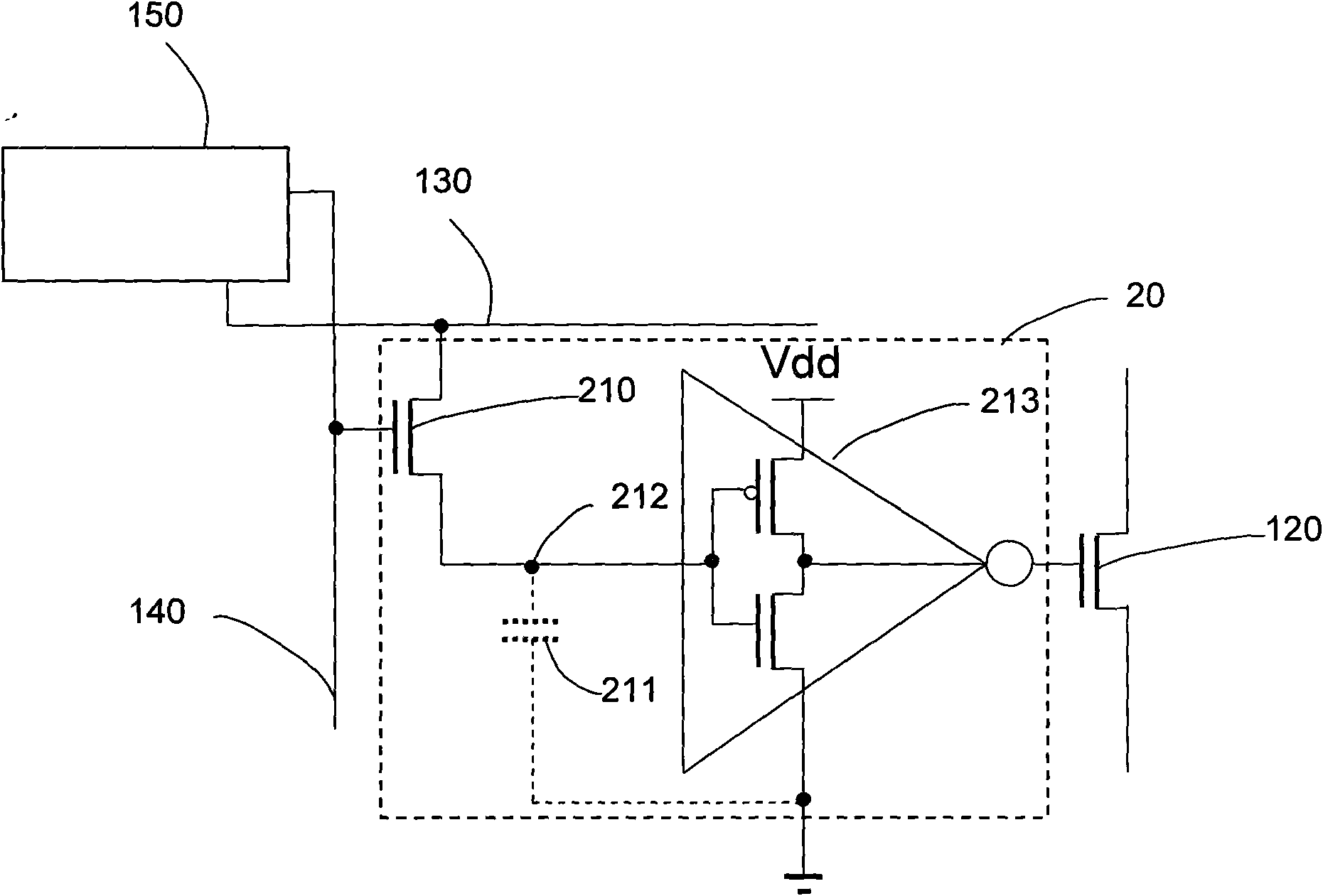

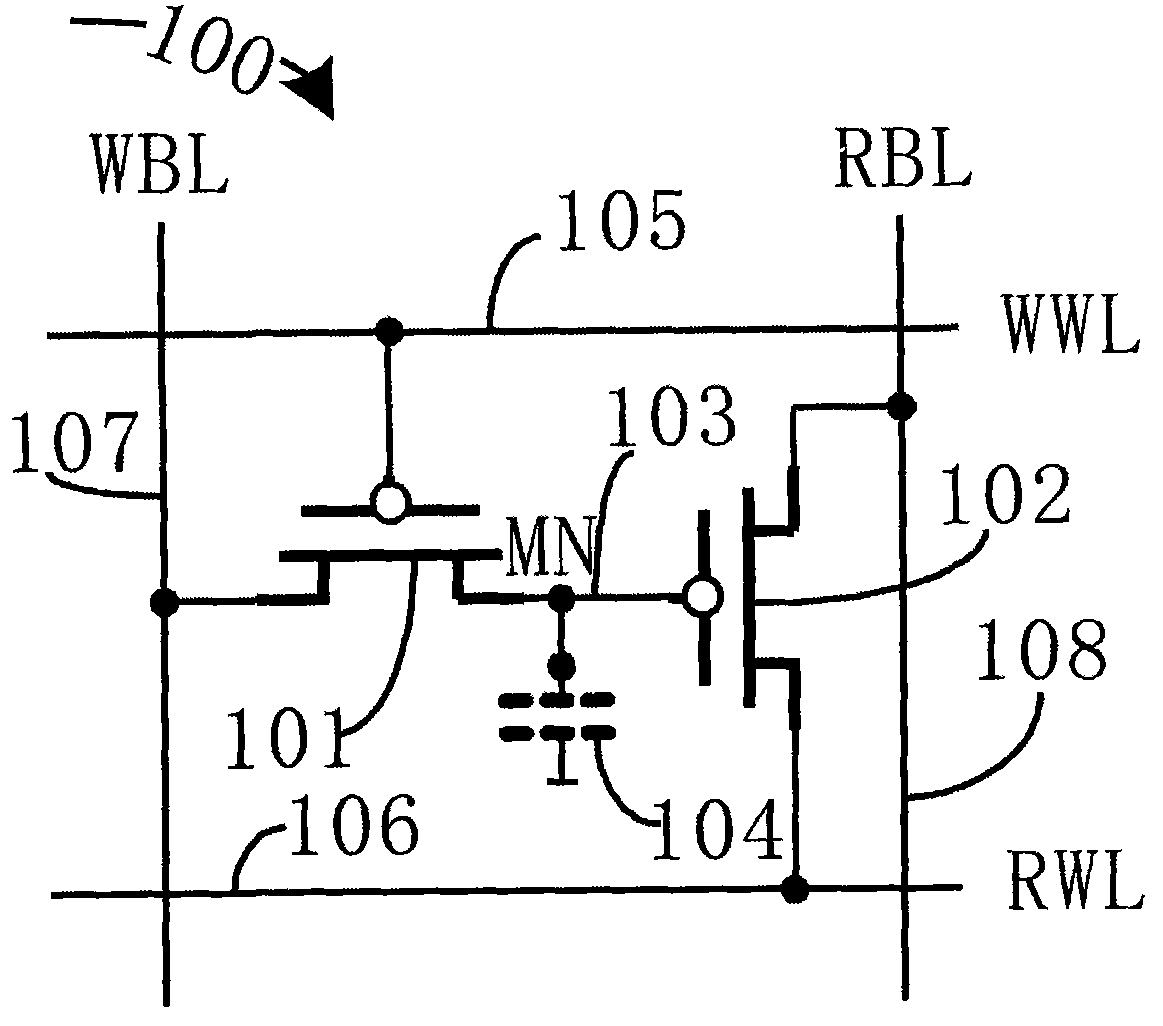

[0025] Figure 4 Shown is a schematic structural diagram of a gain unit eDRAM according to an embodiment of the present invention. In this embodiment, the gain unit eDRAM 300 is used for the configuration memory of the programmable logic device, and is used to control the on and off of the switching tube. The switching tube is one of the basic units of the programmable logic device, and its logic state reflects the programmable The programming state of the logic device. In this invention, the programmable logic device not only refers to PLD, but also includes FPGA and other programmable logic devices with basically the same principle. Such as Figure 4 As shown, the gain unit eDRAM 300 includes a write MOS transistor 301, a read MOS transistor 302, a write word...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com