Method for preparing stress-free GaN thick film on sapphire patterned substrate

A graphics substrate, sapphire technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as substrate pollution and easy cracking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

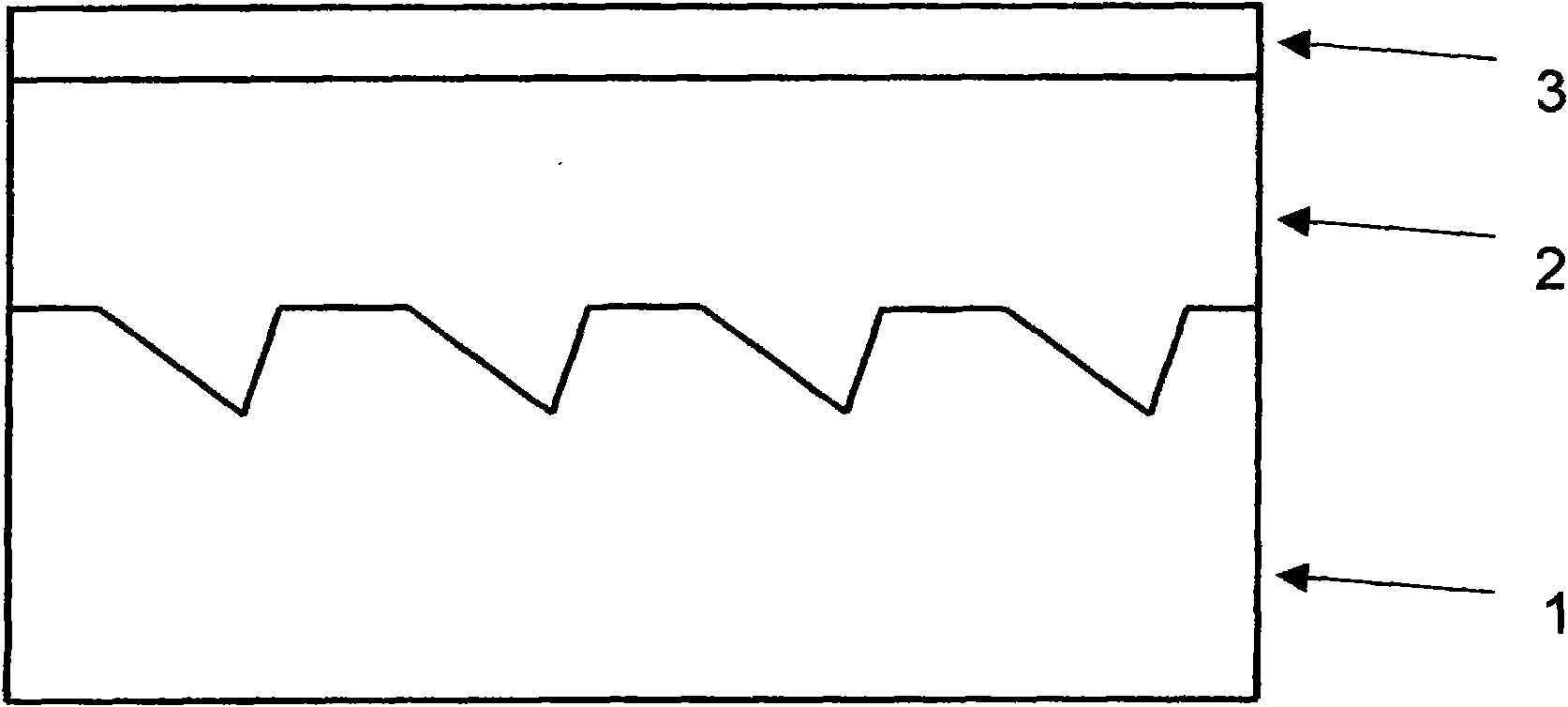

[0024] see figure 1 Shown, a kind of method of the present invention prepares stress-free GaN thick film on sapphire pattern substrate, comprises the following steps:

[0025] Step 1. Deposit a layer of silicon dioxide or silicon nitride film (not shown) on the C-face sapphire substrate; wherein the thickness of the silicon dioxide or silicon nitride film is 10 nm to 5 μm; this example uses plasma Enhanced chemical vapor deposition technology evaporates a silicon dioxide film with a thickness of 300nm on the C-plane sapphire substrate.

[0026] Step 2, using conventional photolithography techniques to photoetch striped silicon dioxide or silicon nitride mask patterns along the [11-20] direction on the C-plane sapphire substrate deposited with silicon dioxide or silicon nitride; Wherein the strip-shaped silicon dioxide or silicon nitride mask pattern is along the [11-20] direction, the strip-shaped silicon dioxide or silicon nitride mask pattern is striped, and its width is 1 ...

Embodiment 2

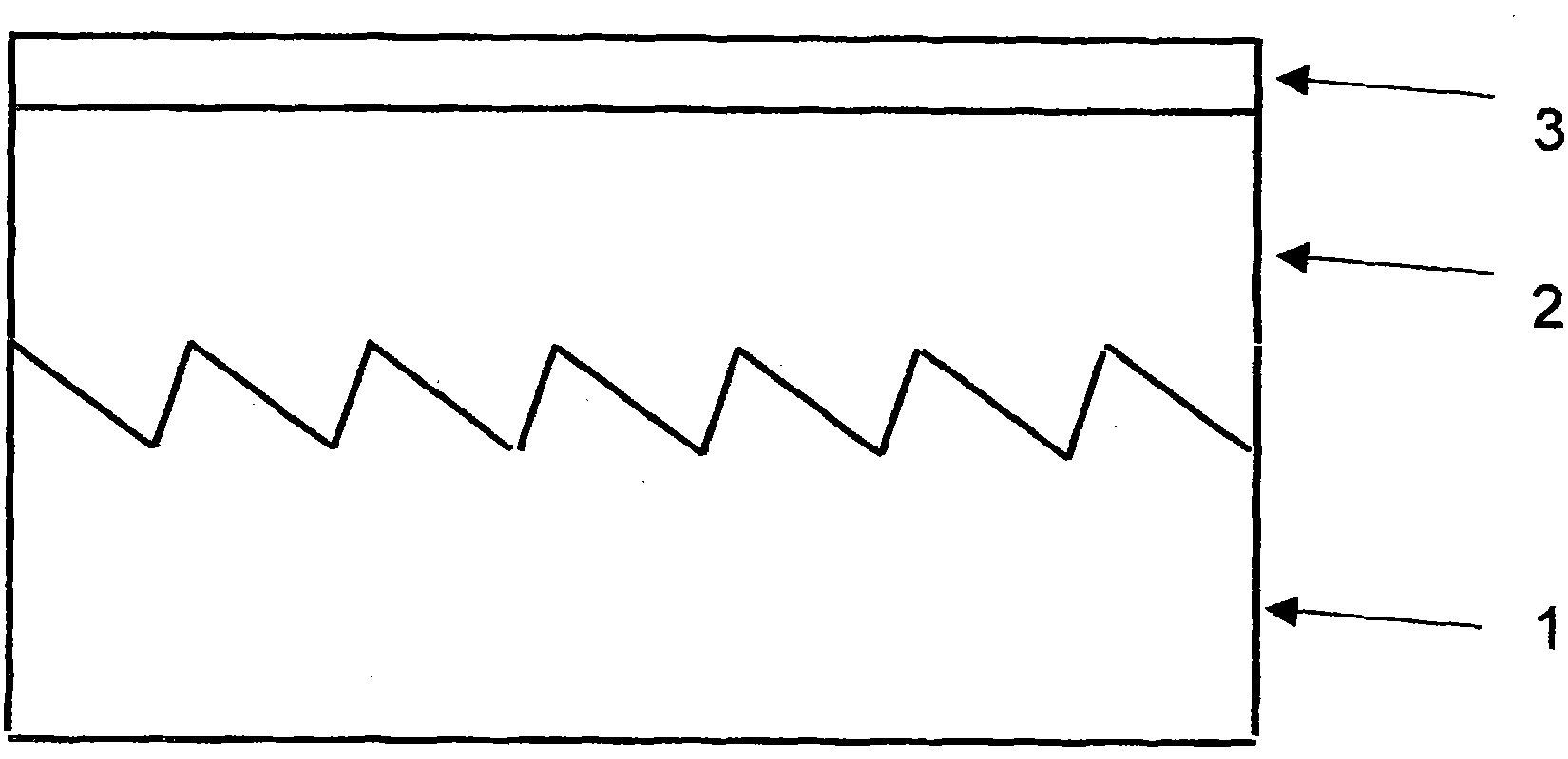

[0032] see figure 2 , present embodiment 2 is basically the same as embodiment 1, and its difference is:

[0033](1) In step 2, standard photolithography process is used to photoetch the strip-shaped silicon dioxide mask pattern along the [11-20] direction on the sapphire substrate. The photolithography process includes glue coating, exposure and etching. Standard processes such as silicon oxide and glue removal, the width of the prepared silicon dioxide mask layer stripes is 2 μm, and the width of the window area is 5 μm.

[0034] (2) After step 3 was completed, a clean sapphire pattern substrate 1 different from Example 1 was obtained. It can be seen that the corroded grooves are V-shaped, and the V-shaped grooves are regularly arranged on the substrate. Each The period is 7 μm. There is no platform between the V-shaped grooves, and the sapphire pattern substrate 1 is zigzag. The depth of the V-shaped groove is 3 μm, and the two sides are asymmetrical, the short side cor...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More