ESD (electrostatic discharge) protection circuit optimization method of RFIC (radio frequency integrated circuit) based on network S-parameter extraction

A technology of parameter extraction and optimization method, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of inaccurate equivalent method, inaccurate equivalent, non-portability of ESD protection circuit, etc., and achieve multiple parasitic effects , accurate results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

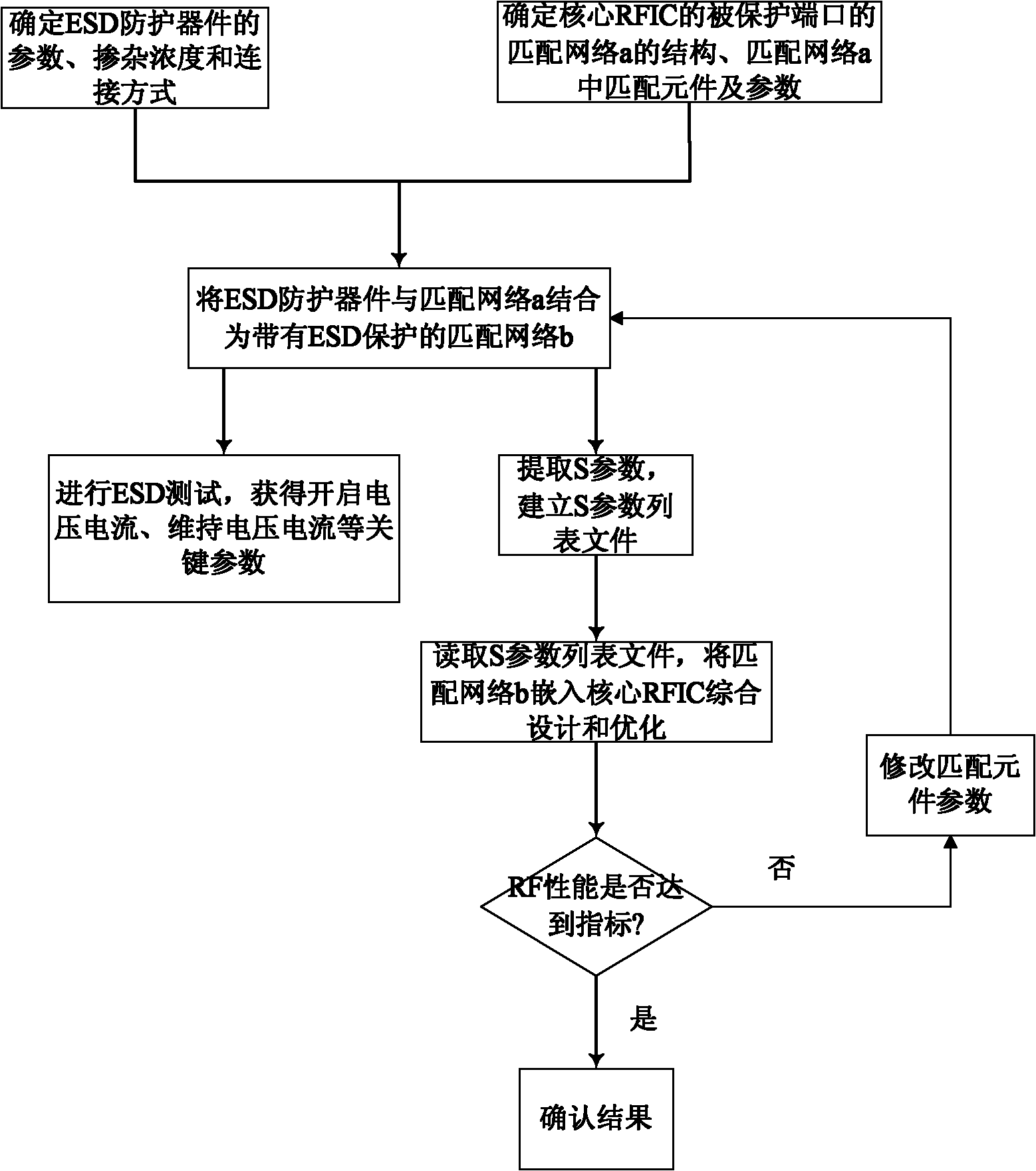

[0032] refer to image 3 , the present invention is based on the RFIC ESD protection circuit optimization of network S parameter extraction, carries out as follows:

[0033] Step 1, determine the type and structural parameters of the ESD protection device.

[0034] According to the process conditions and the type of ESD protection device used in the core RFIC design, determine the structural parameters, doping concentration and connection mode of the ESD protection device. Among them, the ESD protection device adopts any one of diode, metal-oxide-semiconductor field effect transistor MOSFET, silicon-controlled rectifier SCR and derivative devices of these devices or a combination of these devices.

[0035]For example, the core RFIC adopts TSMC 0.25μm process of TSMC, and the ESD protection device adopts a low-voltage trigger silicon-controlled rectifier LVTSCR. It is determined that the channel length of LVTSCR is 0.24μm, the gate oxide layer thickness is 3nm, the PN junction...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More