Method for manufacturing wafer-level patch panel

An adapter board and wafer-level technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as low formation efficiency, difficulty in dielectric layer deposition, and limited application range of wafer-level packaging technology. Achieve the effect of realizing large-scale production, reducing process difficulty and process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] see Figure 1~Figure 11 , Figure 1~Figure 11 It is an example diagram of the formation process of the wafer-level interposer of the present invention. Depend on Figure 1~Figure 11 It can be seen that the wafer-level adapter plate preparation method of the present invention includes the following process steps:

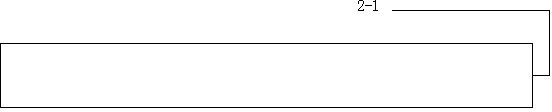

[0034] Step 1, take the carrier wafer 2-1, such as figure 1 ;

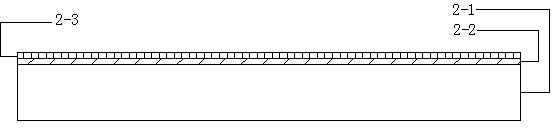

[0035] Step 2, forming a release agent 2-2 on the carrier wafer 2-1, the release agent 2-2 is usually sulfide and chromate, etc., and then sputtering or electroless plating on the release agent 2-2 Metal conductive layer 2-3, such as figure 2 , its purpose is to make conductive preparations for the next step of electroplating process;

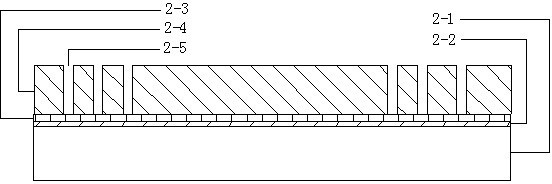

[0036] Step 3: Paste or coat the mask material 2-4 on the metal conductive layer 2-3. The mask material 2-4 adopts a thick dry film or a thick colloidal substance, and the mask material 2 is formed by photolithography or laser. Form mask pattern opening 2-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com