Method for manufacturing high-voltage lateral dual-diffusion N-channel metal oxide semiconductor (NMOS) based on standard complementary metal-oxide-semiconductor transistor (CMOS) process

A technology of lateral double-diffusion and manufacturing method, which is applied in the field of high-voltage lateral double-diffusion NMOS manufacturing. It can solve the problems of lowering the requirements of photolithographic alignment, difficult manufacturing process, and integration, and achieves short channel length and optimal current drive. and the effect of conduction capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below in conjunction with specific embodiments and accompanying drawings, but the protection scope of the present invention should not be limited thereby.

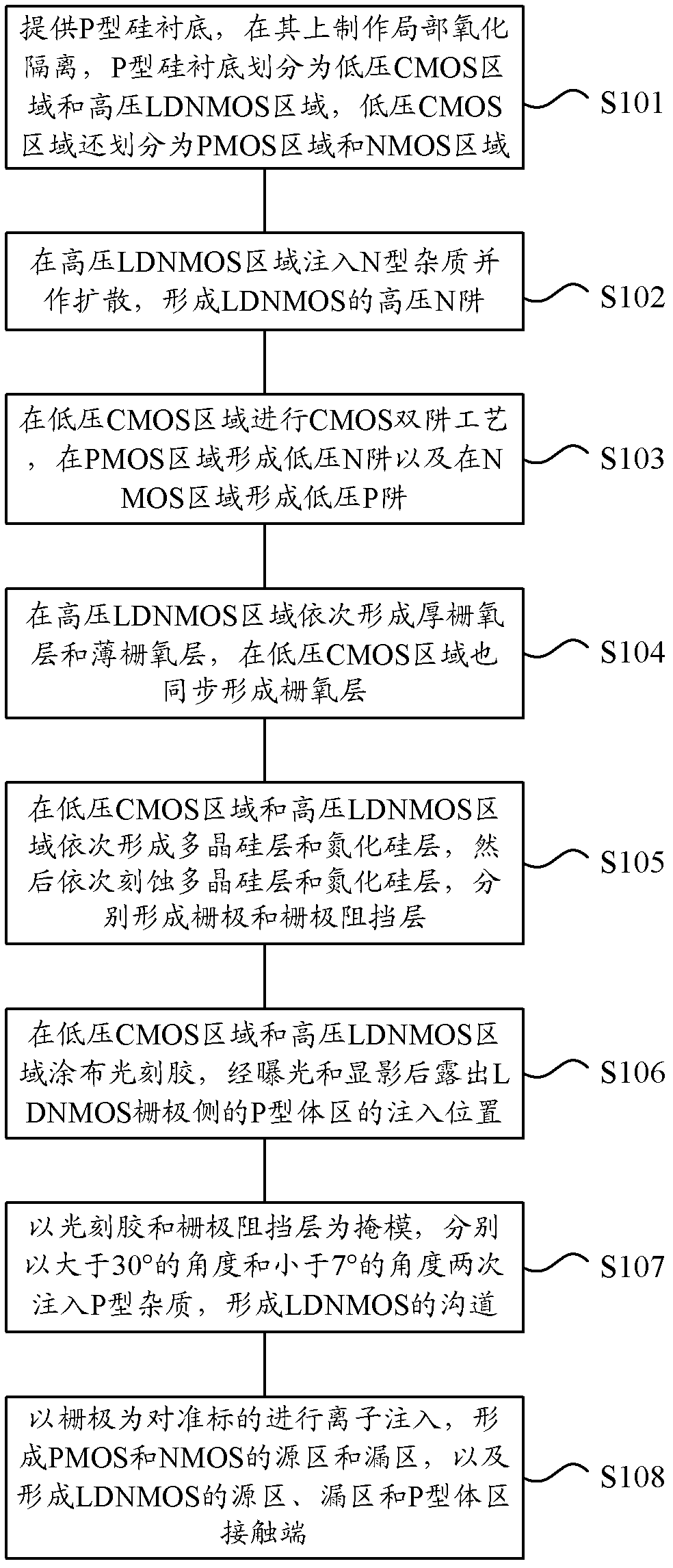

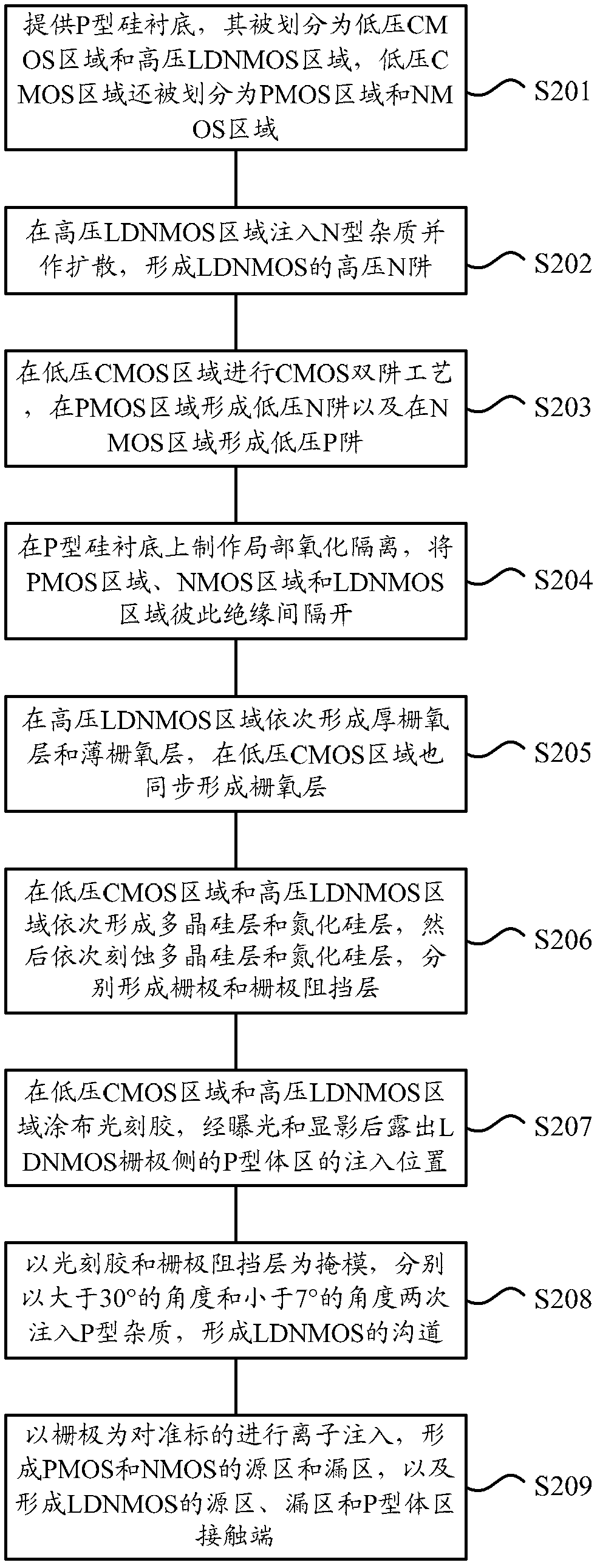

[0039] figure 1 It is a schematic flowchart of a method for fabricating a high-voltage lateral double-diffusion NMOS based on a standard CMOS process according to an embodiment of the present invention. As shown in the figure, the fabrication method of the high-voltage lateral double-diffused NMOS (LDNMOS) may include:

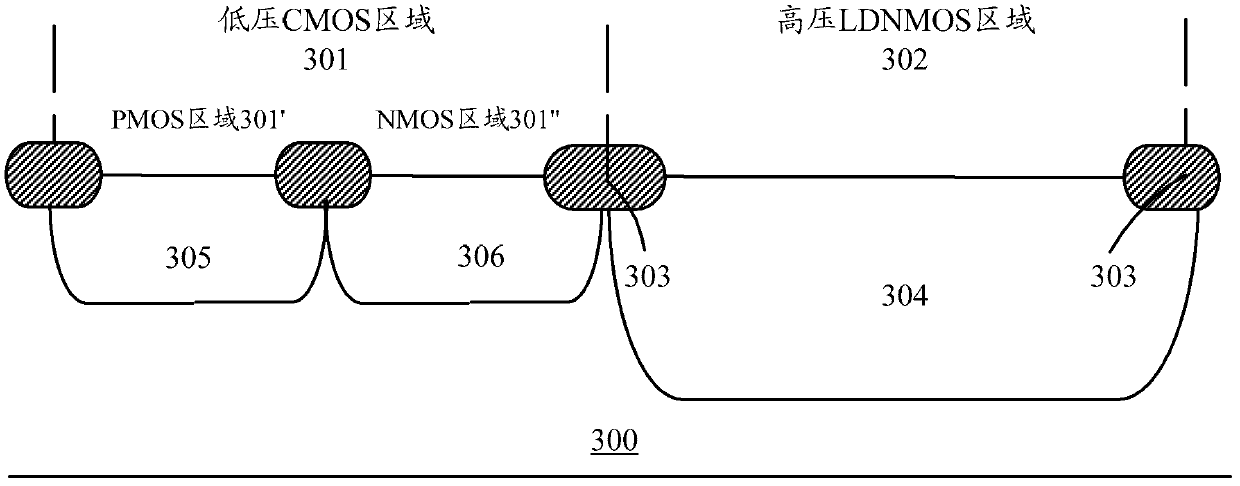

[0040] Executing step S101, providing a P-type silicon substrate on which local oxidation isolation is made, the P-type silicon substrate is divided into a low-voltage CMOS region and a high-voltage LDNMOS region, and the low-voltage CMOS region is further divided into a PMOS region and an NMOS region;

[0041] Executing step S102, implanting and diffusing N-type impurities in the high-voltage LDNMOS region to form a high-voltage N well of the LDNMOS;...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More