Buried Mask Wet Etching Process of Silicon Micromechanical Structure

A technology of wet etching and silicon micromechanics, applied in the direction of microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve the problems of inability to complete the precise transfer of graphics, easy to damage the film structure, and affect the accuracy of lithography, etc., to achieve Avoid the effects of inaccurate transfer, low process equipment requirements, and product cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

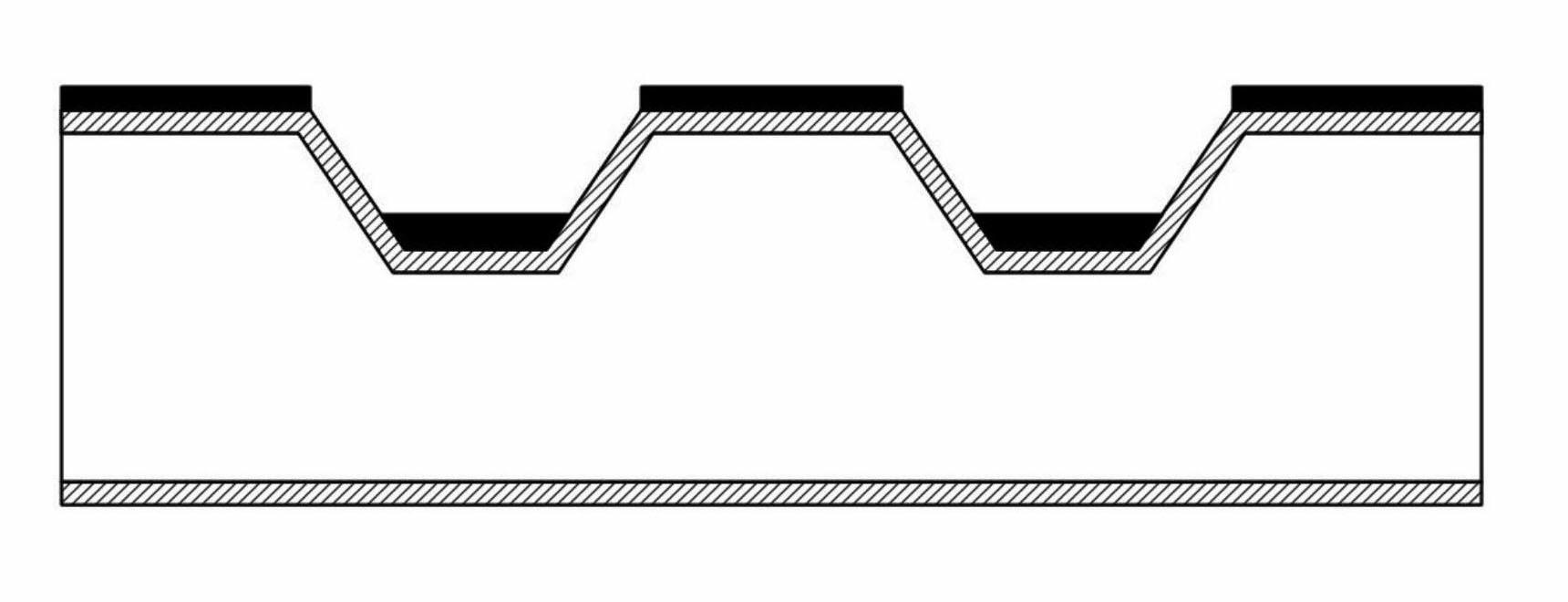

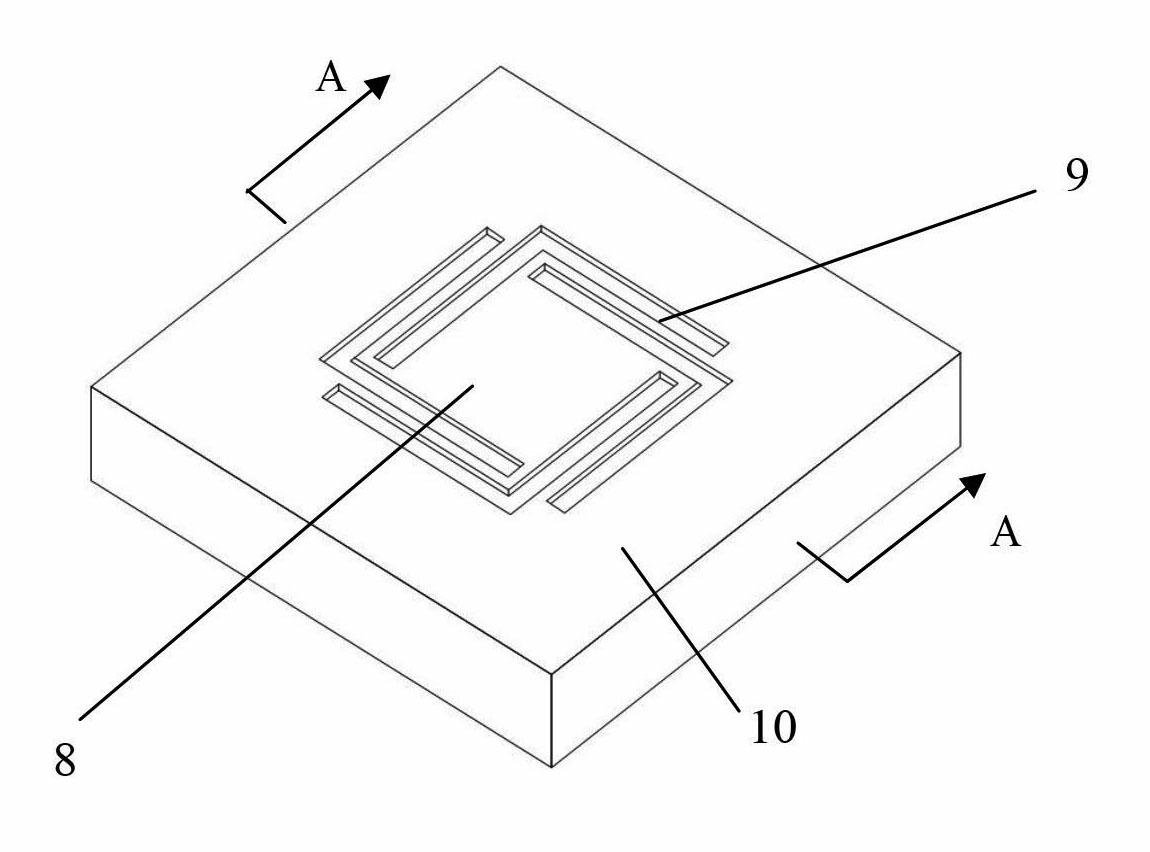

[0055] Such as Figure 5 ~ Figure 14 Shown, utilize the pre-buried mask wet etching process of silicon micromechanical structure of the present invention, prepare a kind of micro-hot plate that is used in micro-environment, specifically comprise the following steps:

[0056] (1) Preparation of SiO 2 Film layer: such as Figure 5 As shown in the figure, a (100) silicon wafer with N-type double-sided polishing, a resistivity of 0.08Ω·cm to 0.15Ω·cm, and a thickness of 600 μm is selected as the substrate 1 of the silicon micromechanical structure. In a thermal oxidation furnace, thermal oxidation The process produces a thickness of D on the front and back of the silicon wafer 0 =7000 ? of SiO 2 film layer 2;

[0057] (2) Prepare mask pattern: such as Figure 6 As shown, the photoresist is evenly spin-coated on the back of the silicon wafer (the photoresist is a positive photoresist, and the spin-coating speed is adjusted to 3500r / min), and the back of the silicon wafer is fi...

Embodiment 2

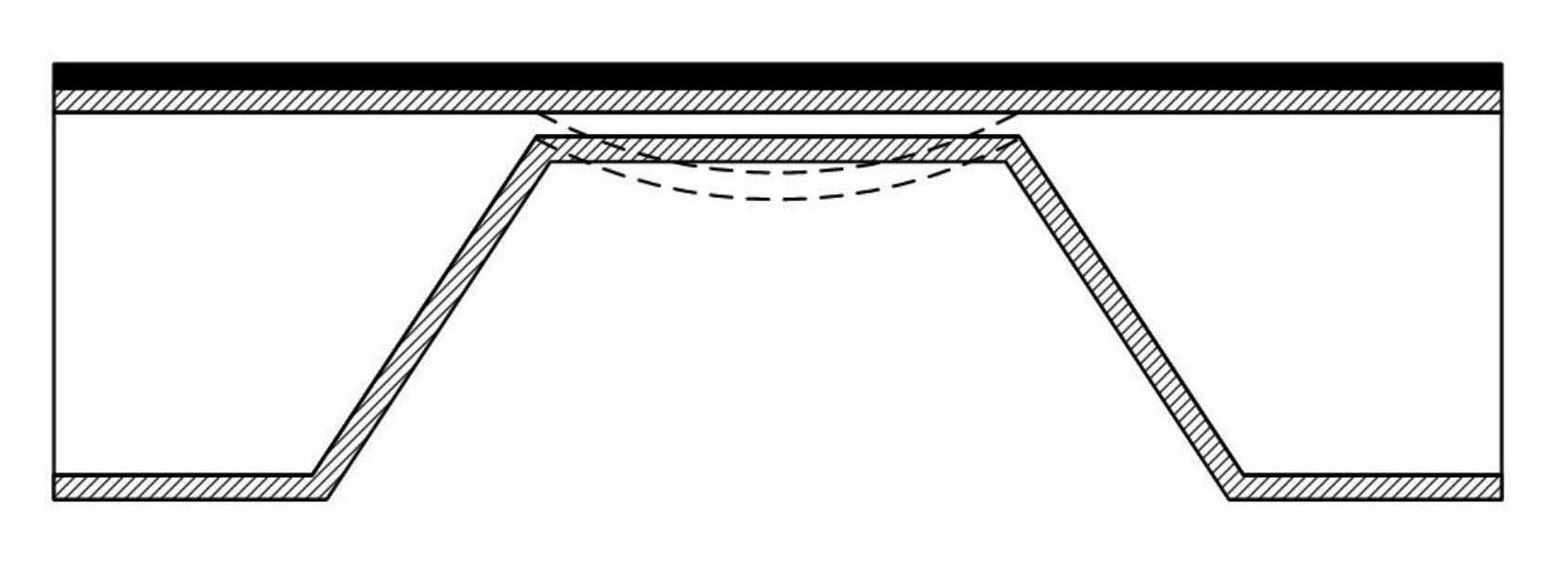

[0063] Utilize the pre-buried mask wet etching process of the silicon micromechanical structure of the present invention to prepare a single cantilever beam-mass micromechanical structure, such as Figure 17 ~ Figure 26 shown, including the following steps:

[0064] (1) Preparation of SiO 2 Film layer: such as Figure 17 and 18 As shown in Fig. 1, a (100) silicon wafer with N-type double-sided polishing, a resistivity of 0.08Ω·cm-0.15Ω·cm, and a thickness of 200 μm is selected as the substrate 1 of the silicon micromechanical structure. In a thermal oxidation furnace, the silicon wafer is The thermal oxidation process is carried out on the surface, and a thickness of D is formed on the front and back sides of the silicon wafer. 0 =7000 ? of SiO 2 film layer 2;

[0065] (2) Prepare mask pattern: such as Figure 19 As shown, the photoresist is uniformly spin-coated on the front and back of the silicon wafer, and the front and back of the silicon wafer are photoetched by us...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More