Thin Film Transistor, Method For Making The Same, Device Having The Same

A technology of thin-film transistors and manufacturing methods, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., and can solve the problems of carrier inflow, low mobility, and inability to obtain IGZO single-film field-effect mobility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0212] The mobilities of Examples 1, 2, and 3, and Comparative Examples 1 and 2 were compared for fabrication of bottom-gate thin-film transistors. Table 4 is a table showing Ga / (In+Ga) of each transistor, oxygen partial pressure / argon partial pressure and mobility during film formation.

[0213] [Table 4]

[0214]

[0215]

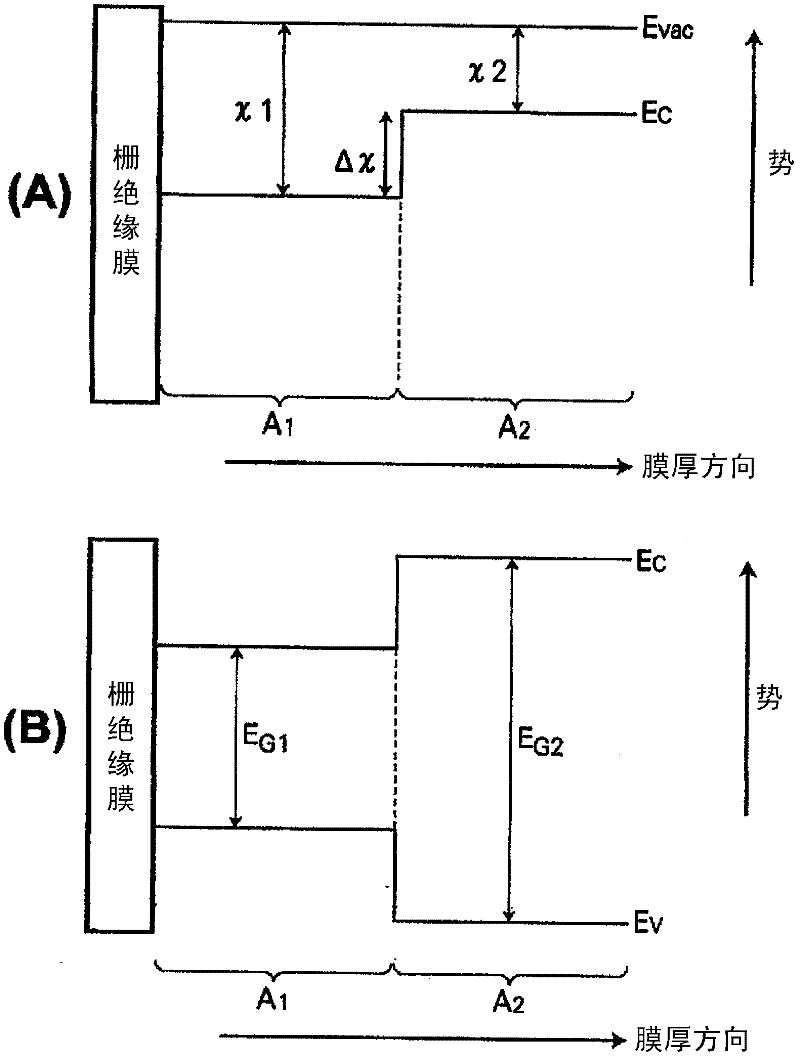

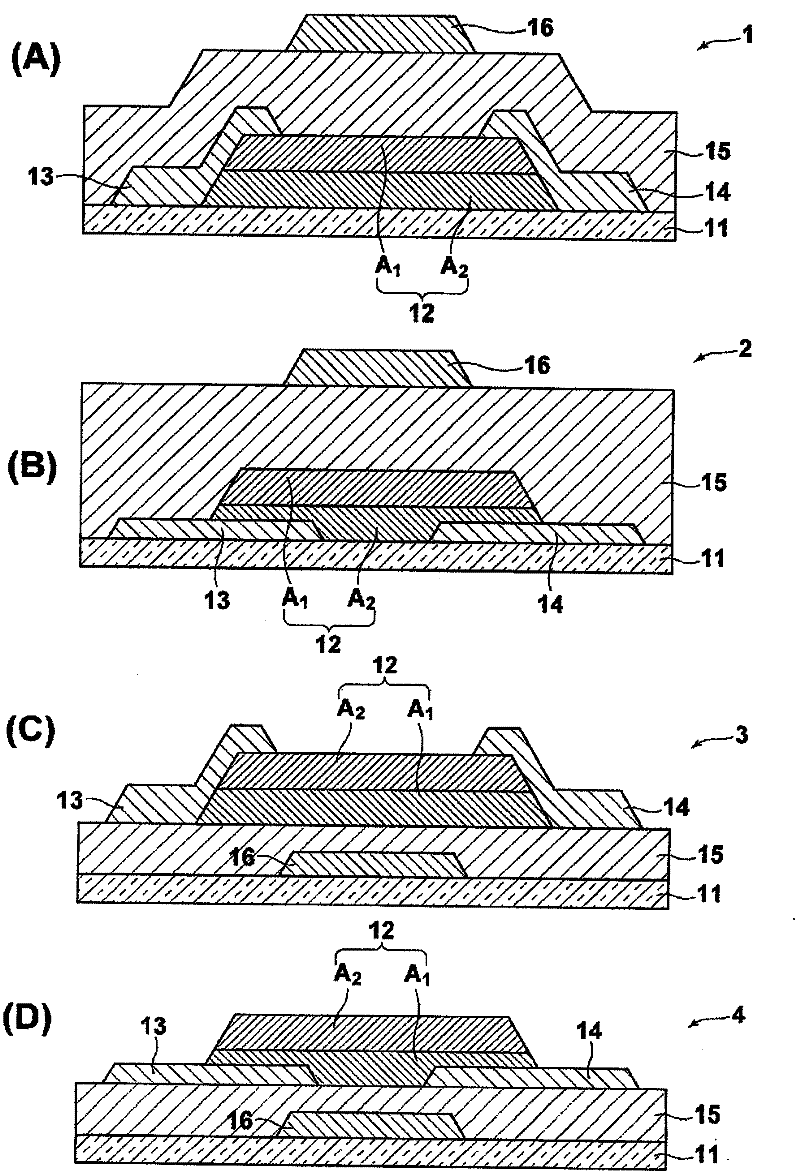

[0216] As Example 1, bottom-gate and top-gate thin film transistors were produced. As the substrate, SiO with 100nm formed on the surface is used 2 A p-type silicon substrate (manufactured by Mitsubishi Materials Corporation) doped with a high concentration of an oxide film. The oxide semiconductor layer is made of a material composed of IGZO. First, as the first region A 1 After sputtering a 5nm InGaZnO film with Ga / (In+Ga)=0.25 and Zn / (In+Ga)=0.5, the second region A 2 A 30 nm IGZO film of Ga / (In+Ga)=0.75 and Zn / (In+Ga)=0.5 was formed by sputtering. The oxide semiconductor layer is formed continuously between regions without being exposed to t...

Embodiment 2

[0232] The element configuration is the same as in Example 1, and only the composition of the oxide semiconductor layer is different. First, as the first area A 1After sputtering a 5nm IGZO film with Ga / (In+Ga)=0.375 and Zn / (In+Ga)=0.5, the second region A 2 A 30 nm IGZO film of Ga / (In+Ga)=0.625 and Zn / (In+Ga)=0.5 was formed by sputtering. The oxide semiconductor layer is formed continuously between regions without being exposed to the atmosphere. The sputtering of each area is based on the use of In 2 o 3 Target, Ga 2 o 3 Target, ZnO target co-sputtering (co-sputter) carried out. The adjustment of the film thickness of each region is performed by adjusting the film formation time. The detailed sputtering conditions of each region are as follows.

[0233] (first area A 1 sputtering conditions)

[0234] Achieved vacuum degree: 6×10 -6 Pa

[0235] Film forming pressure: 4.4×10 -1 Pa

[0236] Film forming temperature: room temperature

[0237] Oxygen partial pressu...

Embodiment 3

[0246] The device configuration is the same as in Example 1, but the composition and oxygen concentration of the oxide semiconductor layer are different. First, as the first area A 1 After sputtering and forming a 5nm IGZO film with Ga / (In+Ga)=0.0 and Zn / (In+Ga)=0.5, the second region A 2 A 30 nm IGZO film of Ga / (In+Ga)=1.0 and Zn / (In+Ga)=0.5 was formed by sputtering. The oxide semiconductor layer is formed continuously between regions without being exposed to the atmosphere. The sputtering of each area is based on the use of In 2 o 3 Target, Ga 2 o 3 Target, ZnO target co-sputtering (co-sputter) carried out. The adjustment of the film thickness of each region is performed by adjusting the film formation time. The detailed sputtering conditions of each region are as follows.

[0247] (first area A 1 sputtering conditions)

[0248] Achieved vacuum degree: 6×10 -6 Pa

[0249] Film forming pressure: 4.4×10 -1 Pa

[0250] Film forming temperature: room temperature

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More