Manufacturing method of uniaxial strain SGOI (SiGe-on-Insulator) wafer on SiN buried insulating layer based on mechanical bending table

A production method and uniaxial strain technology, applied in the field of microelectronics, can solve the problems of easily broken silicon wafers, complex process steps, long production cycle, etc., and achieve low surface roughness, simple production process, and few production equipment. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] Embodiment 1: Preparation of 4-inch uniaxially strained SGOI wafer

[0036] 1. SGOI wafer selection: 4-inch (100) or (110) wafer ((100) or (110) refers to a certain crystal surface of the SGOI wafer crystal surface), Si substrate thickness 0.4mm, The SiN buried insulating layer is 500nm thick, and the top SiGe layer is 500nm thick.

[0037] SGOI wafer diameter selection: the larger the diameter of the SGOI wafer, the smaller the minimum bending radius of its bending, the greater the strain of the obtained uniaxially strained SGOI wafer, and the final electron migration of the uniaxially strained SGOI wafer The enhancement of rate and hole mobility is also higher. For the uniaxially strained SGOI wafer based on the SiN buried insulating layer produced in the present invention, SGOI wafers with different diameters from inches to 12 inches can be selected according to the different processes of the SGOI devices and circuits.

[0038] SGOI wafer crystal plane and crystal ...

Embodiment 2

[0056] Embodiment 2: Preparation of 5-inch uniaxially strained SGOI wafer

[0057] 1. SGOI wafer selection: 5-inch (100) or (110) crystal plane, Si substrate thickness 0.55mm, SiN buried insulating layer thickness 300nm, top SiGe thickness 50nm.

[0058] 2. Selection of bending radius of curvature: According to the selected SGOI wafer, the radius of curvature of the bending table is selected to be 0.75m.

[0059] 3. SGOI wafer bending process steps:

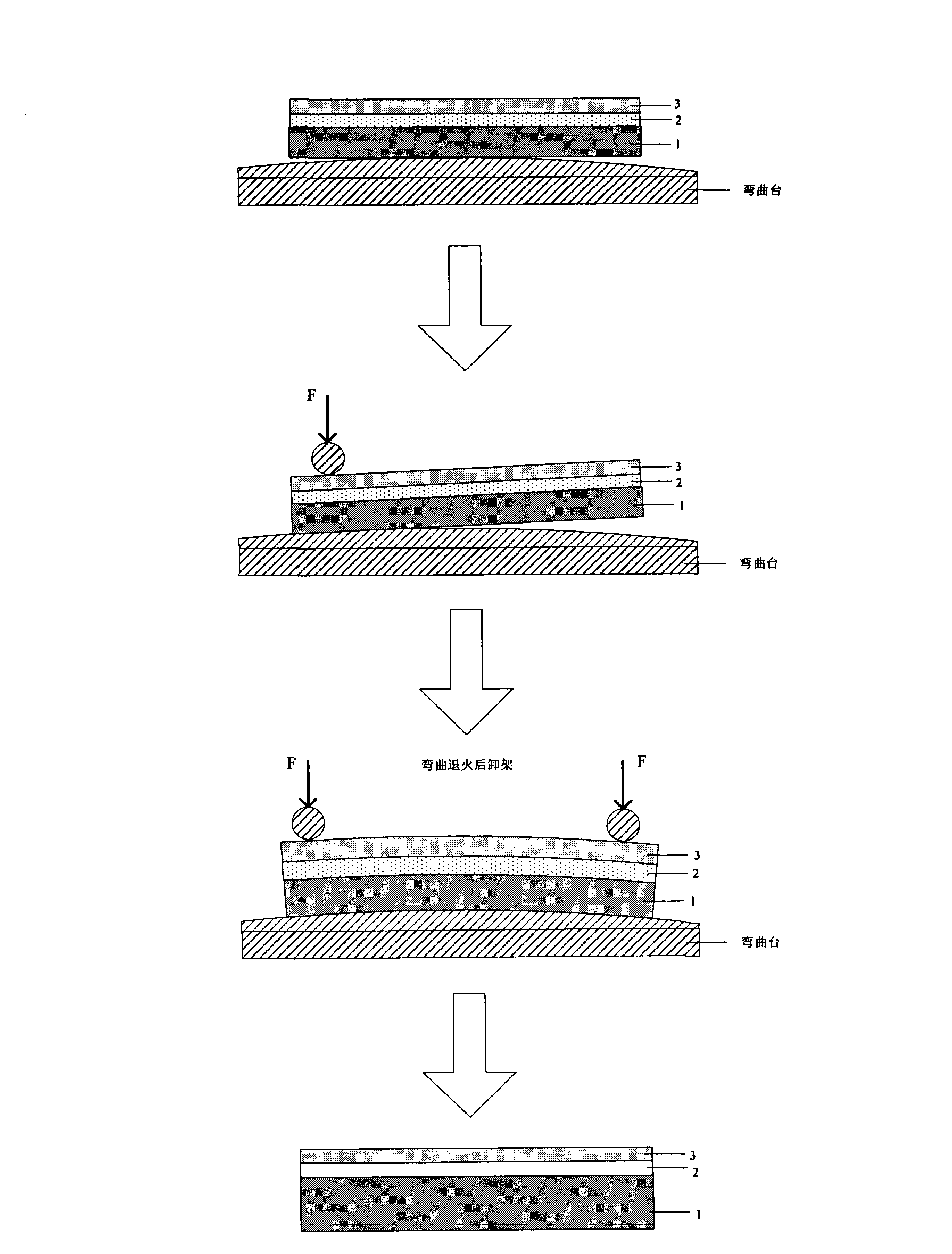

[0060] 1) Place the top Si layer of the SGOI wafer upwards (or downwards) on a clean bending table, with its or direction parallel to the bending direction, such as image 3 or Figure 4 shown;

[0061] 2) Two cylindrical horizontal pressure bars on the bending table are placed horizontally at both ends of the SGOI wafer, 1 cm away from its edge;

[0062] 3) Rotate the ejector nut of one of the pressure rods on the bending table to fix one end of the SGOI wafer first;

[0063] 4) Slowly turn the ejector nut of another pres...

Embodiment 3

[0070] Through the above process steps, a 5-inch uniaxially strained SGOI wafer based on a SiN buried insulating layer can be obtained. Embodiment 3: Preparation of 8-inch uniaxially strained SGOI wafer

[0071] 1. SGOI wafer selection: 8-inch (100) or (110) crystal plane, Si substrate thickness 0.68mm, SiN buried insulating layer thickness 1000nm, top SiGe thickness 1000nm.

[0072] 2. Selection of bending radius of curvature: According to the selected SGOI wafer, the radius of curvature of the bending table is selected to be 0.5m.

[0073] 3. SGOI wafer bending process steps:

[0074] 1) Place the SiGe layer on the top layer of the SGOI wafer upwards (or downwards) on the arc-shaped bending table, and its bending direction is parallel to the or direction, such as image 3 or Figure 4 shown;

[0075] 2) Two cylindrical horizontal pressure bars on the bending table are placed horizontally at both ends of the SGOI wafer, 1 cm away from its edge;

[0076] 3) Rotate the e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More