Method for achieving controller area network (CAN) bus network nodes

A CAN bus, network node technology, applied in the field of CAN bus network node implementation, can solve the problems of increasing power consumption and design complexity, increasing the size of the chip, and consuming logic resources, so as to reduce the overhead of logic resources and reduce power consumption. , the effect of small size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

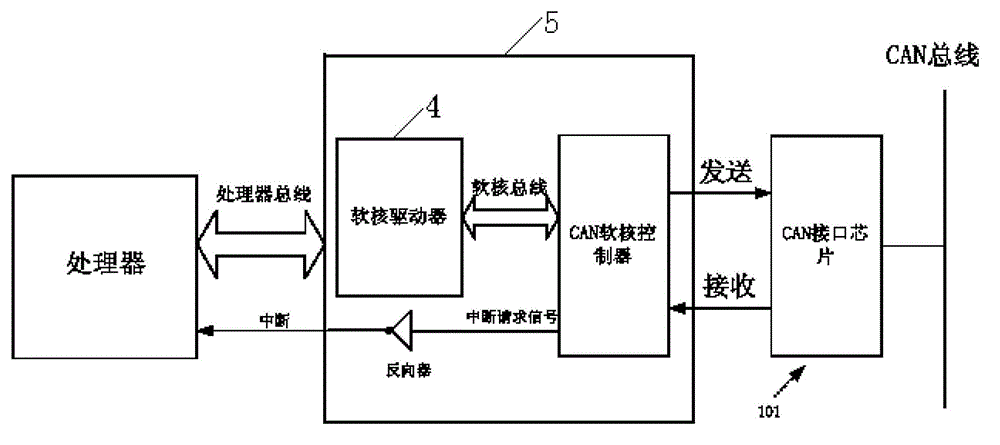

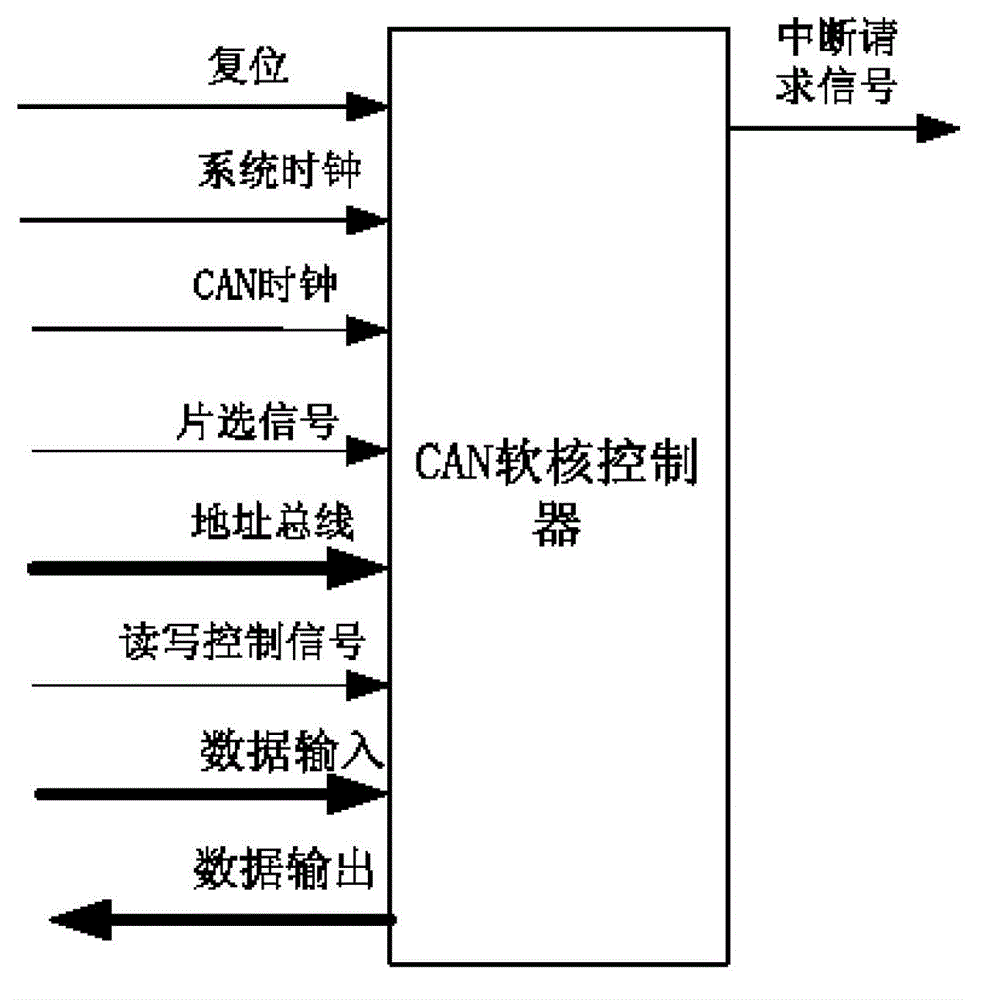

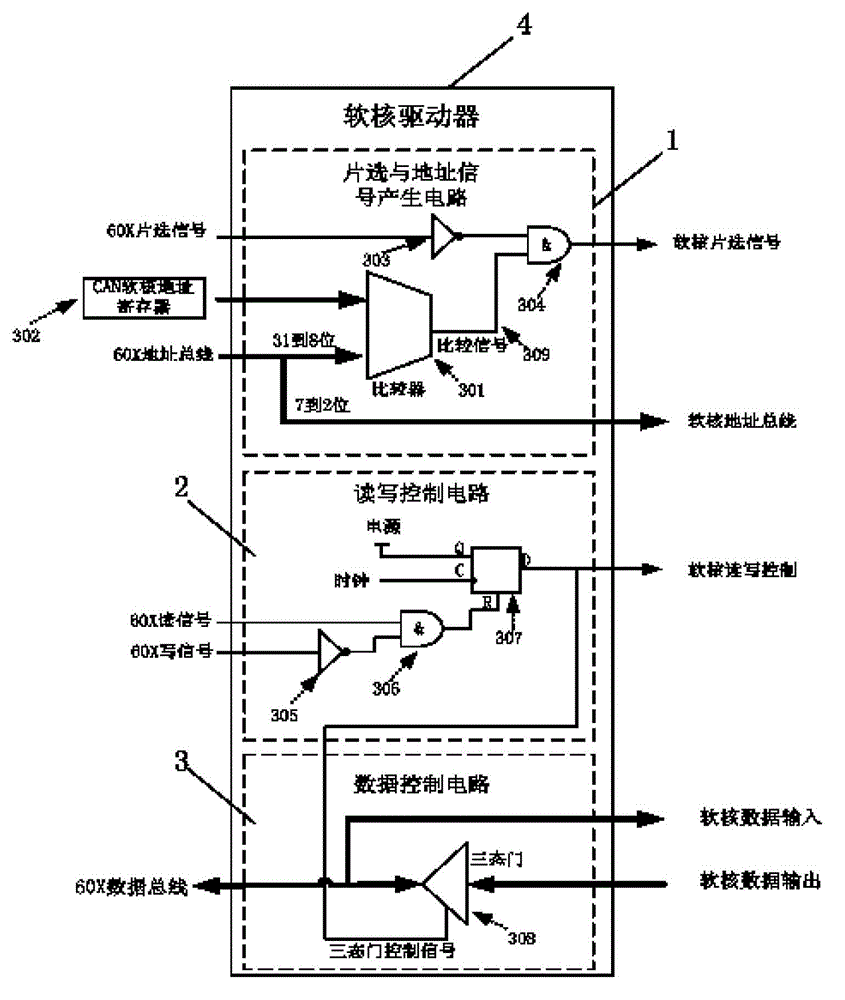

[0019] refer to figure 1 . figure 1 Describes a best embodiment of the present invention using Xilinx's XC5VSX95T programmable logic array (FPGA) as the programmable logic array chip 5, and PowerPC as the CAN driver software processor to realize the CAN bus network node. The CAN soft-core controller embedded in the programmable logic array chip 5 is a mature commercial product, which can realize functions such as the physical layer and the media access control sublayer of the CAN bus. Users only need to embed this commercial module into user logic. The CAN driver software processor can be realized by CPU chips such as PowerPC and DSP. The processor bus connected between the CAN driver software processor and the programmable logic array chip 5 can be EMIF of DSP, 60X of PowerPC, PCIE, RapidIO, PCI, etc. The best implementation mode...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More