NMOS (N-Channel Metal Oxide Semiconductor) transistor forming method and corresponding COMOS structure forming method

A transistor and N-type technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that affect device performance and cannot effectively alleviate the hot carrier injection effect, so as to simplify the process flow and relieve heat Carrier injection effect, effect of reducing hot carrier injection effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

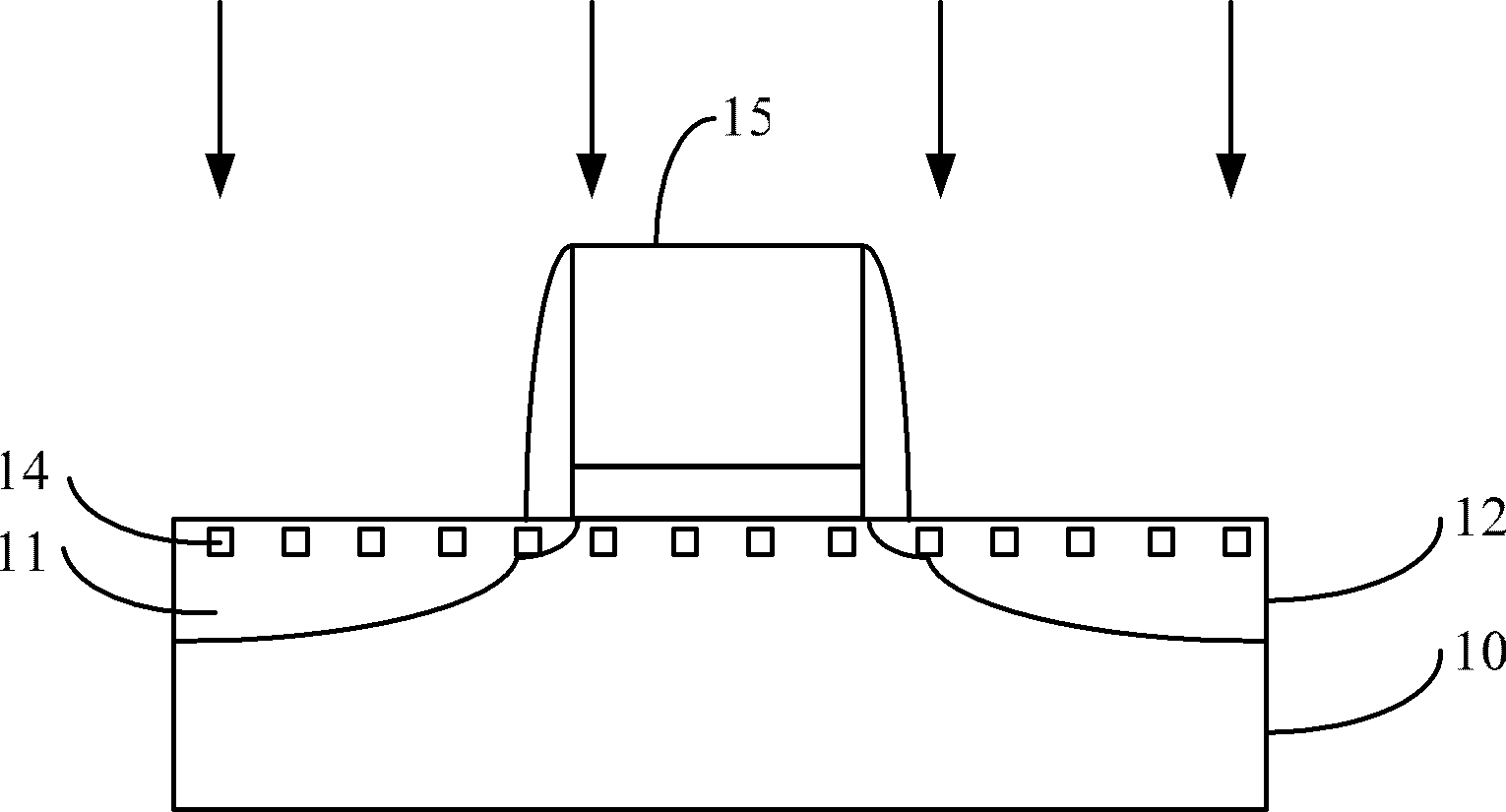

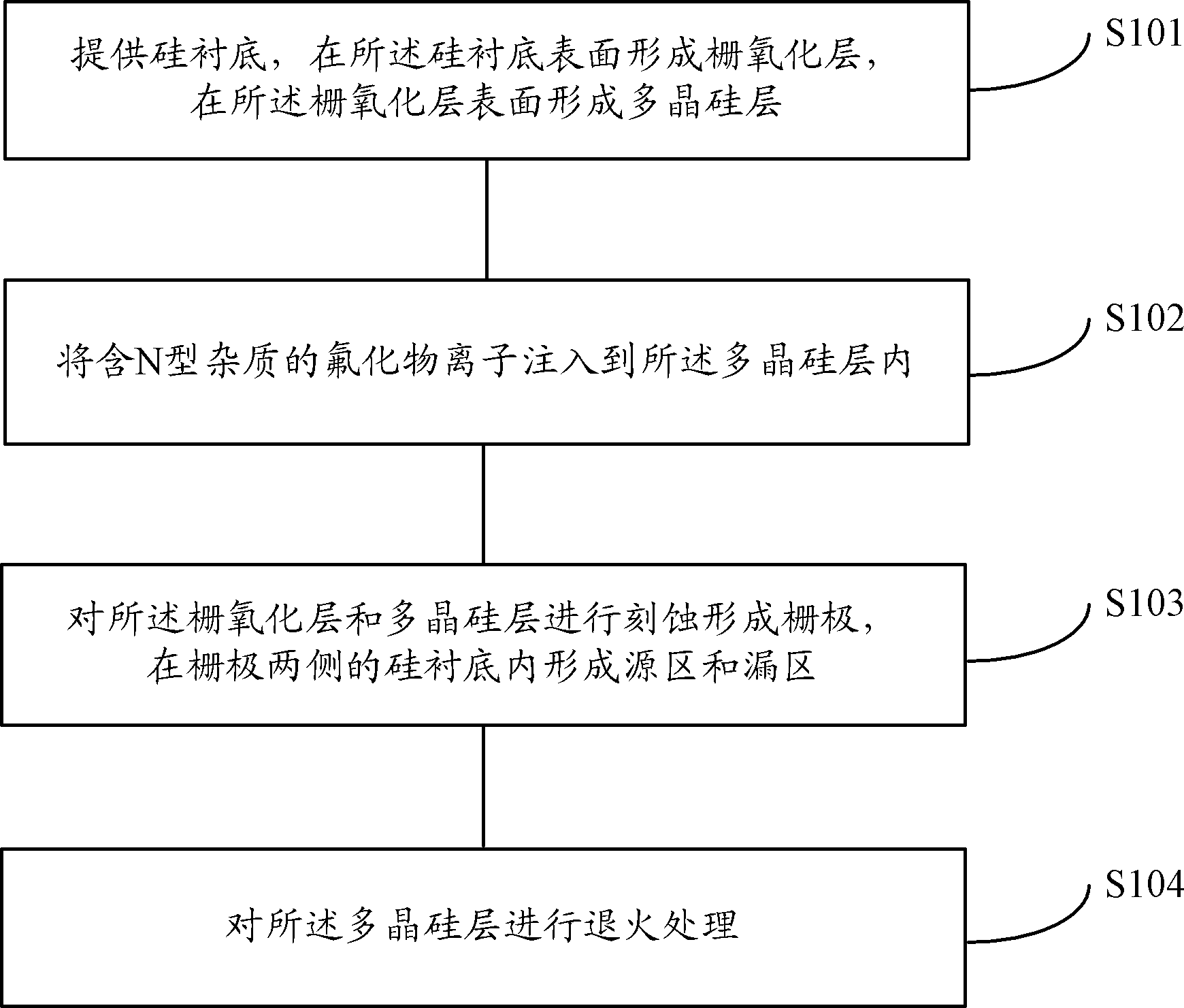

[0029] Since the fluorine ions implanted into the surface layer of the silicon substrate in a large dose will re-form fluorine molecules and escape from the silicon substrate during the annealing process, the inventors have found through research that during the manufacturing process of the NMOS structure, by adding N-type impurities Fluoride is implanted into the polysilicon layer, and then annealing is used to diffuse fluorine ions to the surface of the silicon substrate, so that the fluoride ions combine with silicon on the surface of the silicon substrate to form a silicon-fluorine bond with a large bond energy, which blocks the heat-carrying current in the channel Carriers enter the gate oxide layer, which greatly alleviates the hot carrier injection effect.

[0030] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com