Terminal structure of high-voltage semiconductor device and method for manufacturing terminal structure

A terminal structure and semiconductor technology, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve problems such as the complexity of process preparation, and achieve the effects of increasing electric field strength, improving voltage resistance, and improving breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The terminal structure and manufacturing method of the high-voltage semiconductor device provided by the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

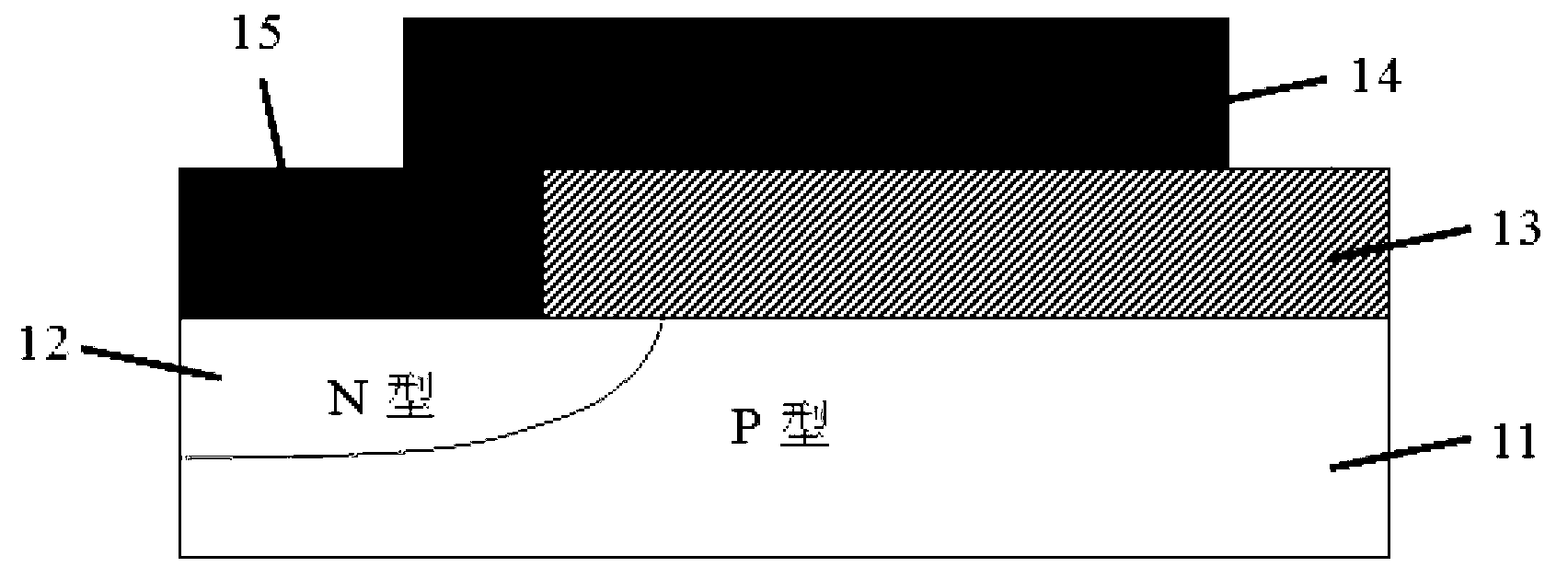

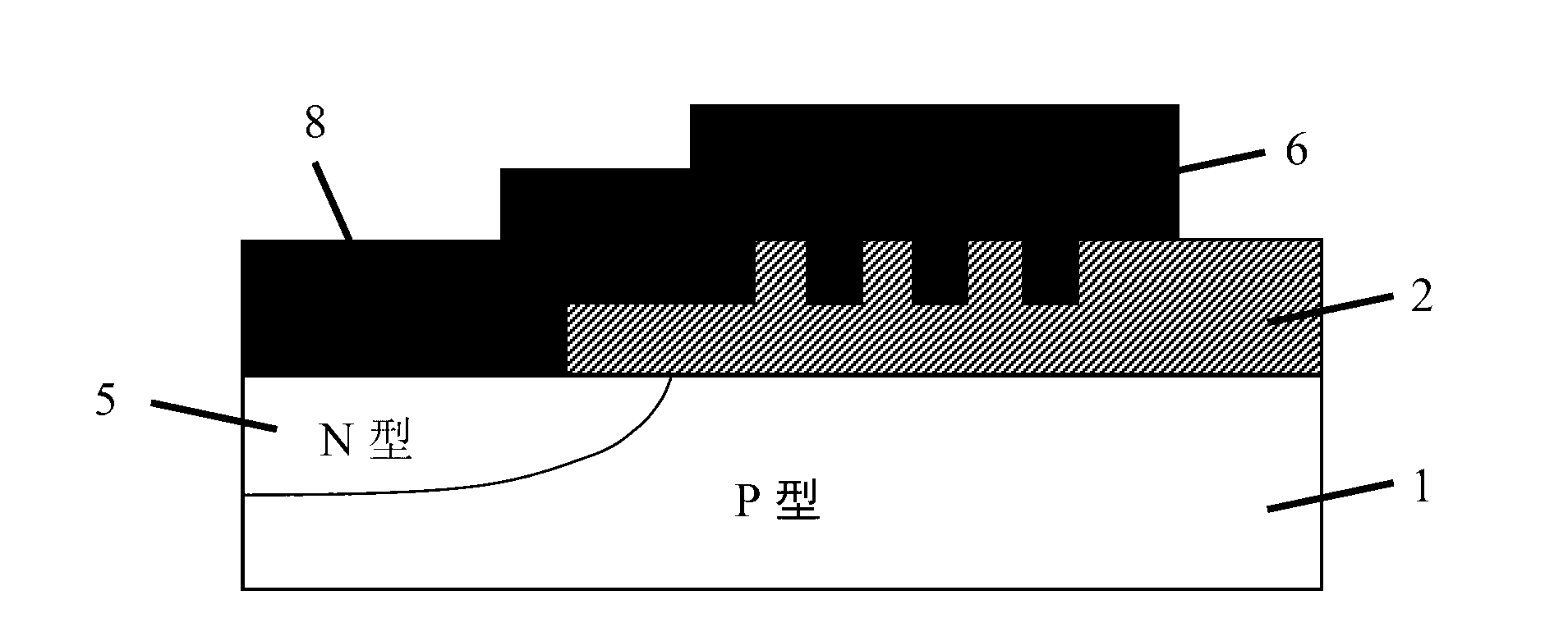

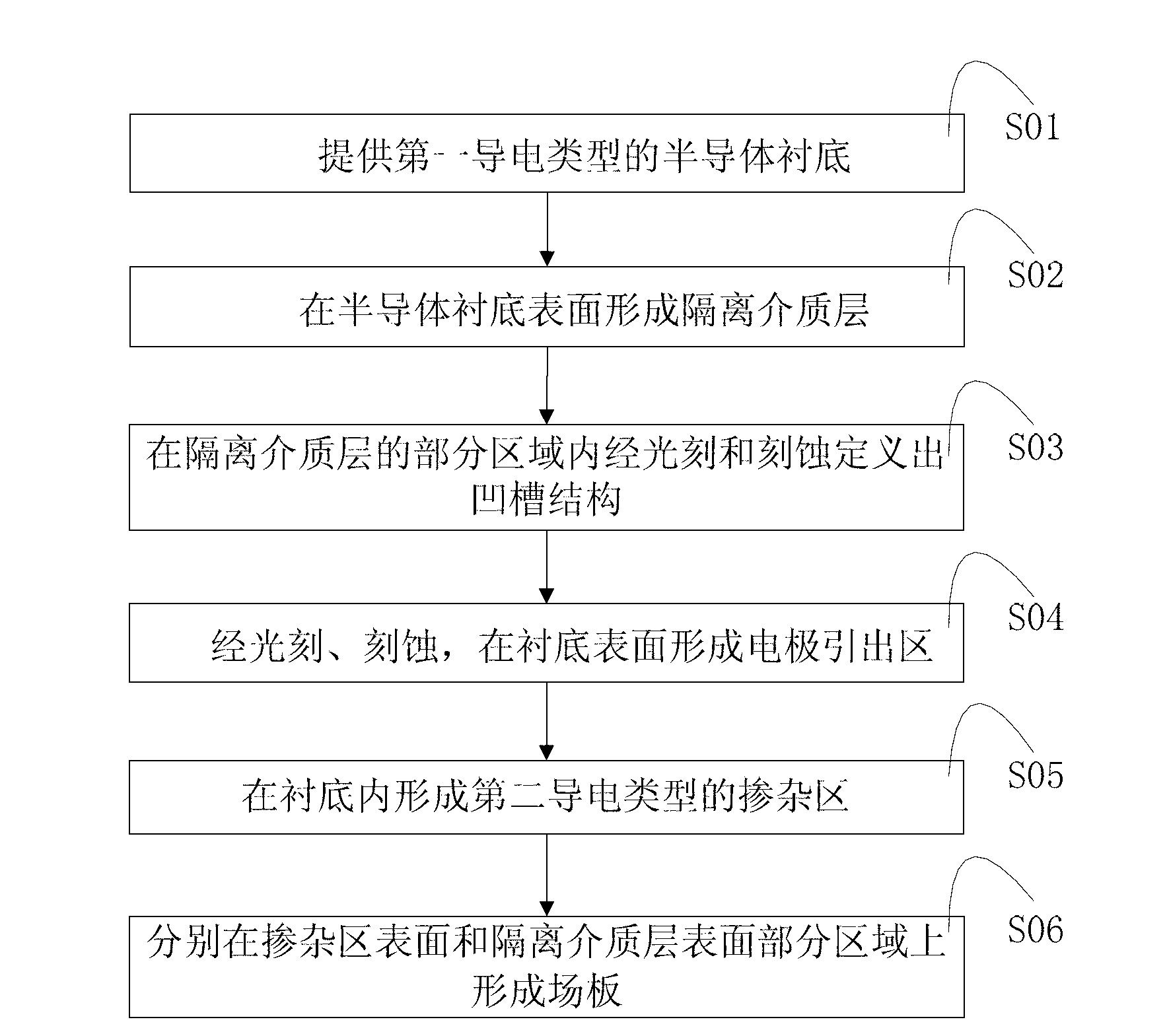

[0029] The invention provides a terminal structure of a high-voltage semiconductor device. see figure 2 , figure 2 It is a structural schematic diagram of a preferred embodiment of a terminal structure of a high-voltage semiconductor device of the present invention. For ease of description, in this embodiment, specific P-type and N-type regions are included, and a P-type silicon substrate 1 is taken as an exam...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness range | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More