Insulated gate transistor device and manufacturing technology method thereof

A technology of insulated gate transistors and manufacturing processes, which is applied in the field of electronics to achieve the effects of reducing manufacturing costs, preventing the occurrence of latch-up effects, and facilitating the control of etching processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

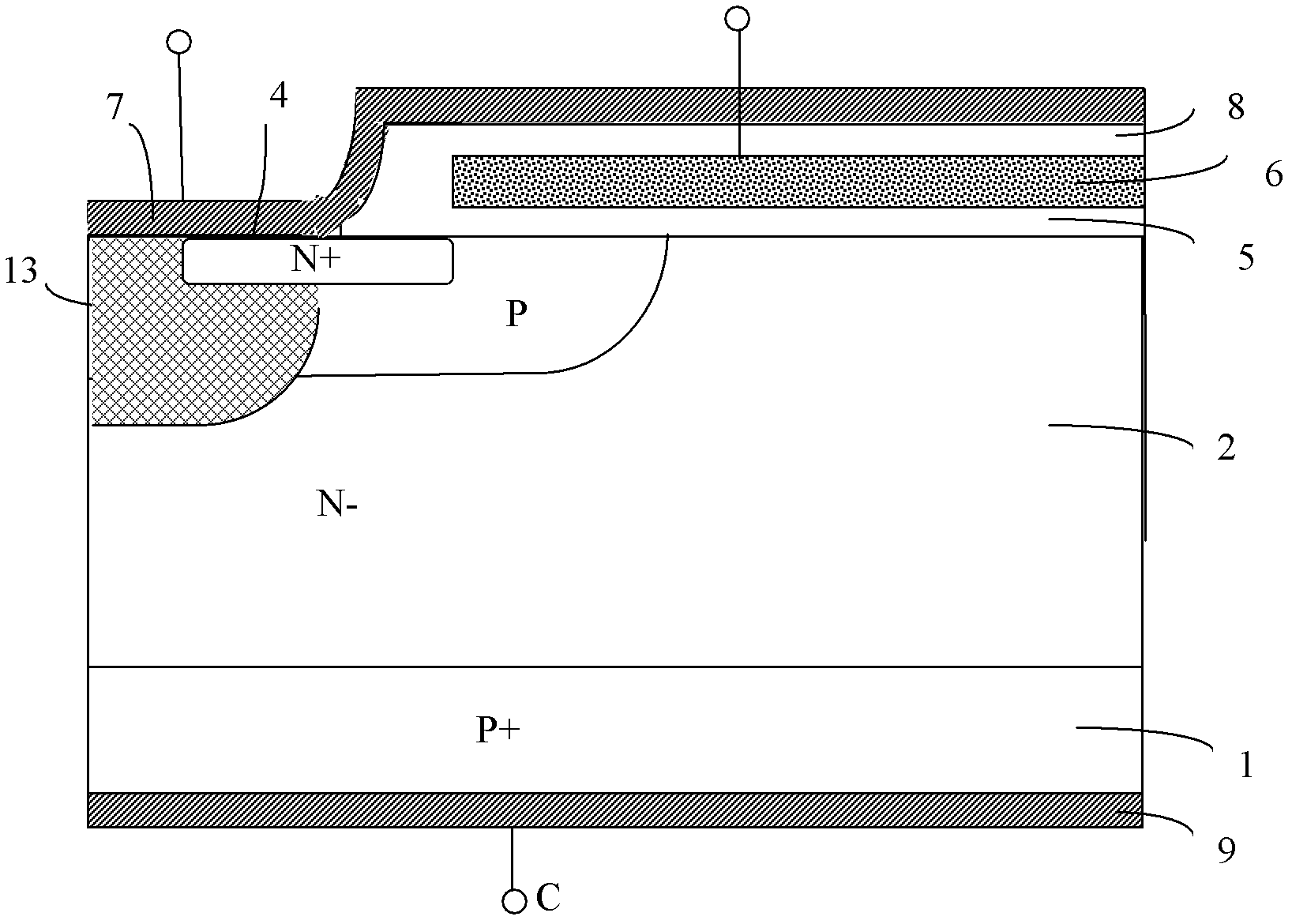

[0031] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

[0032] As shown in Figure 5, the present invention provides a manufacturing process method of an insulated gate transistor device (IGBT), comprising the following steps:

[0033] 1. If Figure 5A As shown, a layer of 50-110um (micrometer) thick N-type epitaxial layer 22 is grown on the surface layer of the P+ semiconductor substrate 21. Then a layer of silicon oxide is grown on the surface of the N-type epitaxial layer 22, and photolithography and etching A mask layer 33 with a certain pattern is formed by the process, and finally P-type impurities such as boron ions are selectively implanted through the mask layer 33 . Then, the implanted ions are diffused and advanced through a high-temperature thermal process to form the first layer of P-type region 23b on the surface.

[0034] 2. If Figure 5B As shown, the mask layer 33 is removed, and...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More