Heat insulation structure based on Parylene filling and preparation method thereof

A technology of structural layers and substrates, applied in the field of MEMS, can solve the problems of increasing process complexity, reducing yield, and prone to voids, saving layout area, reducing measurement errors, and improving device performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

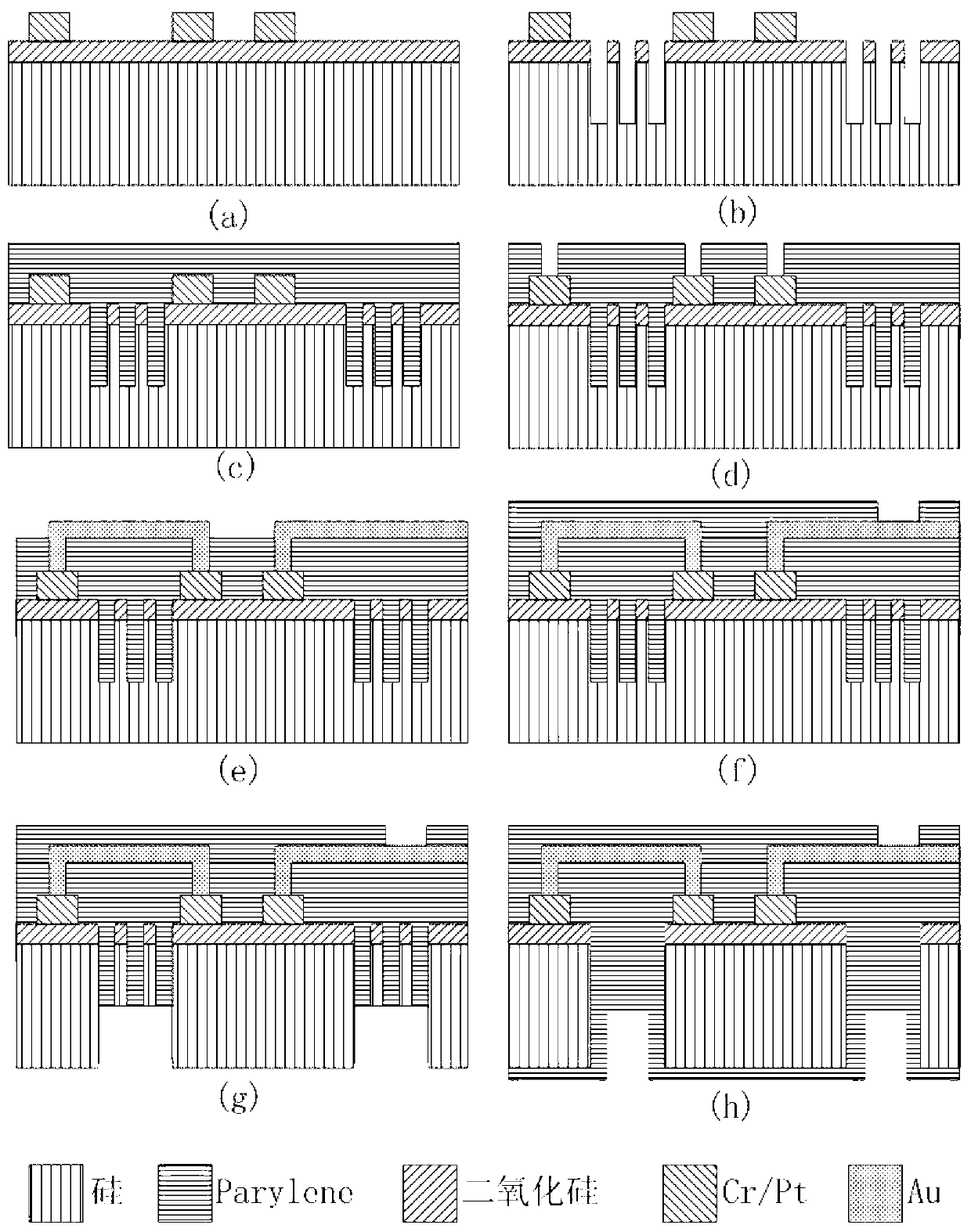

[0030] 1) First, use the usual way to process CMOS circuits or MEMS structures, just ensure that there is a silicon oxide spacer between the base silicon wafer, such as figure 2 (a) shown.

[0031] The spacer acts as an etch stop layer. It can be formed when making the structural layer, or it can be a natural product using the SOI process.

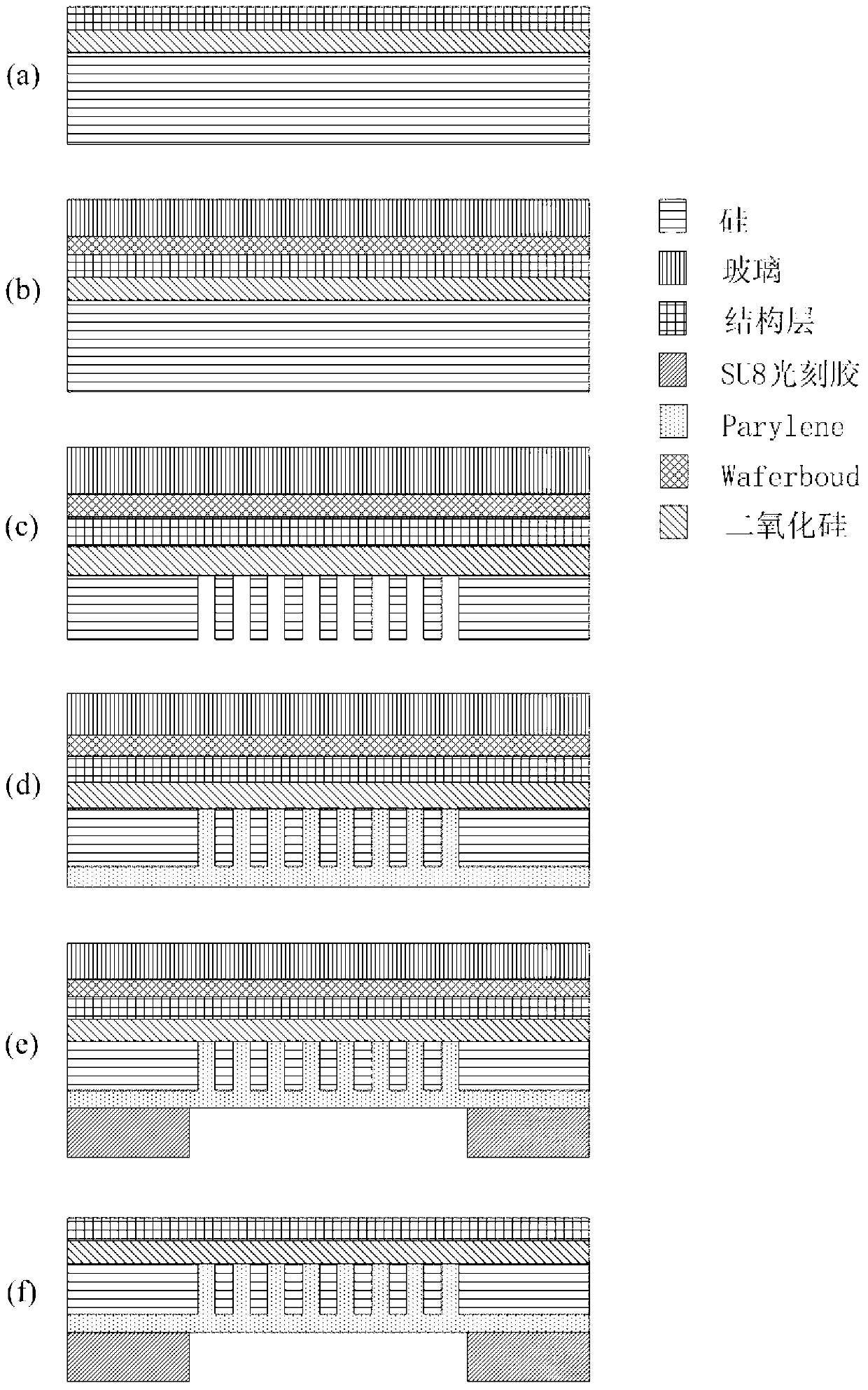

[0032] 2) Use WaferBond temporary bonding agent to bond the glass liner to protect the silicon chip from cracking, such as figure 2 (b) shown.

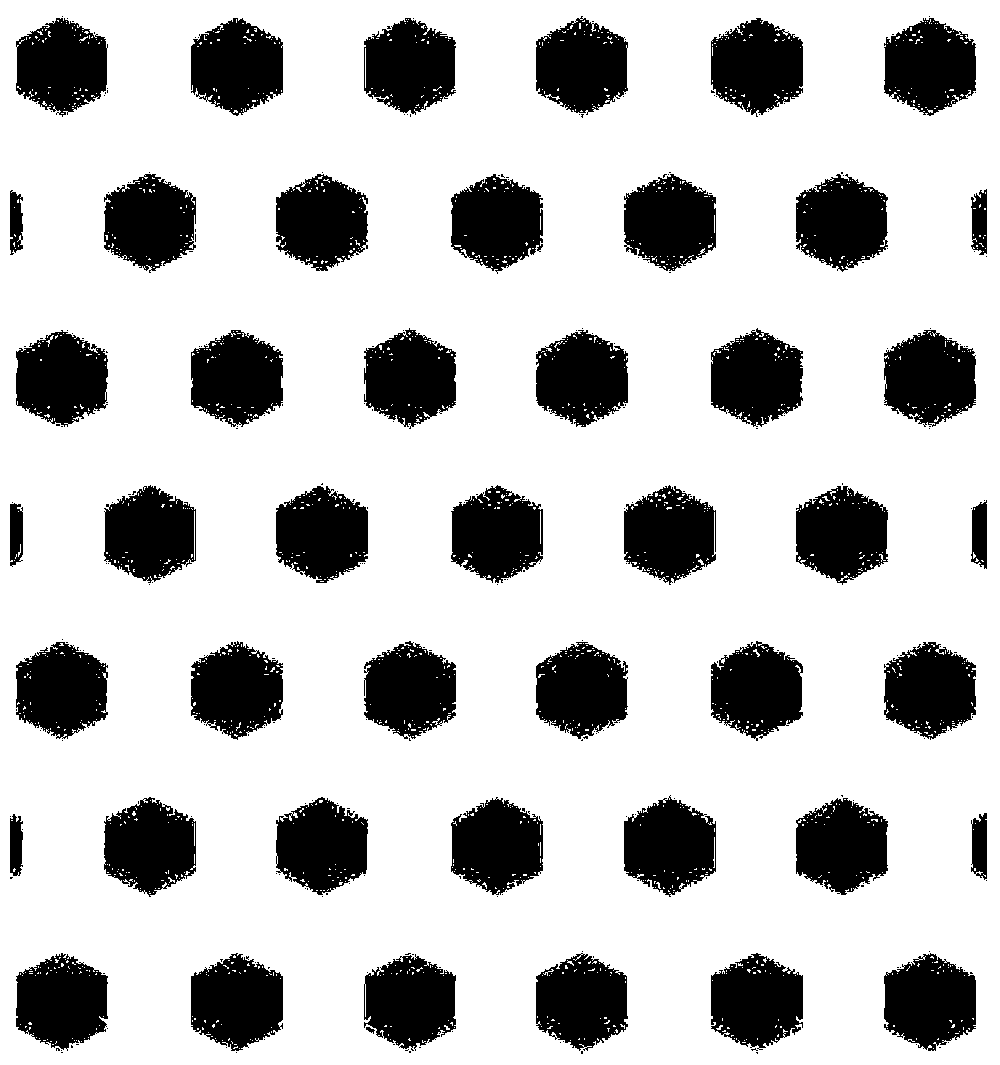

[0033] 3) Thin the silicon wafer from the back to 50um, and perform deep etching in the reserved heat insulation area, leaving substantially equidistant (20um) and uniformly arranged columns, such as figure 2 (c) shown. Columns may be cylinders or prisms with cross-sectional shapes including but not limited to Figure 3a and Figure 3b The quadrilateral and hexagonal structures shown.

[0034] The thickness reduction of the above-mentioned silicon wafer needs to be comprehensively consid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More