Electron Blocking Layer Growth Method for Epitaxial Structures and Corresponding Epitaxial Structures

A technology of electronic blocking layer and epitaxial structure, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problems of poor chip light efficiency improvement, reduce Droop effect, improve spillover, and increase activation efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

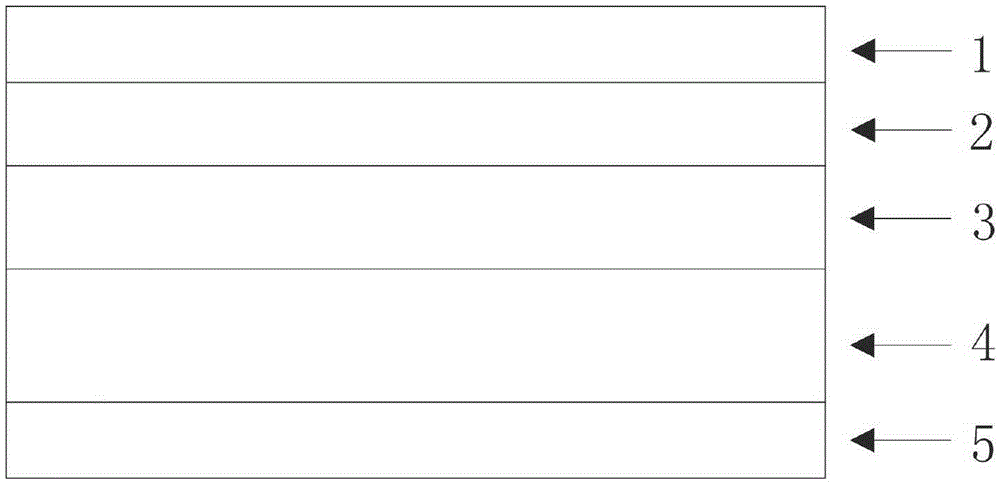

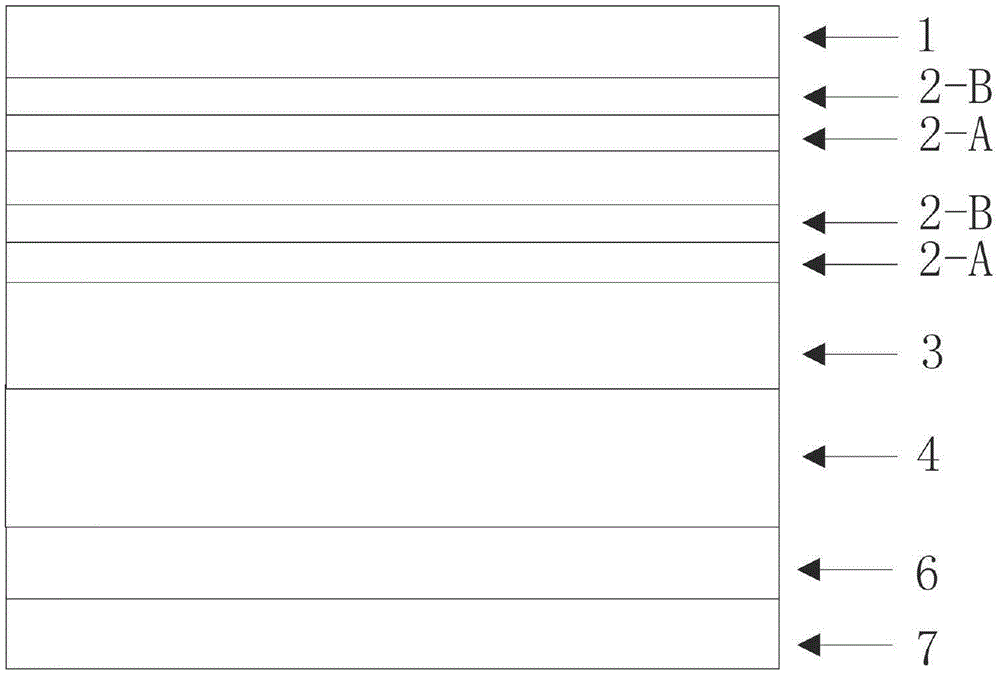

[0055] The invention uses AixtronCruisIIMOCVD to grow high-brightness GaN-based LED epitaxial wafers. Using high-purity H 2 or high purity N 2 or high purity H 2 and high purity N 2 The mixed gas is used as carrier gas, high-purity NH3 is used as N source, trimethylgallium (TMGa) and triethylgallium (TEGa) are used as gallium source, trimethylindium (TMIn) is used as indium source, silane (SiH 4 ) as N-type dopant, trimethylaluminum (TMAl) as aluminum source, dimagnesocene (CP 2 Mg) is used as a P-type dopant, the substrate is (0001) sapphire, and the reaction chamber pressure is between 150mbar and 600mbar.

[0056] 1. Under the hydrogen atmosphere of 1050-1150℃, the pressure of the reaction chamber is controlled at 150-200mbar, and the sapphire substrate is treated at high temperature for 4-5 minutes;

[0057] 2. Lower the temperature to 550-580°C, control the pressure of the reaction chamber at 450-600mbar, and grow a low-temperature buffer layer GaN with a thickness o...

Embodiment 2

[0077] For the implementation steps, refer to Example 1 to obtain sample 4.

[0078] The comparison of growth parameters between Comparative Example 2 and Example 2 can be seen in Table 2 below.

[0079] Table 2 contrasts the growth parameters of Example two and Example two

[0080]

[0081] Then, take sample 3 and sample 4 to take the same treatment method as sample 1 and sample 2 and then test the photoelectric performance of sample 3 and sample 4, the parameters obtained can be found in Figure 6 . Figure 6 The vertical axis of is the light efficiency (Lm / w), and the horizontal axis is the number of chip particles. The value corresponding to sample 4 is the upper thicker line, and the value corresponding to sample 3 is the lower thinner line. From Figure 6 According to the data, the brightness of sample 4 is 6-7% higher than that of sample 3. The growth method provided by this patent improves the light efficiency of large-sized chips.

[0082] Based on the above ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More