Double-structure contact hole synchronous-etching technology

A simultaneous etching and contact hole technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem of increasing chemical mechanical polishing time of tungsten plugs, increasing process complexity and cost, and unsatisfactory process effects, etc. problem, to avoid the loss of silicon oxide, reduce the abnormal connection, and reduce the effect of process risk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

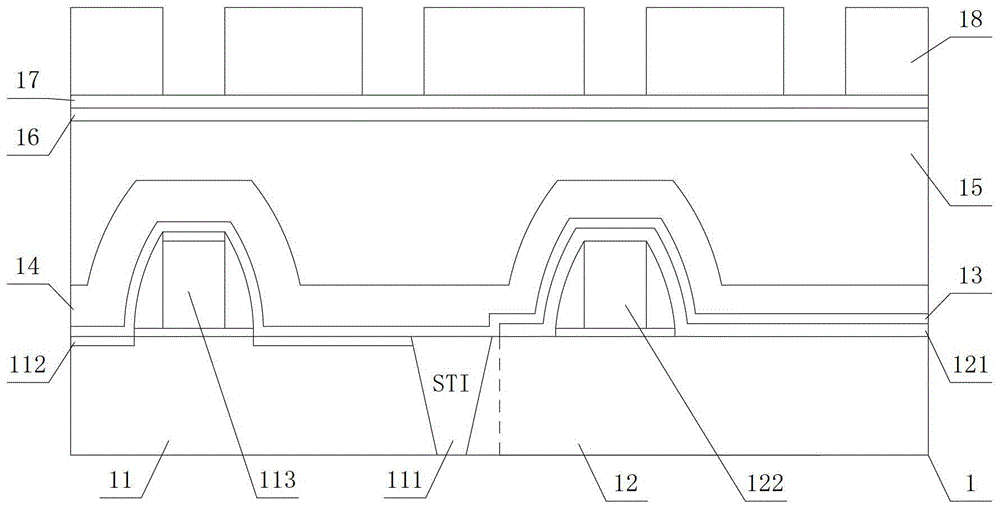

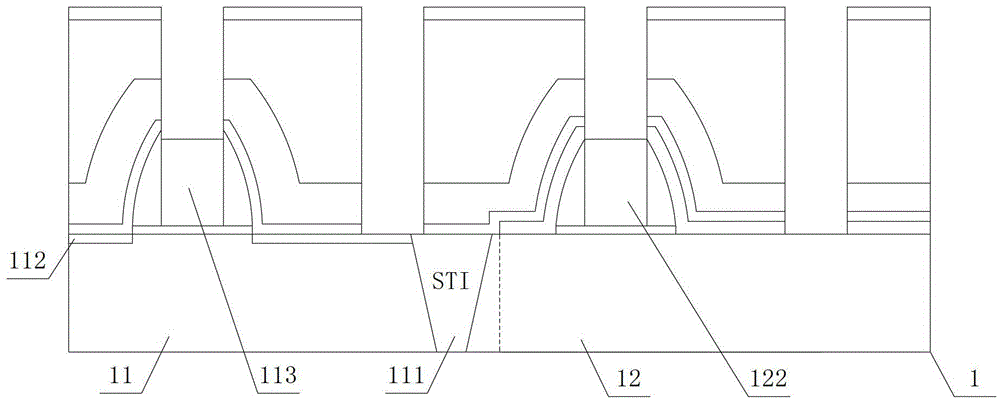

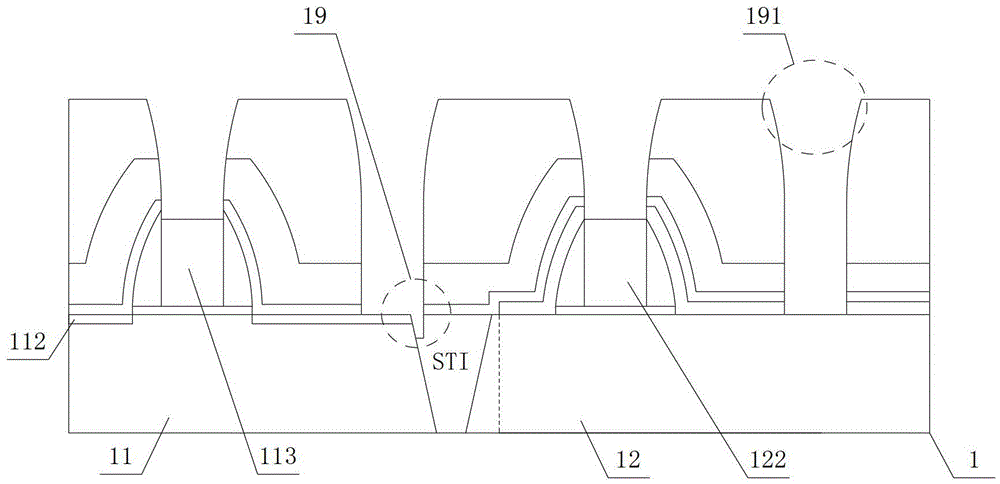

[0044] Figure 4-11 It is a schematic diagram of the flow structure of a dual-structure contact hole simultaneous etching process in the embodiment; as Figure 4-11 As shown, a dual-structure contact hole simultaneous etching process of the present invention:

[0045] First, a substrate 2 with a logic area (logic) 21 and a photosensitive area (pixel) 22 is provided, and the substrate 2 is used to prepare CIS products; the substrate 2 located in the logic area 21 is also provided with shallow trench isolation grooves ( STI) 211, a nickel silicide layer 212 and a first gate structure 213, the nickel silicide layer 212 covers the surface of the substrate 2 not covered by the first gate structure 213 in the logic region and the gate in the first gate structure 213 The upper surface of the electrode; the substrate 2 located in the photosensitive region 22 is provided with a barrier layer (SOR) 221 (preferably, the material of the barrier layer 221 is silicon oxide) and a second ga...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More