Patents

Literature

44results about How to "Fewer etch steps" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

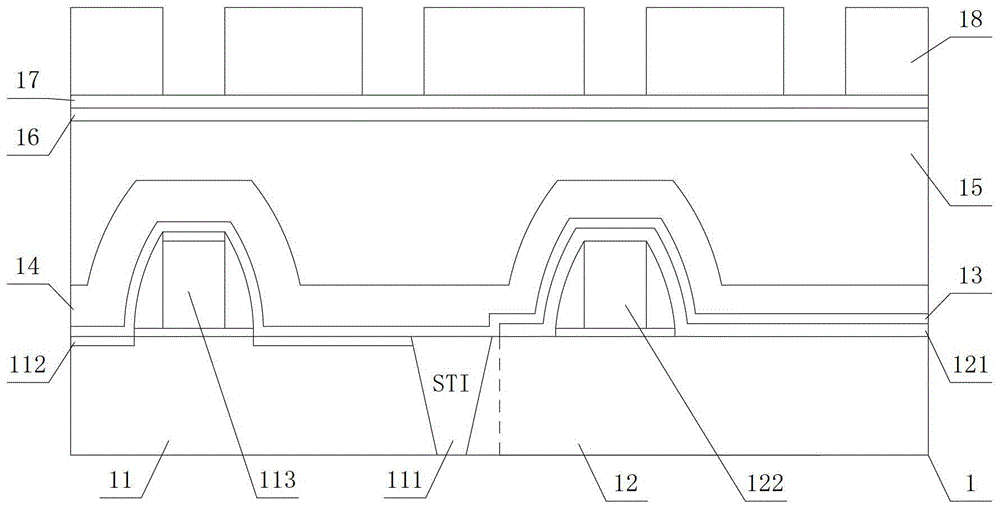

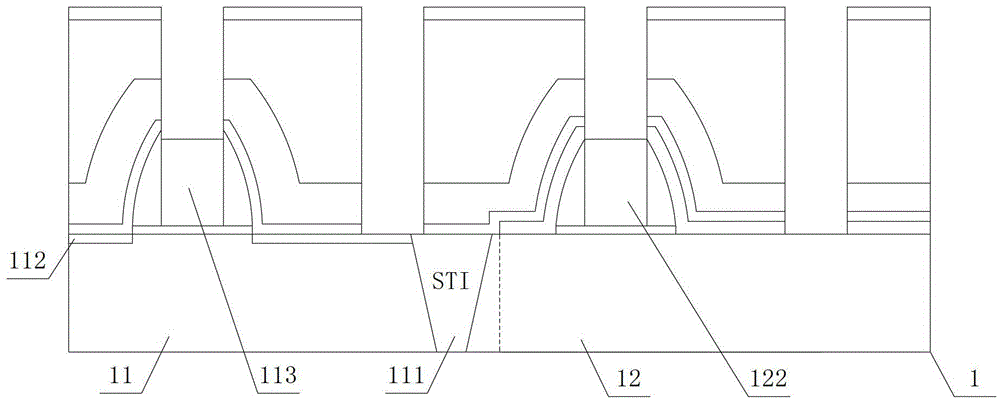

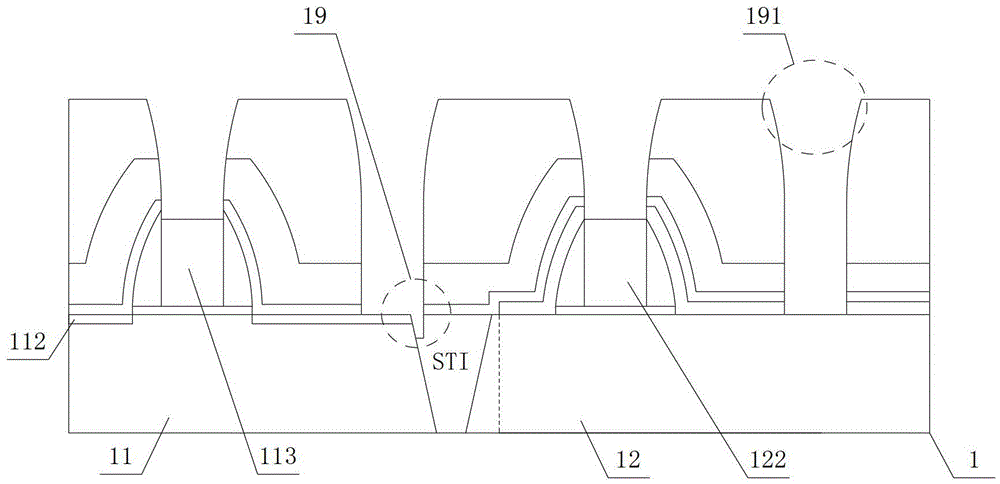

Double-structure contact hole synchronous-etching technology

ActiveCN103337475AReduce the process risk of abnormal connectionReduce lossesSemiconductor/solid-state device manufacturingRadiation controlled devicesDielectric layerMetal

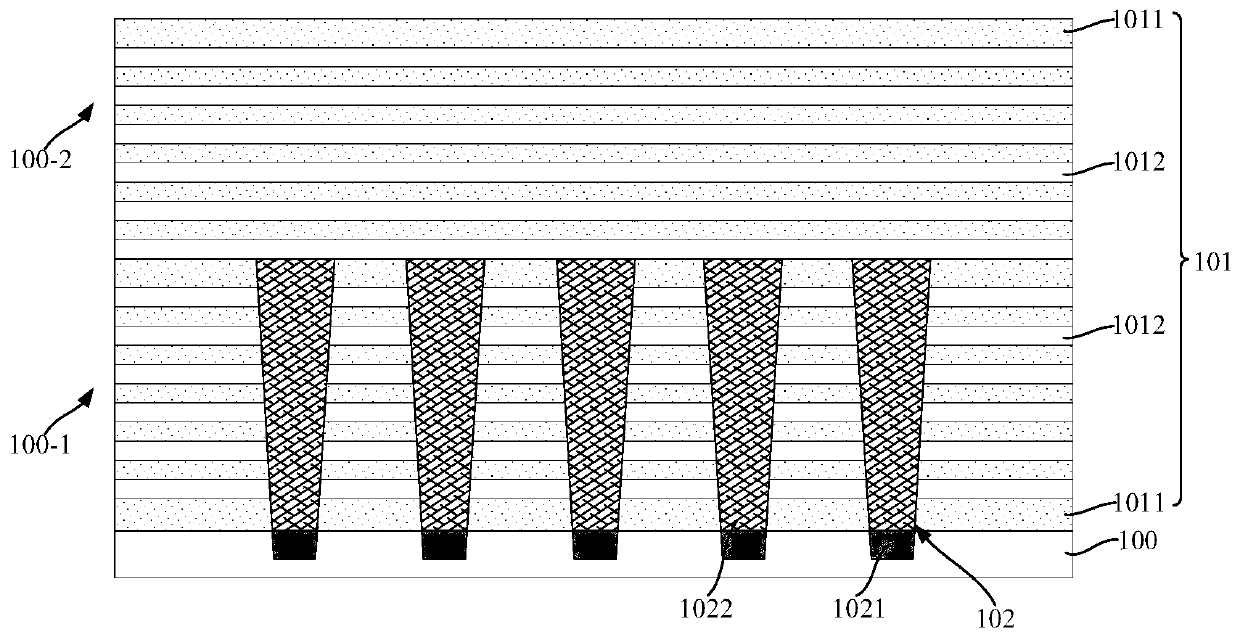

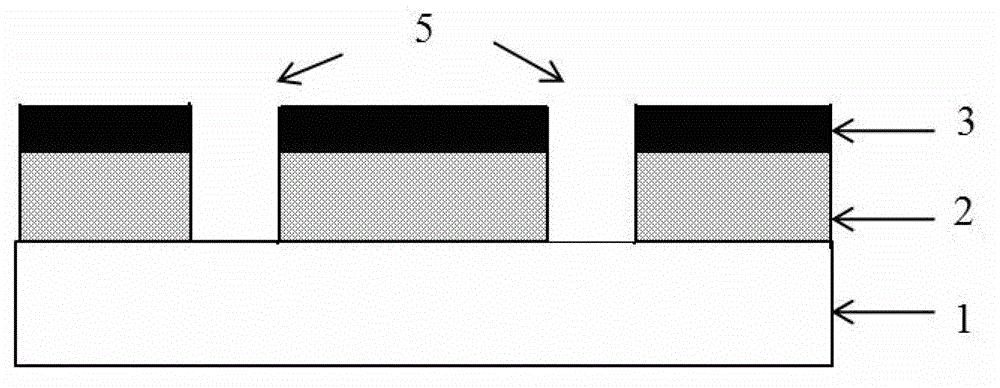

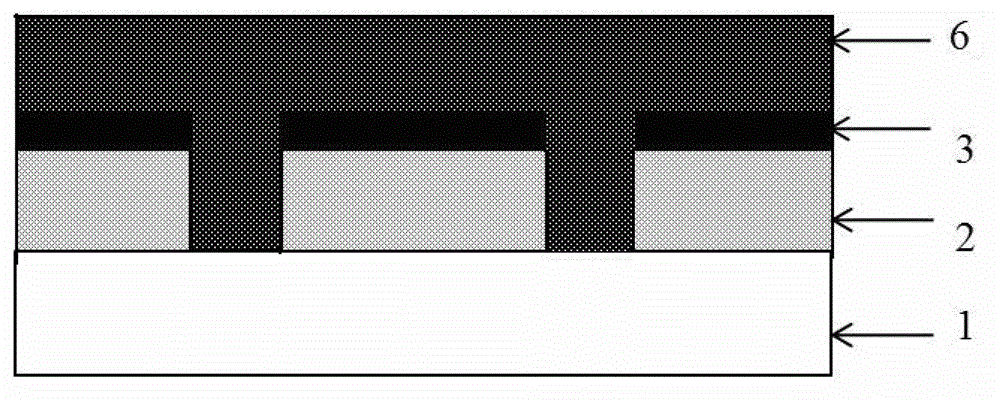

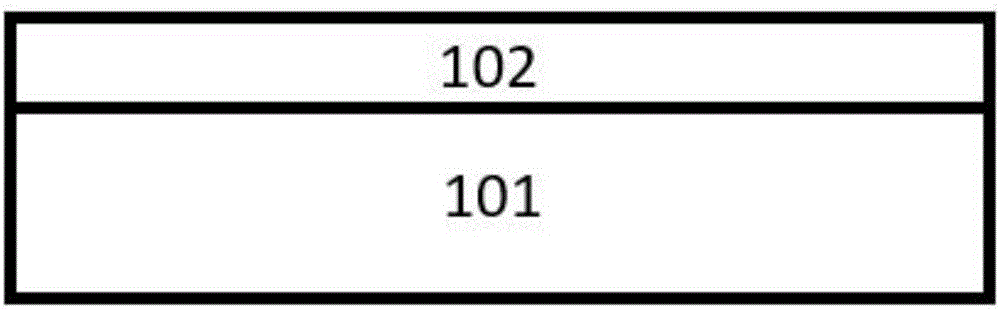

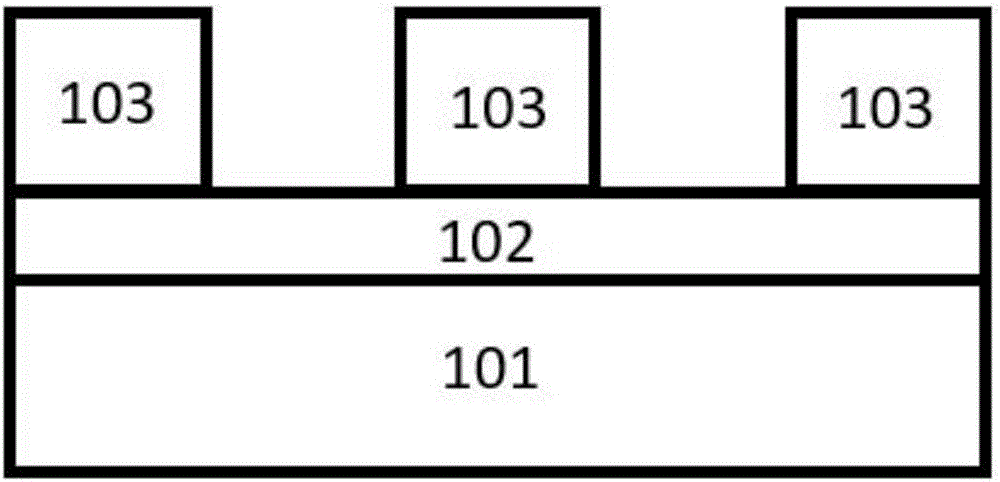

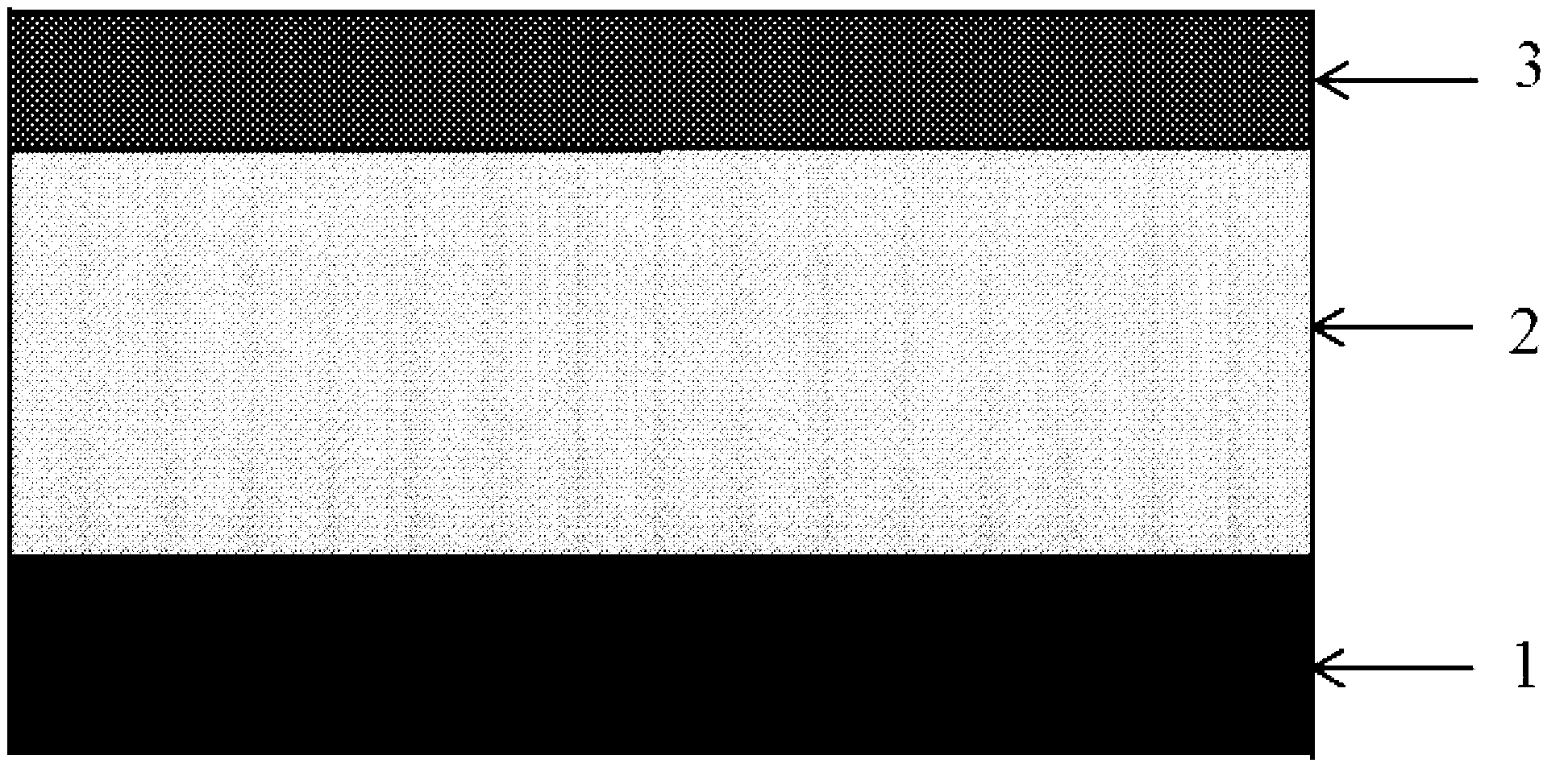

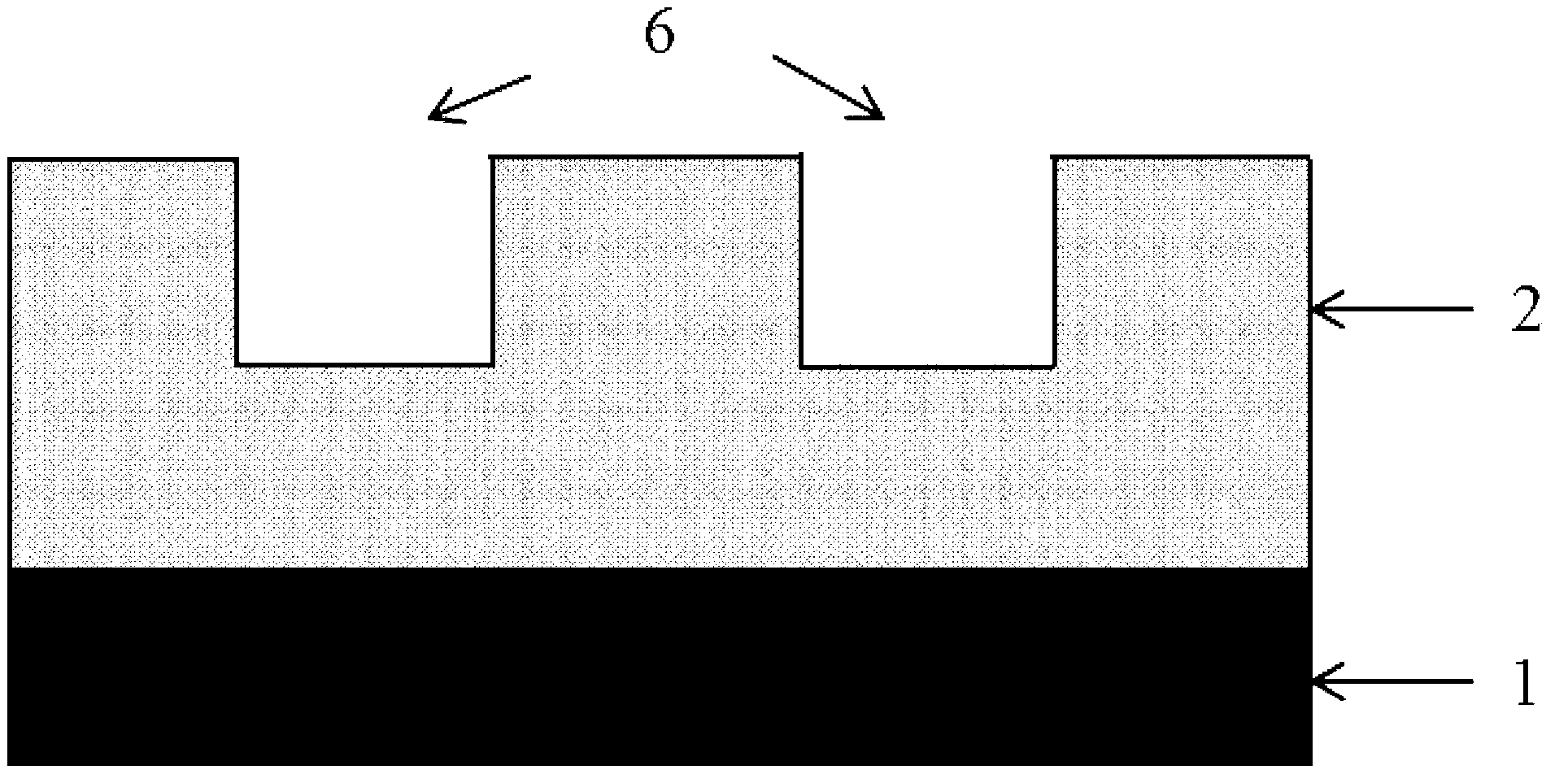

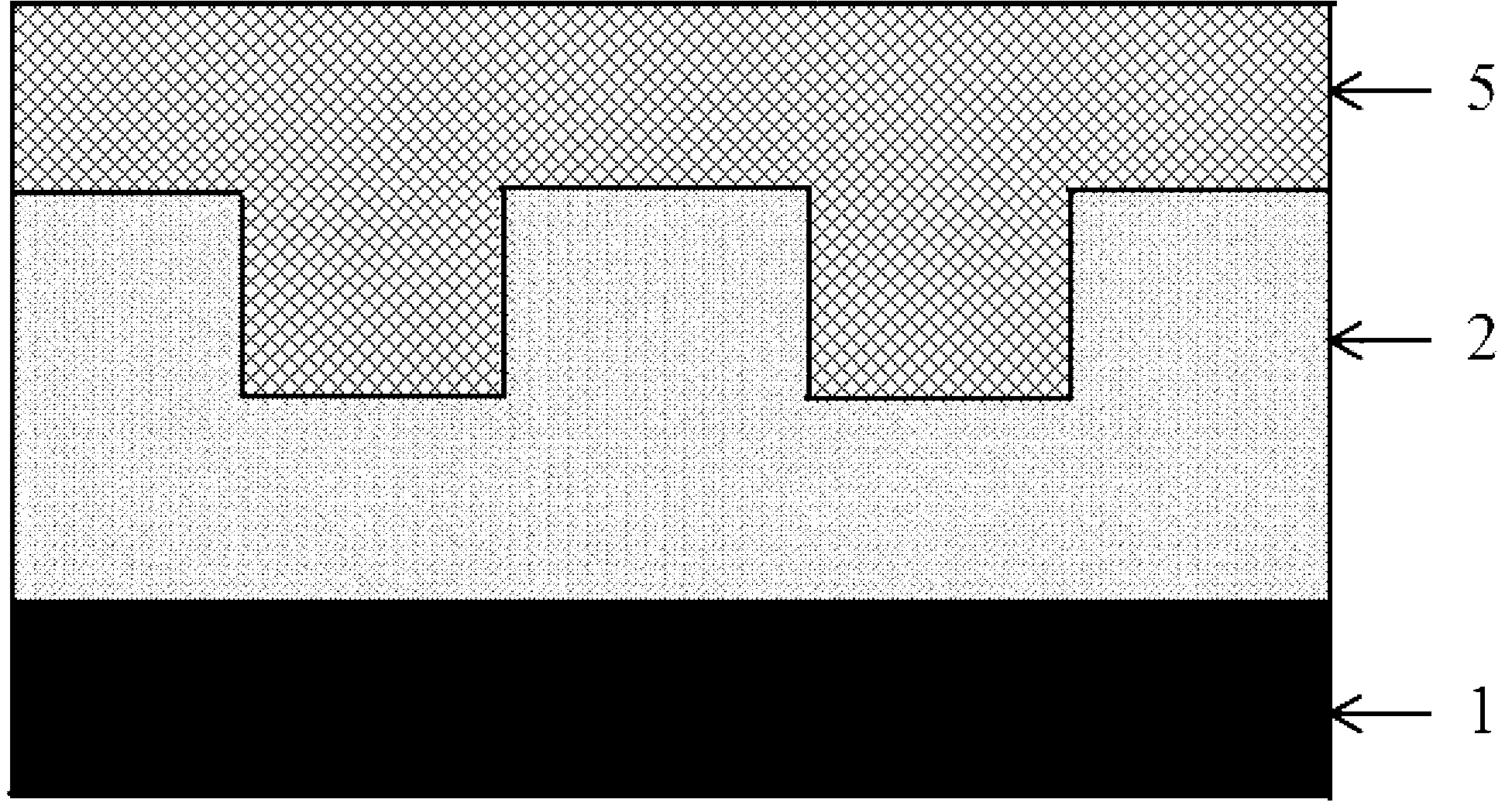

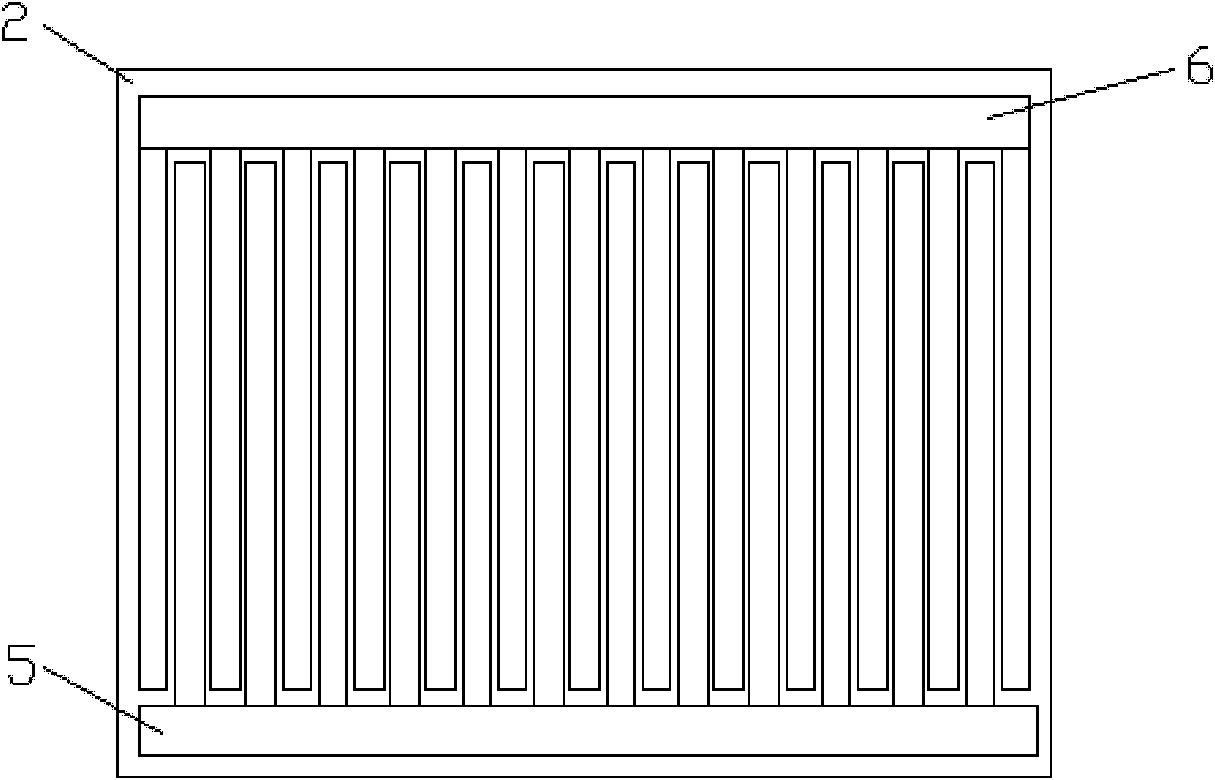

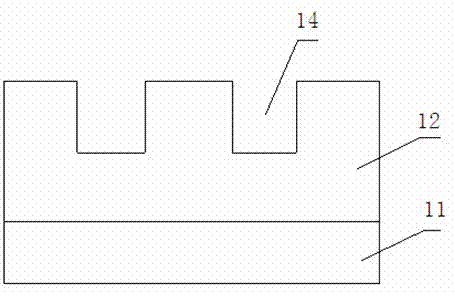

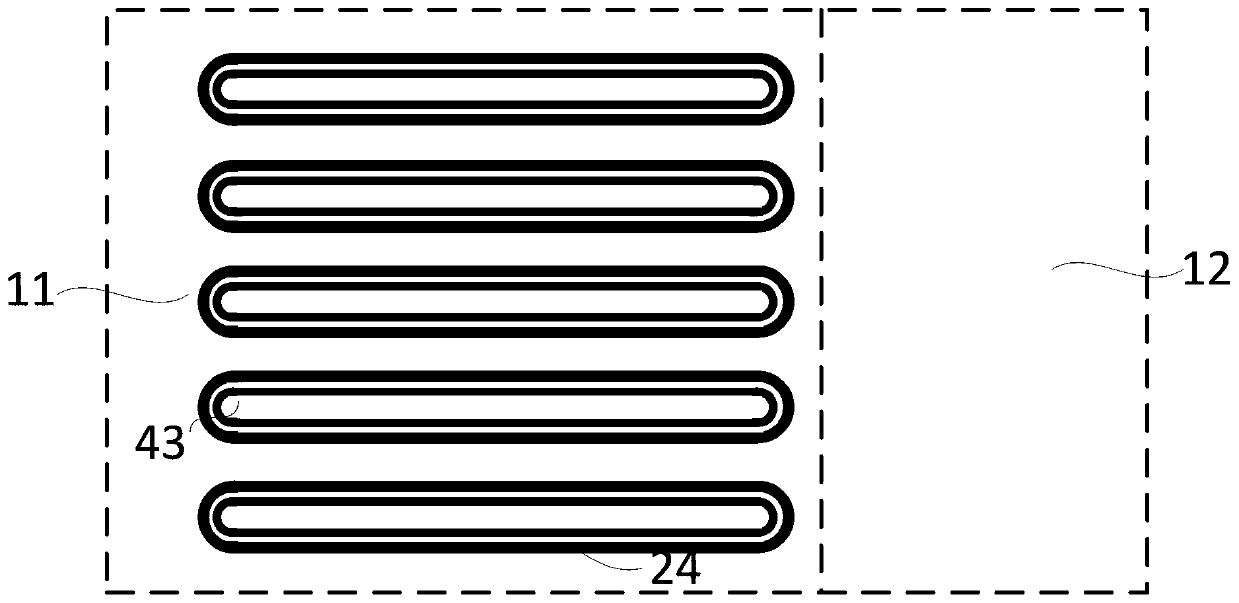

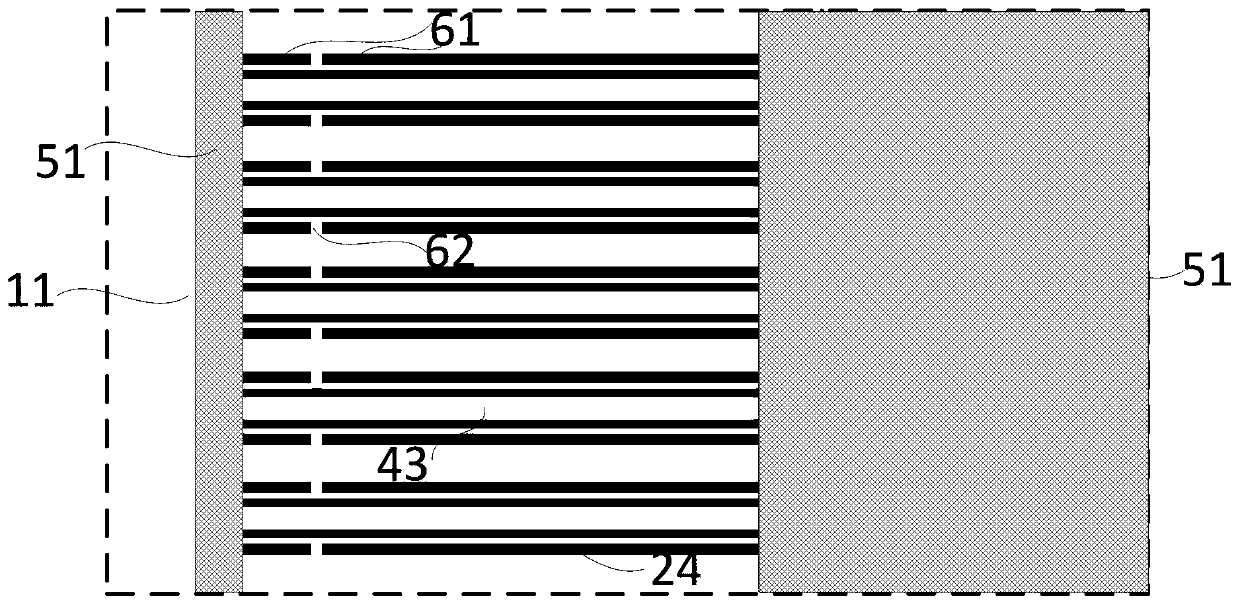

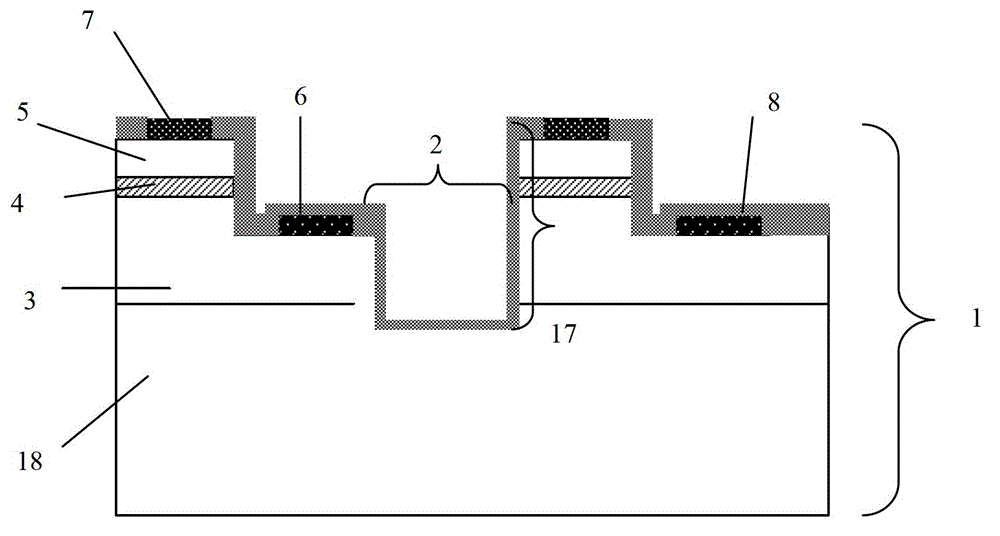

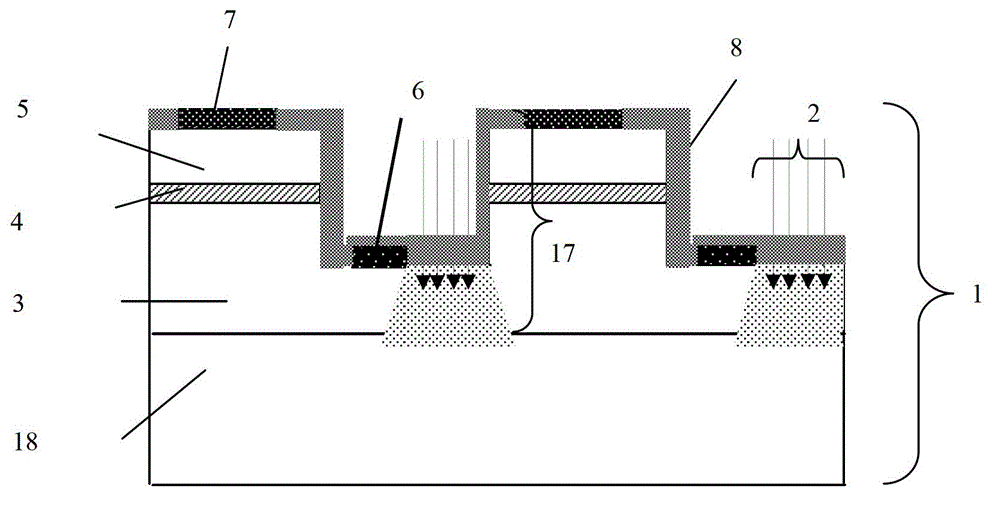

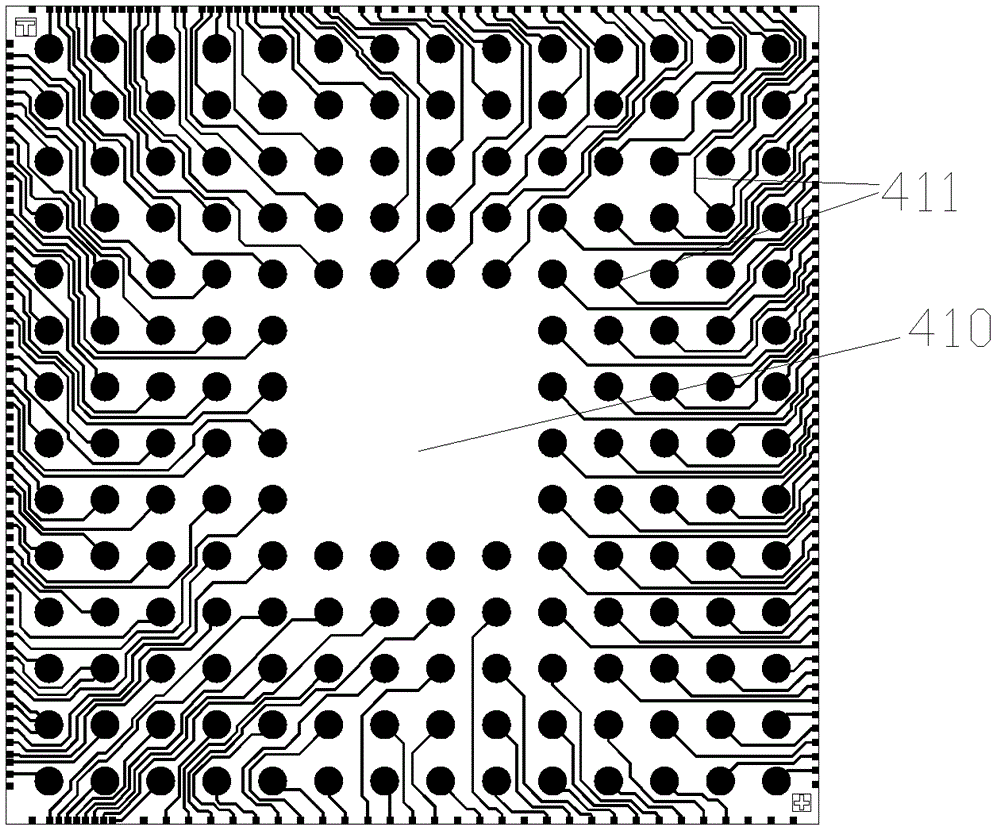

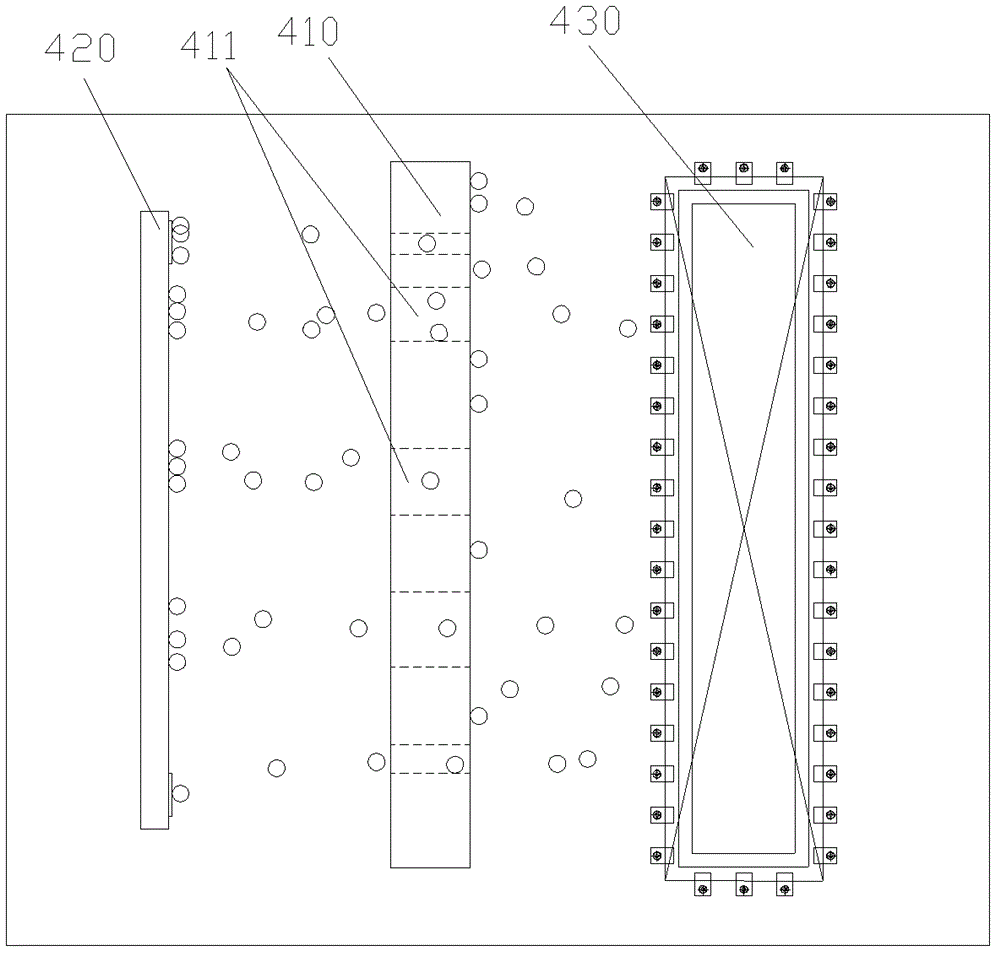

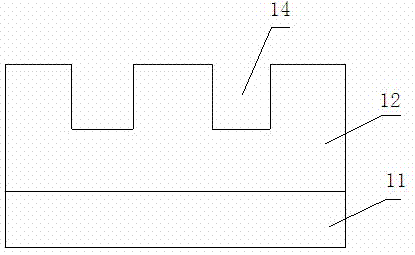

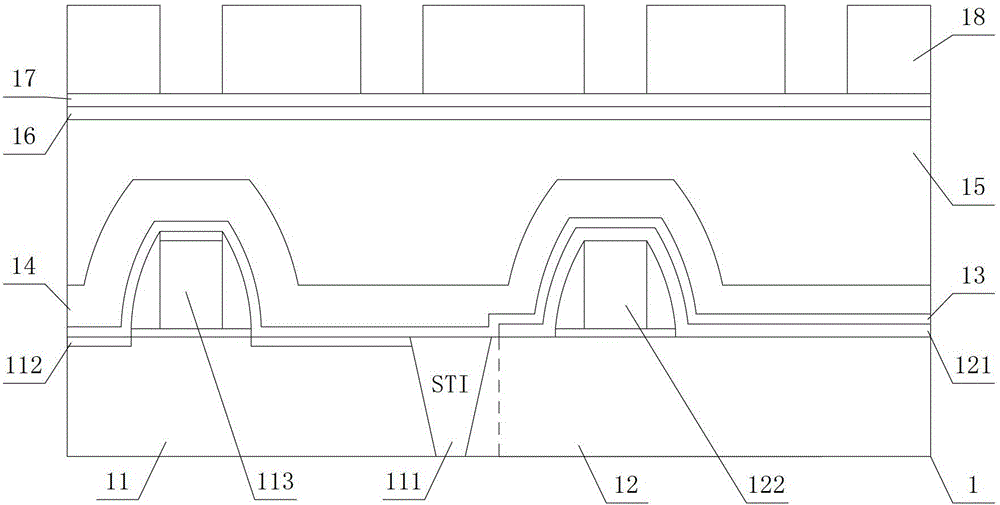

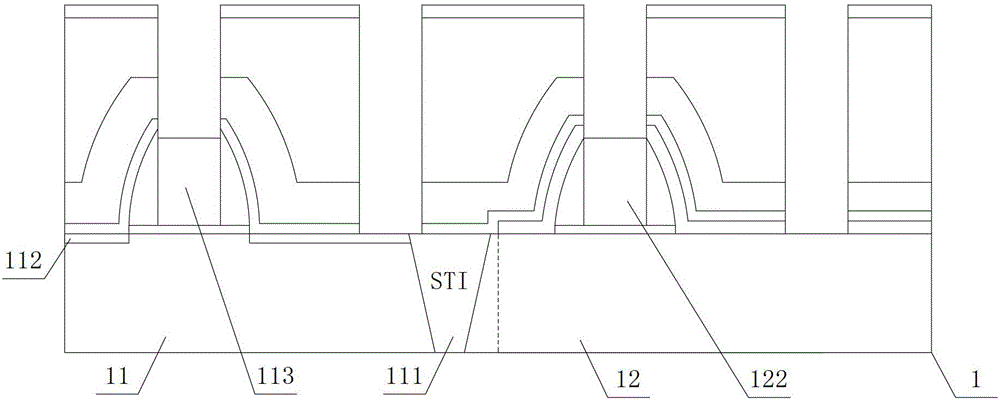

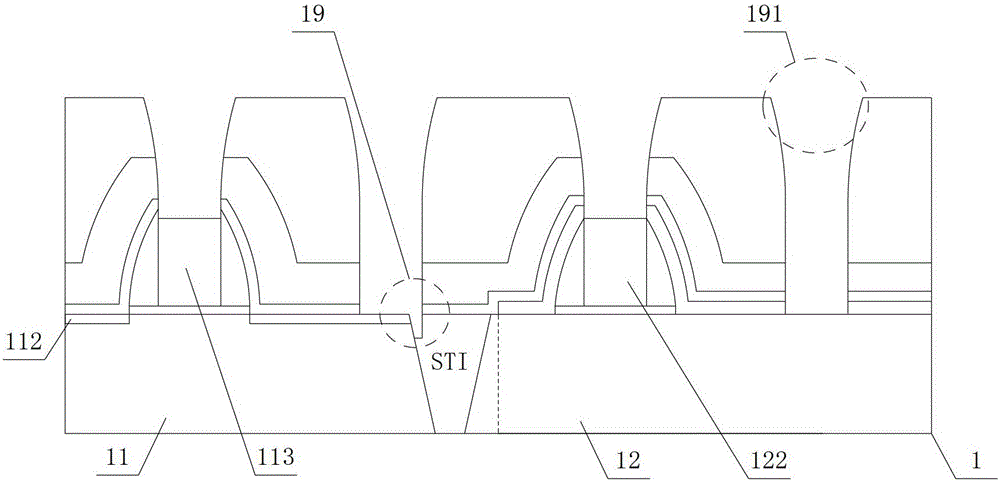

The invention relates to the field of MOS (Metal Oxide Semiconductor) devices, particularly to a double-structure contact hole synchronous-etching technology. The silicon nitride barrier layer in a photosensitive area is removed immediately after a silicon nitride barrier layer is deposited, so that the deposit layer structure of a double-structure contact hole of a CIS (Complementary Metal Oxide Semiconductor Image Sensor) product is changed; the etching selection ratio of an interlayer dielectric layer (insulating dielectric layer) to the barrier layer and a silicone substrate is enlarged in the follow-up etching technology, so that the etching step special for a monox barrier layer at the bottom of the photosensitive area is reduced, the monox loss on STI (Shallow Trench Isolation) of a borderless contact hole in a logic area is reduced while the double-structure contact hole is formed, and the yield of products is improved while the technological reliability and stability are enhanced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

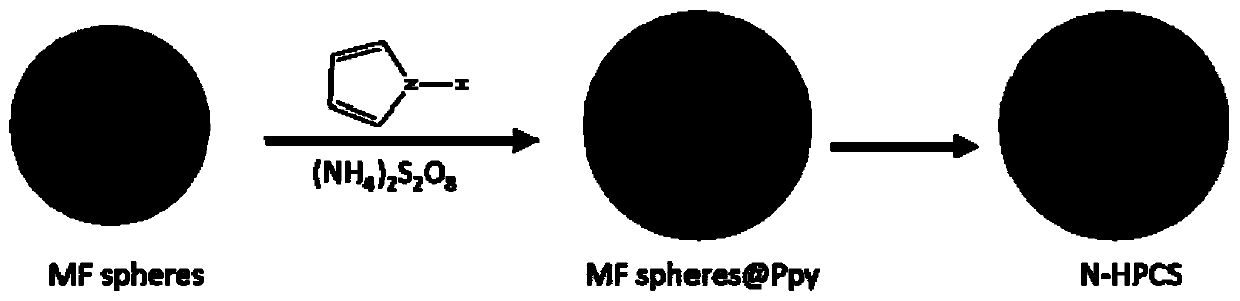

Nitrogen-doped porous hollow carbon sphere and preparation method and application thereof

PendingCN110729480AEliminate the etching stepFewer etch stepsSecondary cellsNegative electrodesPtru catalystPolypyrrole

Melamine resin pellets are obtained through one-step condensation of melamine and formaldehyde, the melamine resin pellets used as templates are coated with polypyrrole by using pyrrole as a nitrogensource and a carbon source and ammonium persulfate as a catalyst; the melamine resin pellets are gradually decomposed in the roasting process by controlling roasting to obtain nitrogen-doped porous hollow carbon spheres; and finally, the material is used in a lithium ion battery negative electrode. By using the melamine resin pellets instead of traditional silicon dioxide pellets, the problem of environmental pollution caused by etching of a silicon dioxide hard template with use of toxic reagents such as hydrofluoric acid in a traditional hard template method is avoided. Because the melamineresin pellets can generate a large amount of gas in the decomposition process, pores can be further formed in the pore walls of the hollow carbon spheres. Because the material is uniform in morphology, large in specific surface area and of a hollow structure, volume expansion can be relieved, and high specific capacity and cycle stability are shown in the lithium ion battery.

Owner:NANKAI UNIV

ESD (electro-static discharge) structure of trench type MOSFET and technological method

ActiveCN105355626AReduce depositionFewer etch stepsSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETBody region

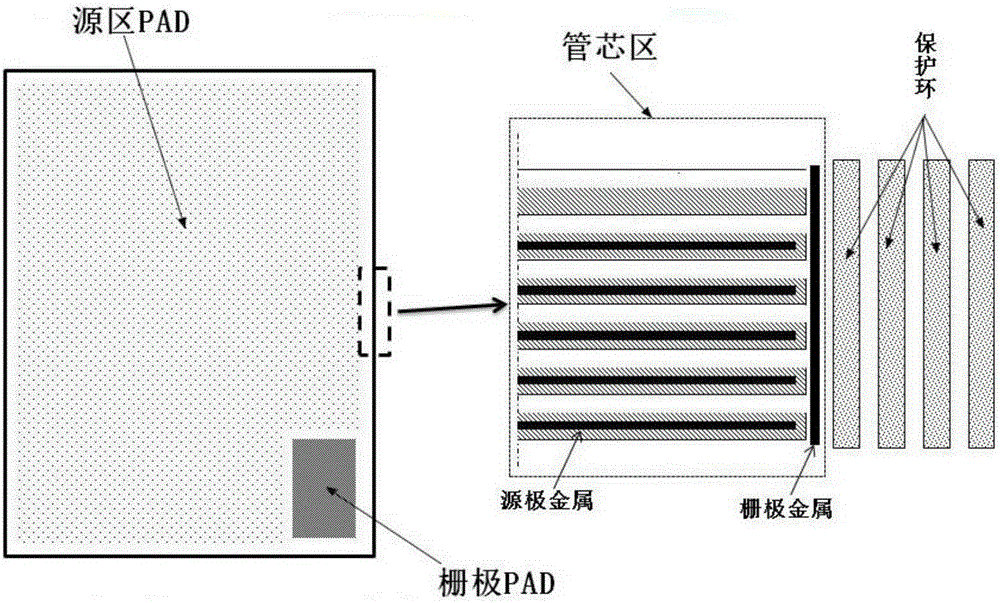

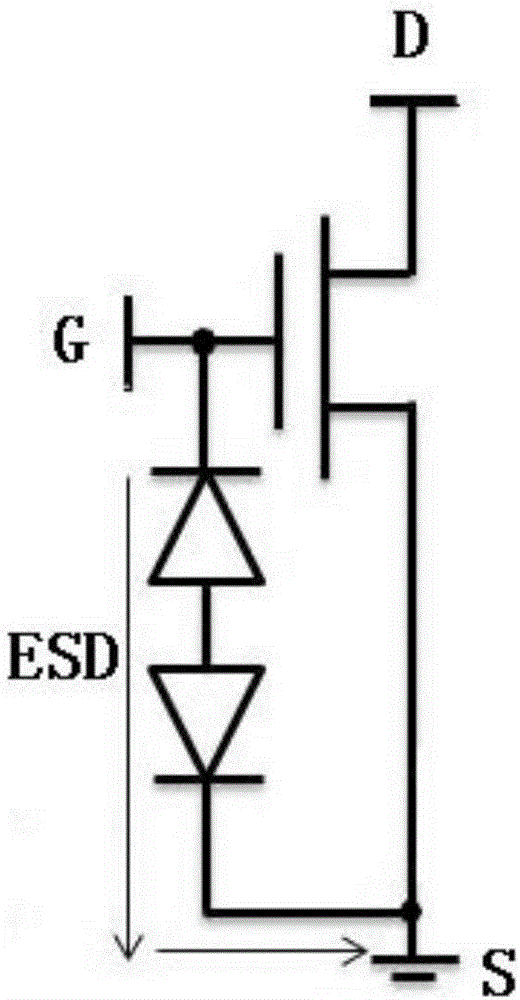

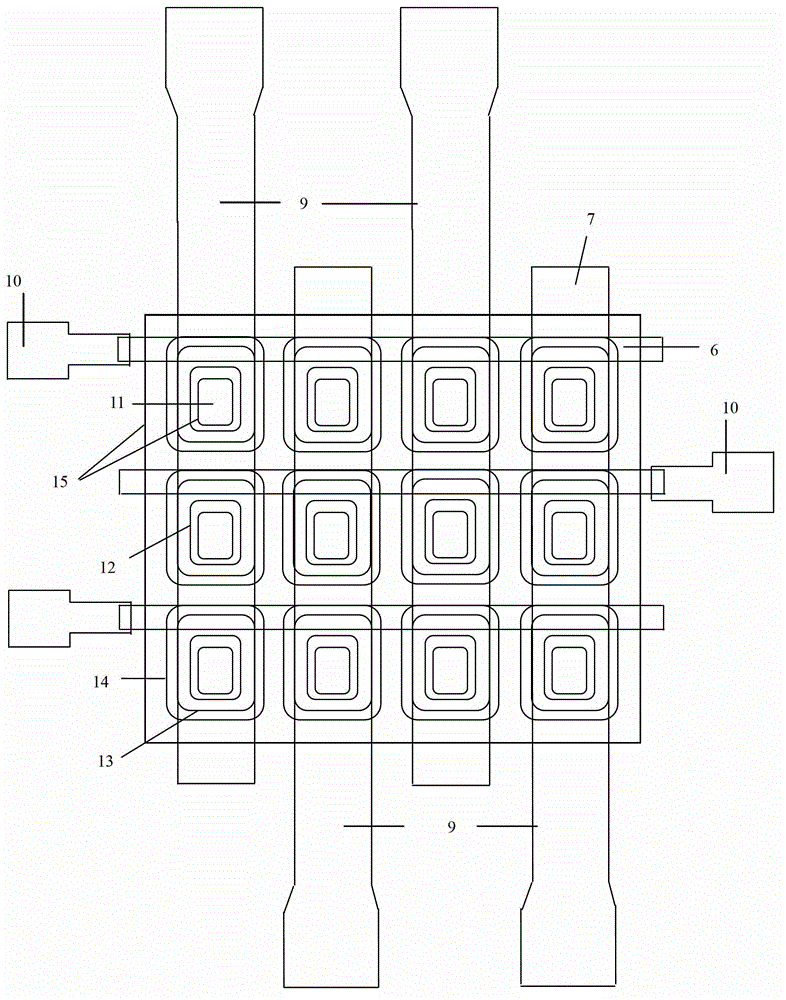

The invention discloses an integrated ESD (electro-static discharge) structure of a trench type MOSFET; a trench type protective ring is arranged around the trench type MOSFET; the ESD structure is integrated in a protective ring trench; the protective ring trench passes through the bottom of a body region to be positioned in an epitaxial layer; the trench is filled with polycrystalline silicon; the polycrystalline silicon is subjected into interval doping in subsections of N-P or P-N, or N-P- until -N-P or P-N- until -P-N to form one or more equivalently concatenated diodes; and the electrodes in the first ends and the tail ends of the concatenated diodes are connected with the grid electrode and the source electrode of the trench type MOSFET respectively. According to the ESD structure of the trench type MOSFET, the polycrystalline silicon, with the alternatively-arranged Ns and Ps at intervals, is formed in the protective ring trench to equivalently form the ESD diodes; the two electrodes of the equivalent ESD diodes formed by PN junctions are connected with the source electrode and the grid electrode of the MOSFET respectively through metal leads to form the ESD protection structure of the MOSFET. According to the technological method for the ESD structure of the trench type MOSFET, by the adoption of the protective ring, the procedures of ESD polycrystalline silicon depositing and etching are reduced, so that the processing steps are simplified and the cost is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

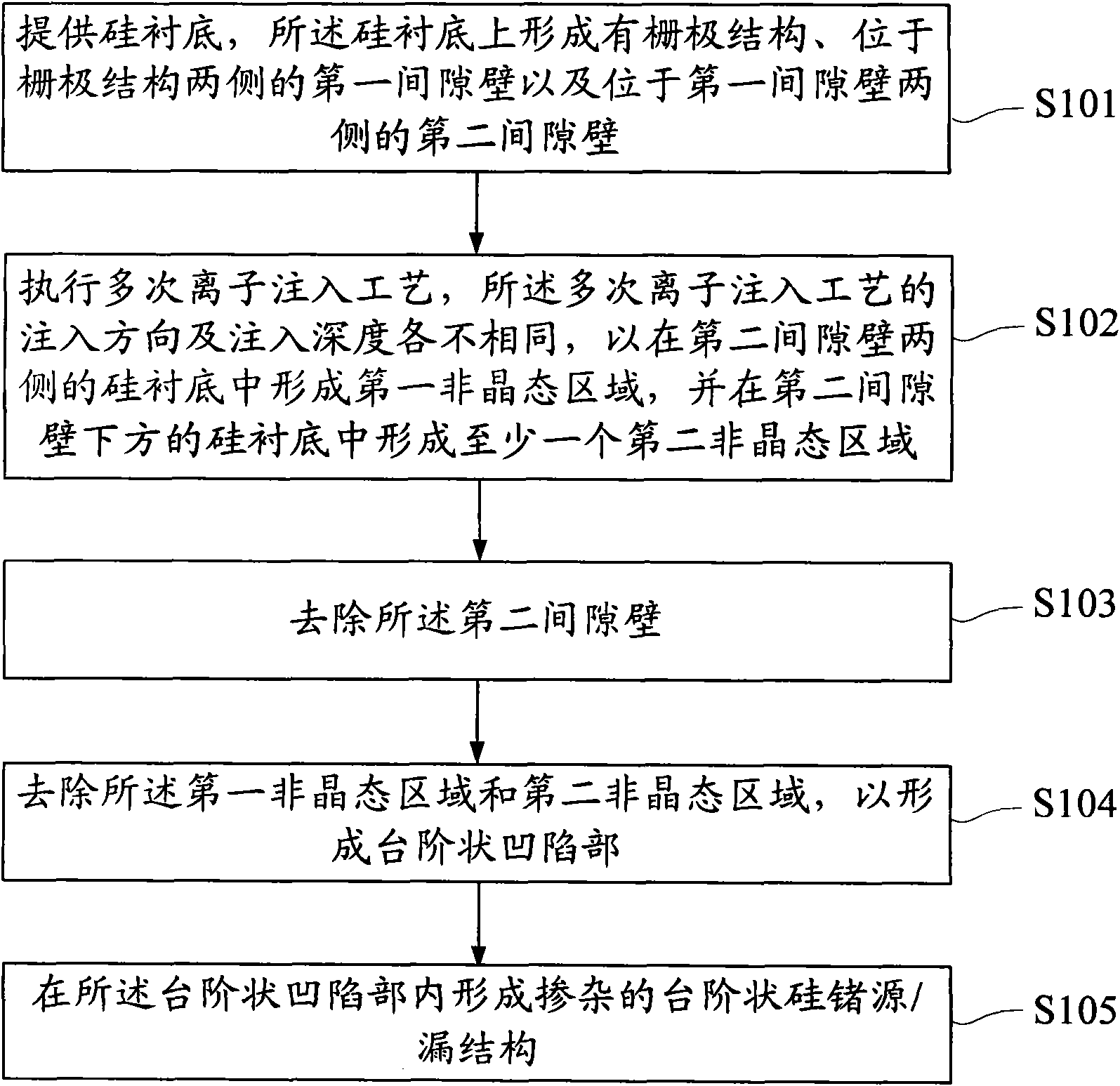

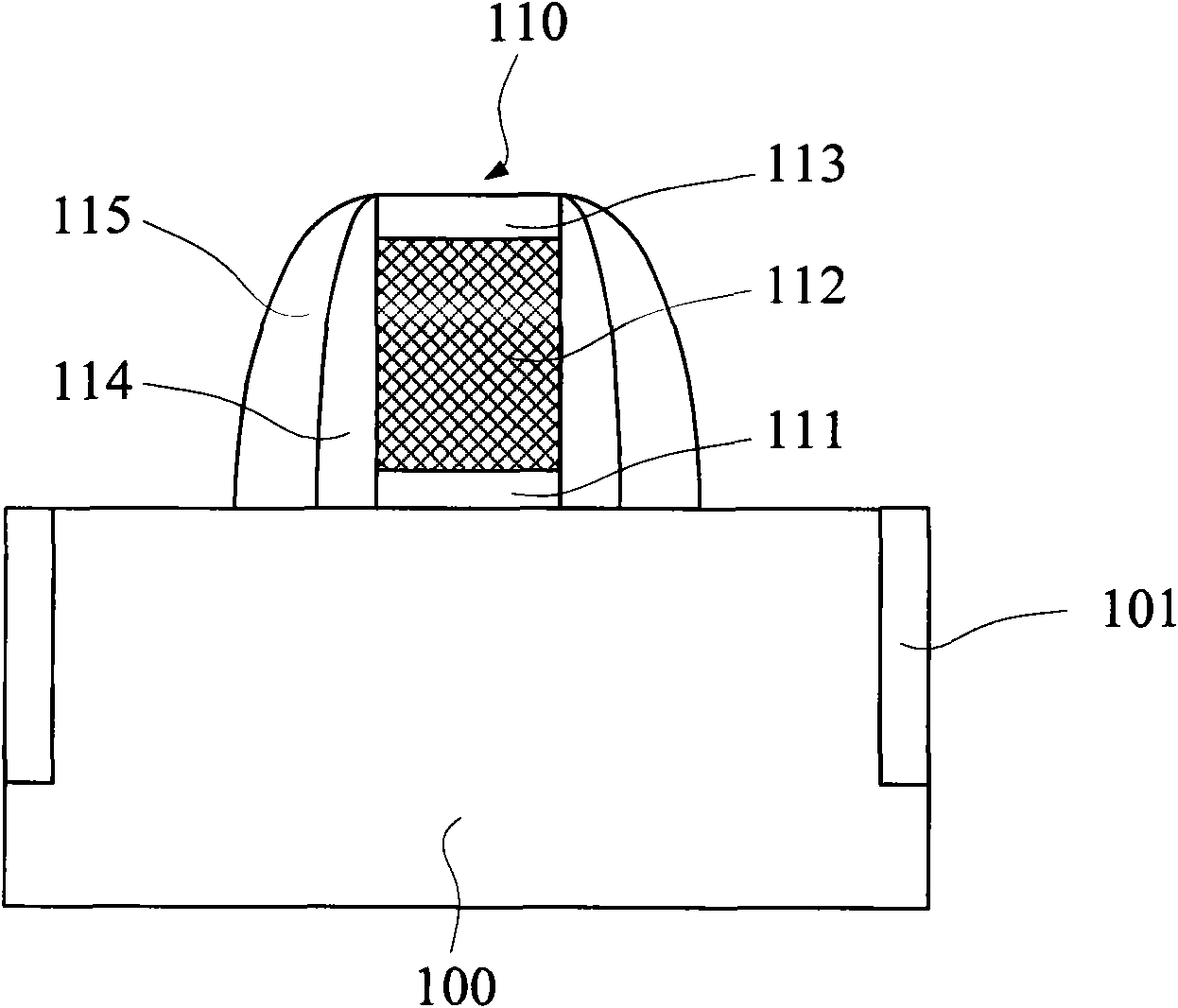

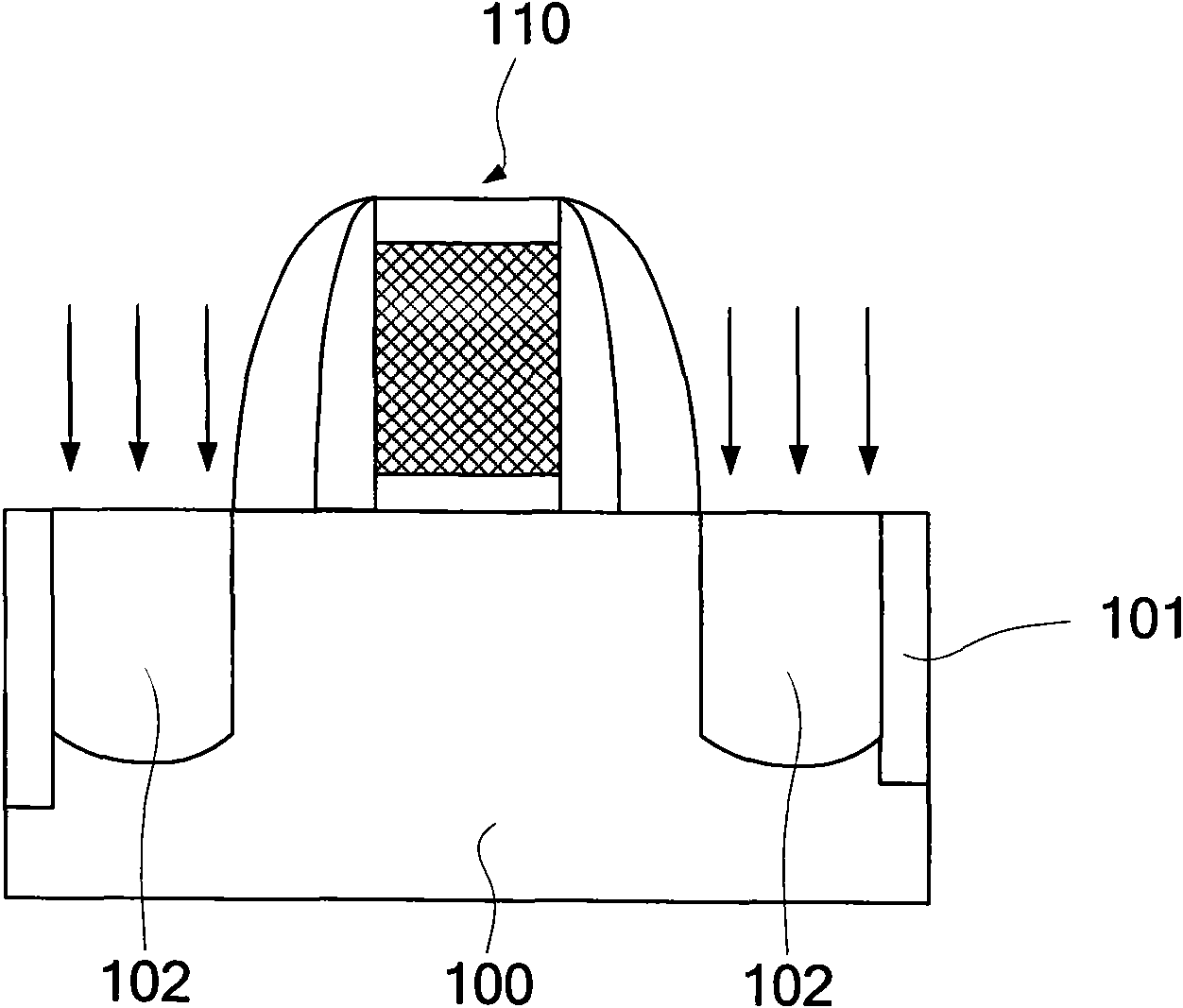

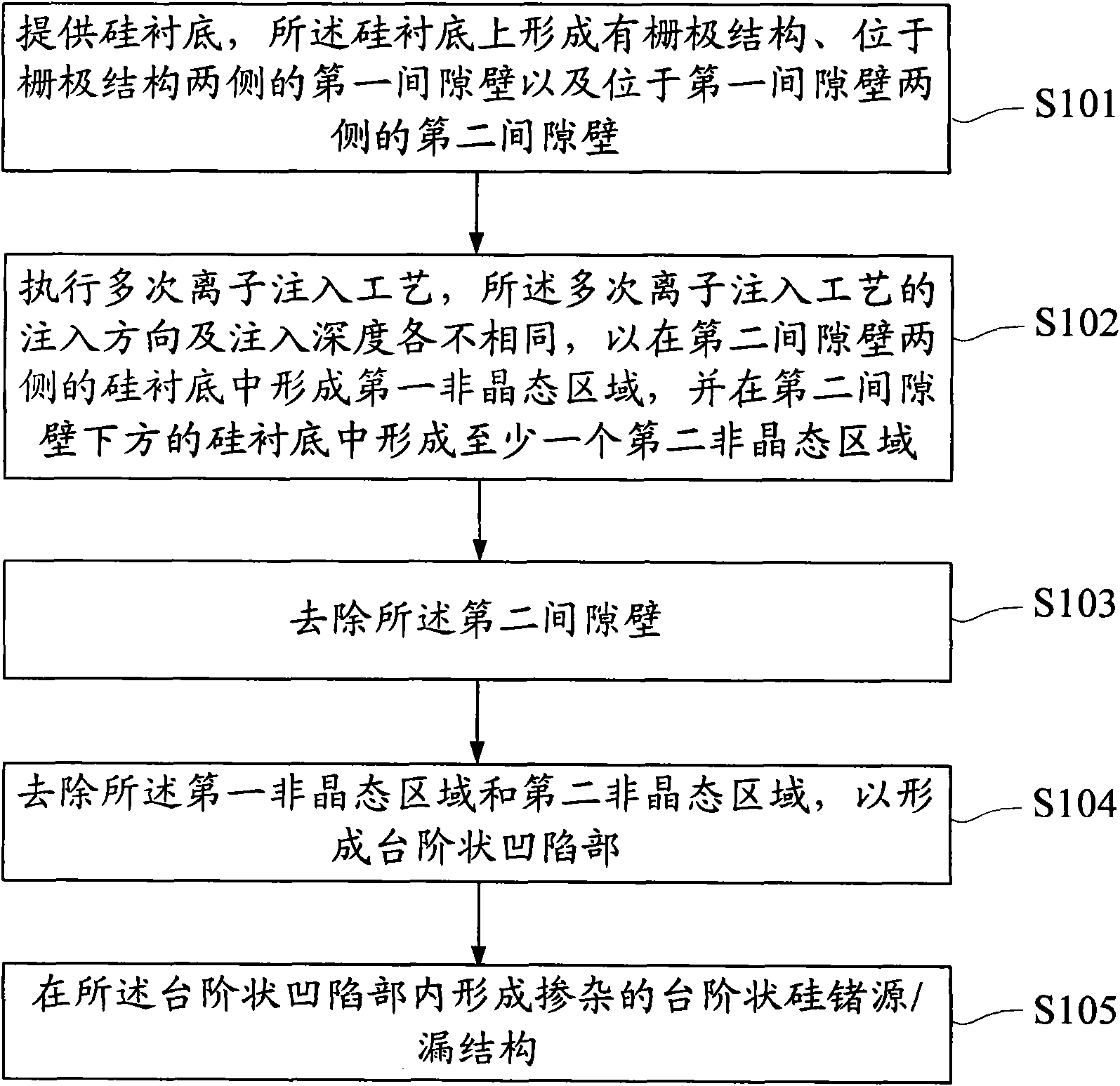

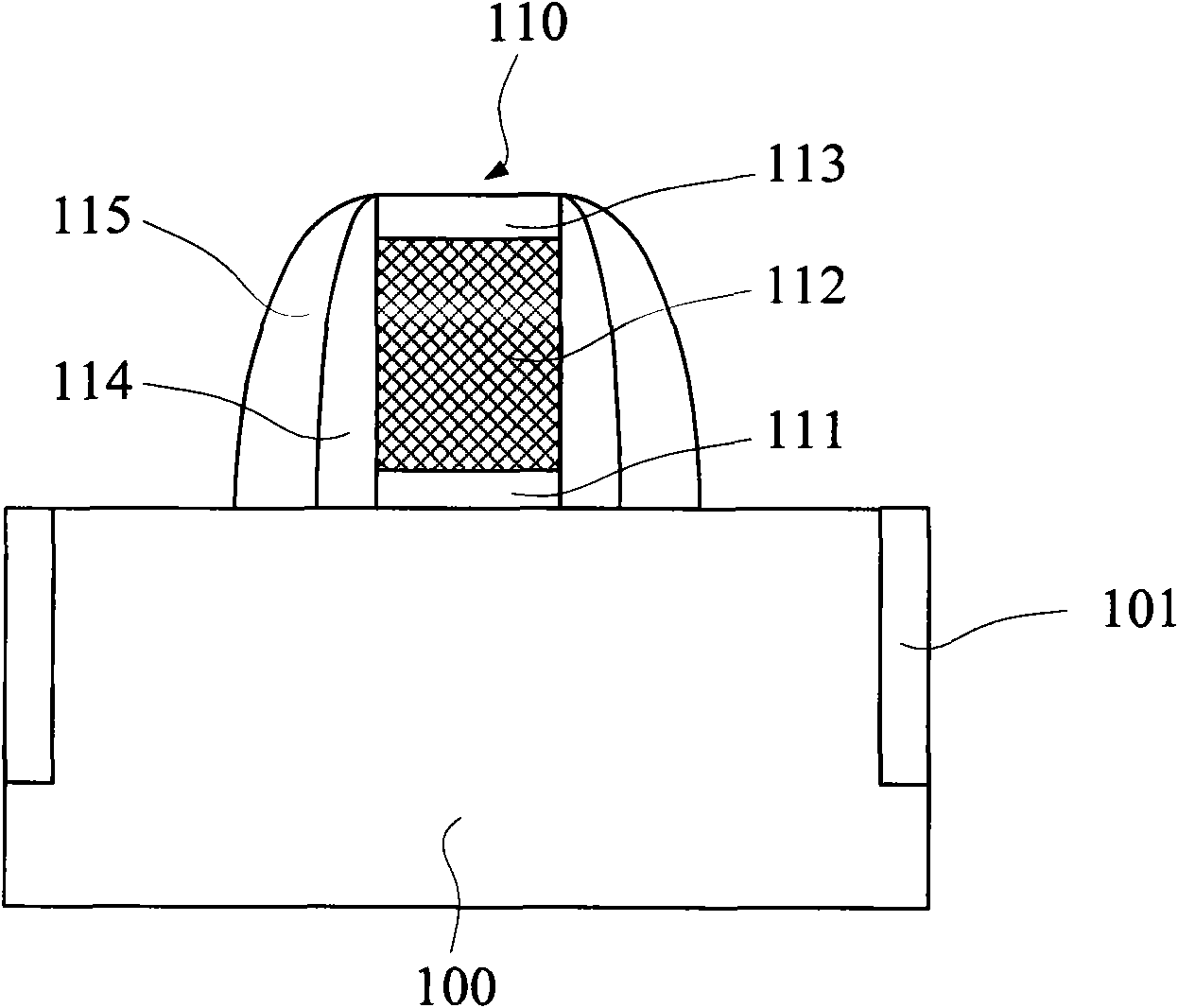

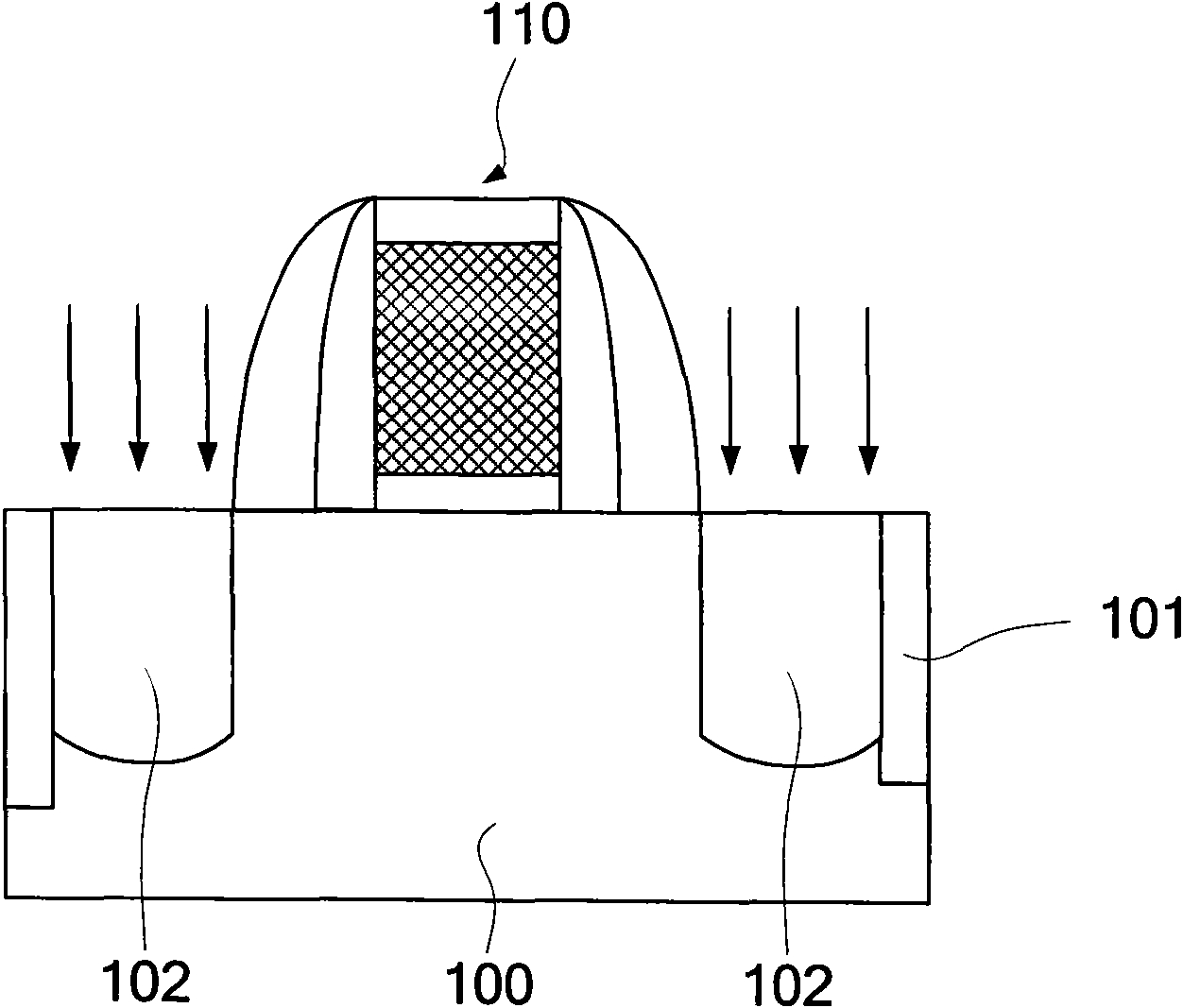

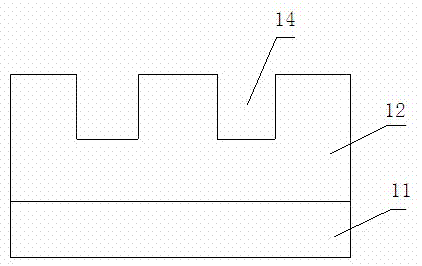

Manufacturing method for stepped silicon germanium source/drain structures

ActiveCN102403227ADepth is easy to controlShape is easy to controlSemiconductor/solid-state device manufacturingIon implantationSilicon-germanium

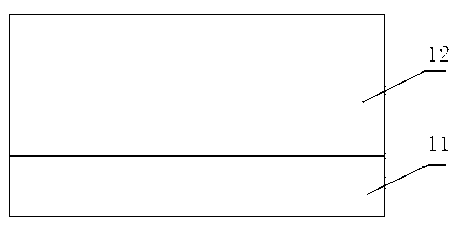

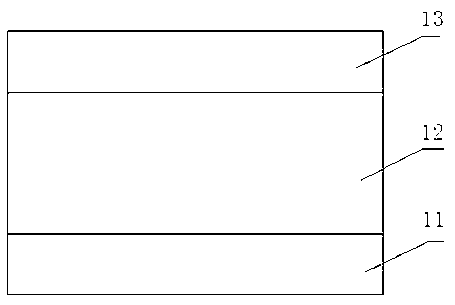

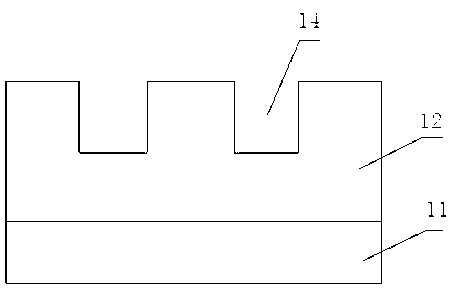

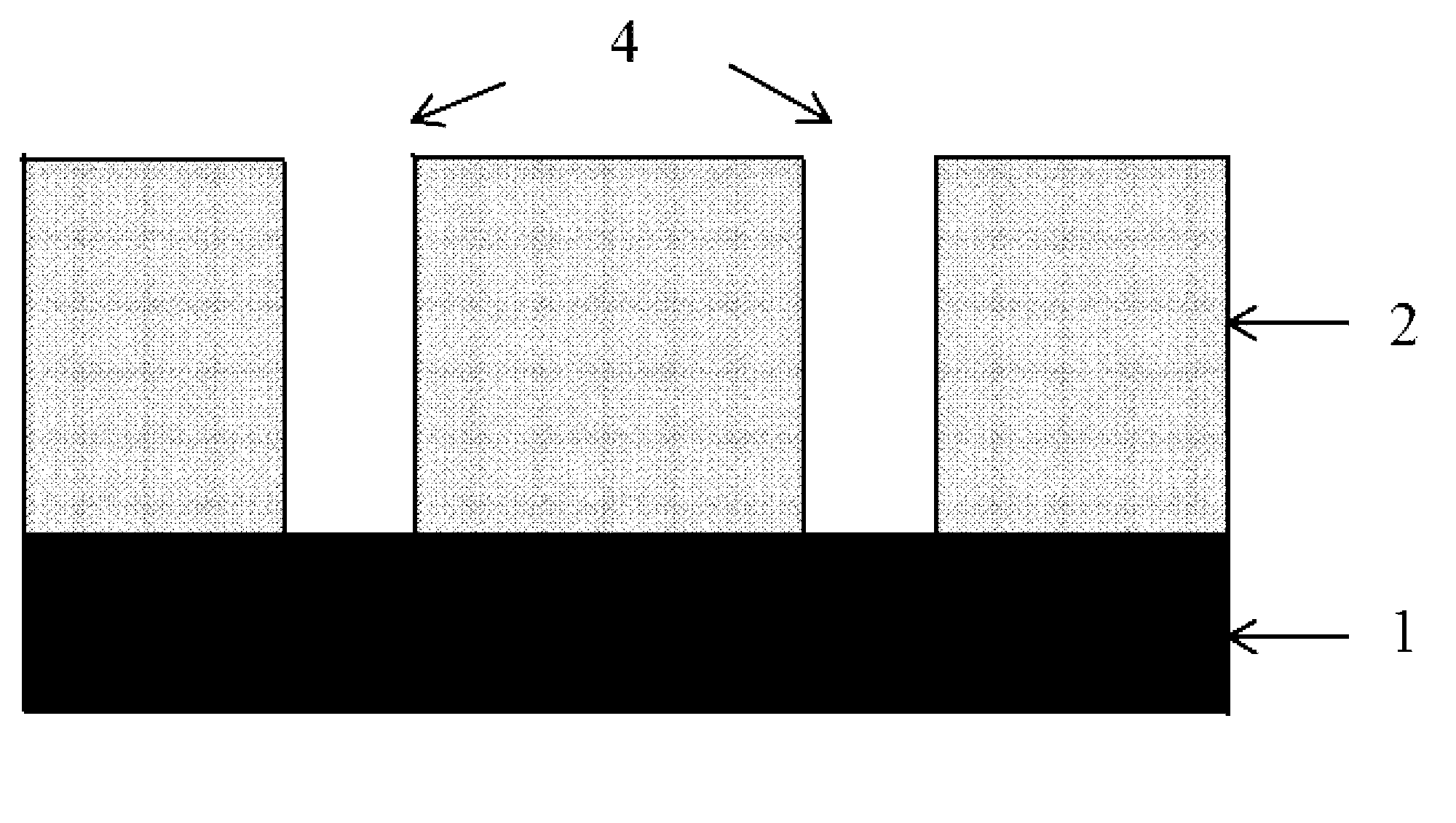

The invention provides a manufacturing method for stepped silicon germanium source / drain structures, which includes firstly, providing a silicon substrate, wherein a grid structure, first gap walls on two sides of the grid structure and second gap walls on two sides of each first gap wall are formed on the silicon substrate, secondly, performing multiple times of ion implantation technology by different directions and depths to form a first amorphous state region in the silicon substrate on two sides of each second gap wall and form at least one second amorphous state region in the silicon substrate below the second gap walls, thirdly, removing the second gap walls, fourthly, removing the first amorphous state regions and the second amorphous state regions to form a stepped recess, and fifthly, forming a doped stepped silicon germanium source / drain structure in the stepped recess. Compared with the prior art, the manufacturing method for stepped silicon germanium source / drain structures can reduce etching procedures and lower control difficulty of the etching process.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Semiconductor device manufacturing method based on double patterning

ActiveCN103779187ANo deformationSimple methodSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusSurface layerGas phase

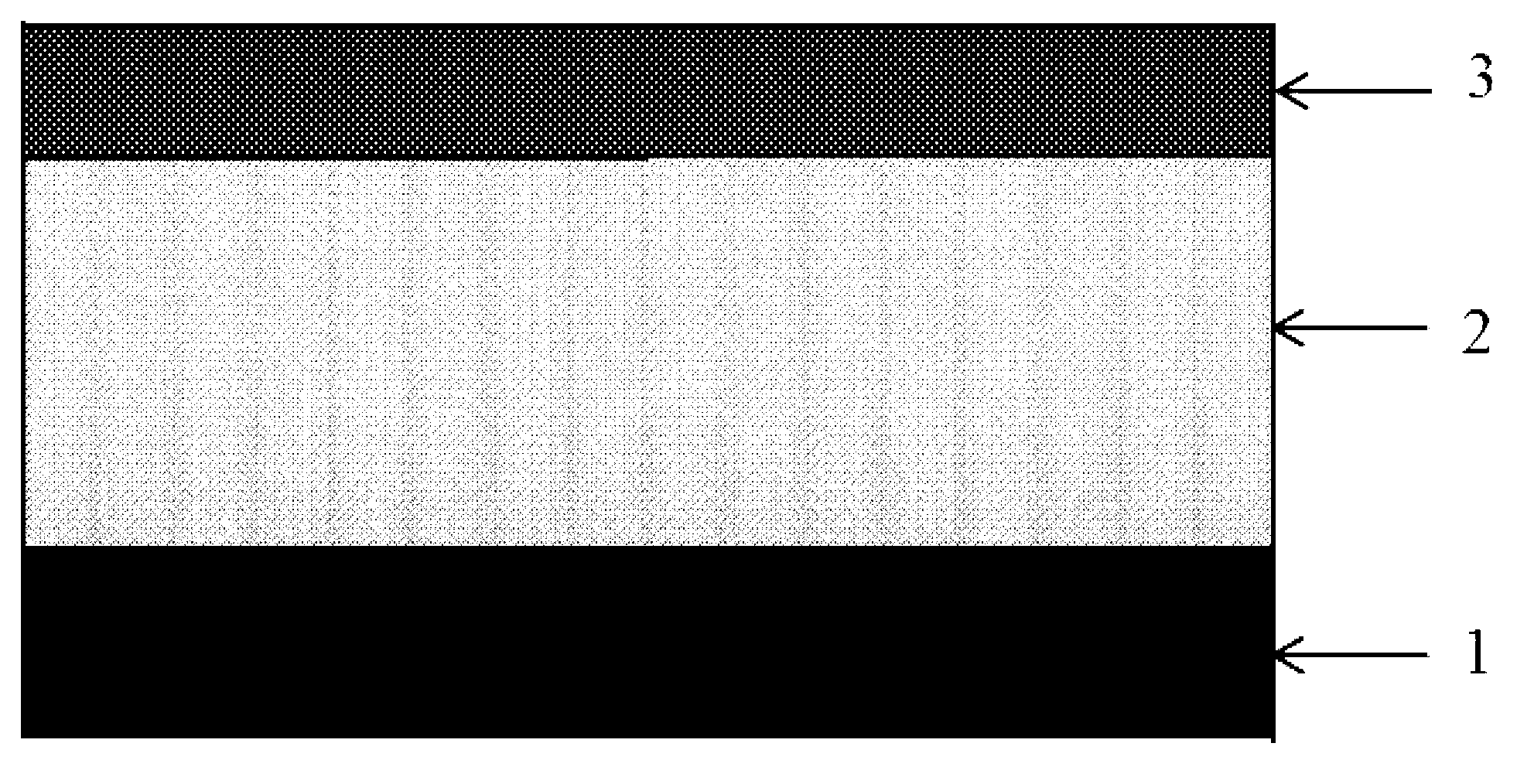

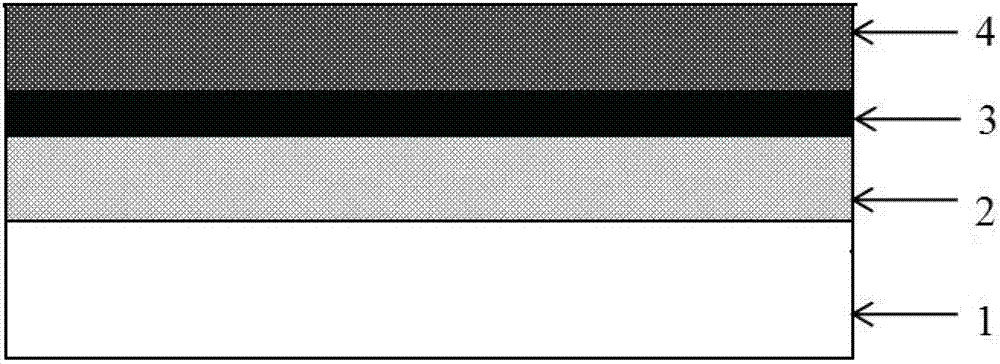

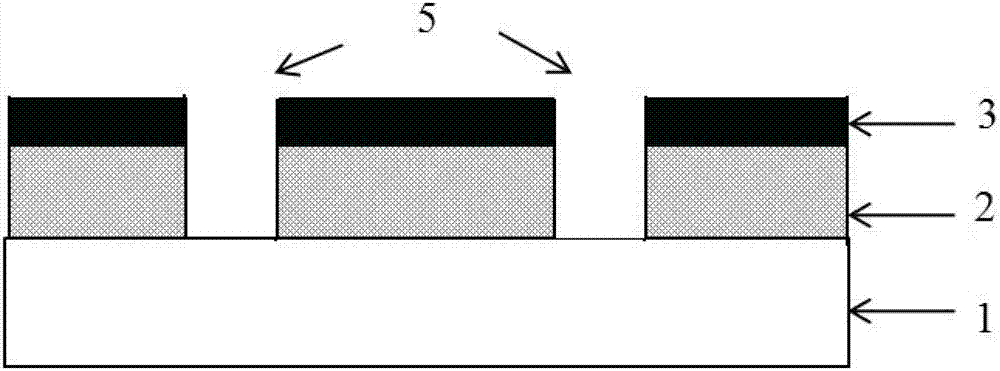

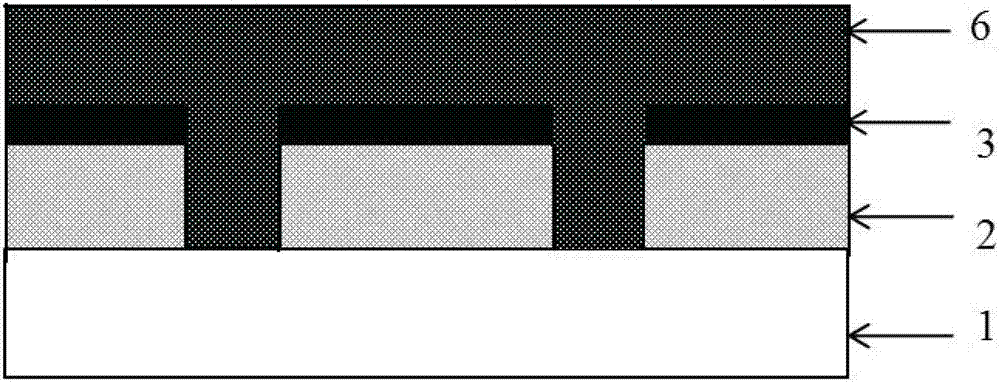

The invention relates to a semiconductor device manufacturing method based on double patterning. The method comprises the following steps: a semiconductor substrate and a mask layer located on the substrate are provided; a patterned photoresist layer is formed on the mask layer, wherein the patterned photoresist layer is photoresist cores separated through openings; a crosslinked top surface layer is formed on the patterned photoresist layer; a part of the photoresist layer sidewall is removed to thin the photoresist cores and reduce the critical size of the photoresist cores; spin coating is performed on the inner sidewall material layer, and the crosslinked top surface layer is covered; the etch back operation is performed on the inner sidewall material layer to form inner sidewalls on the photoresist cores; and the remaining crosslinked top surface layer and remaining photoresist cores are removed to form a double-patterned mask. The method of the invention is more simple, the stress problem caused by inner sidewall material chemical vapor deposition does not exist, and etch steps are reduced, so the cost is greatly reduced, and the product yield can be further improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

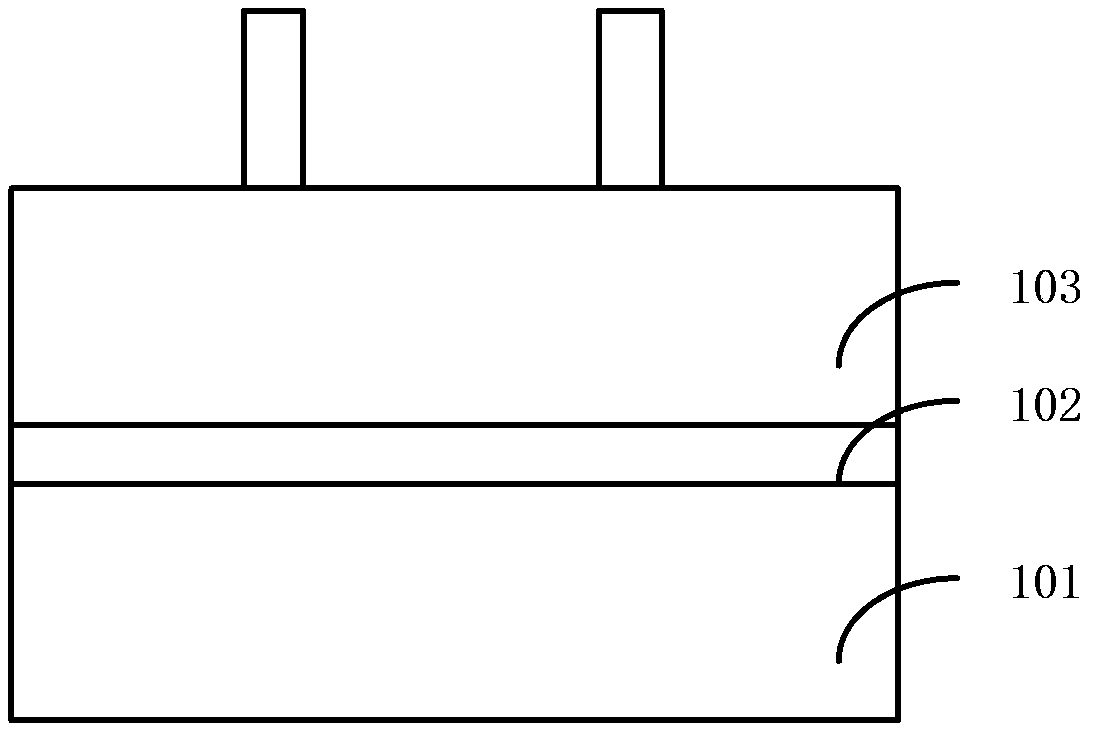

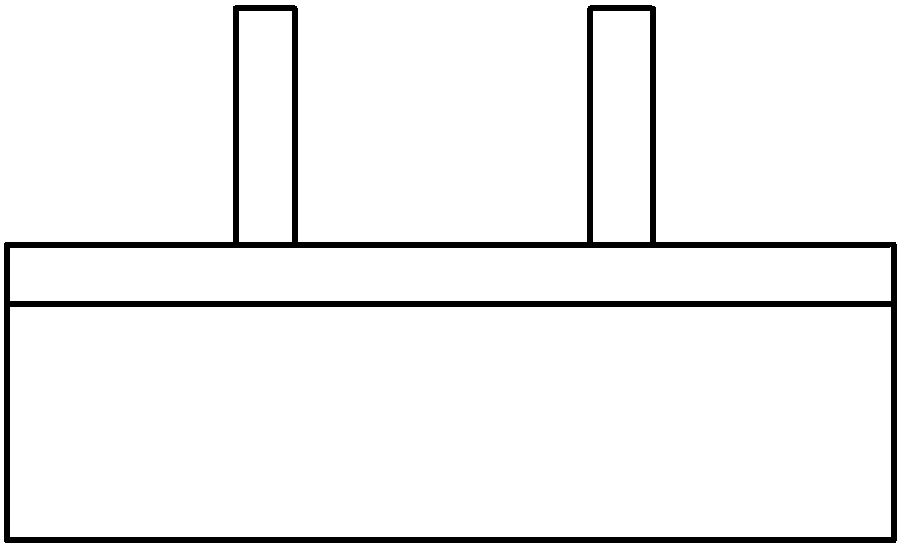

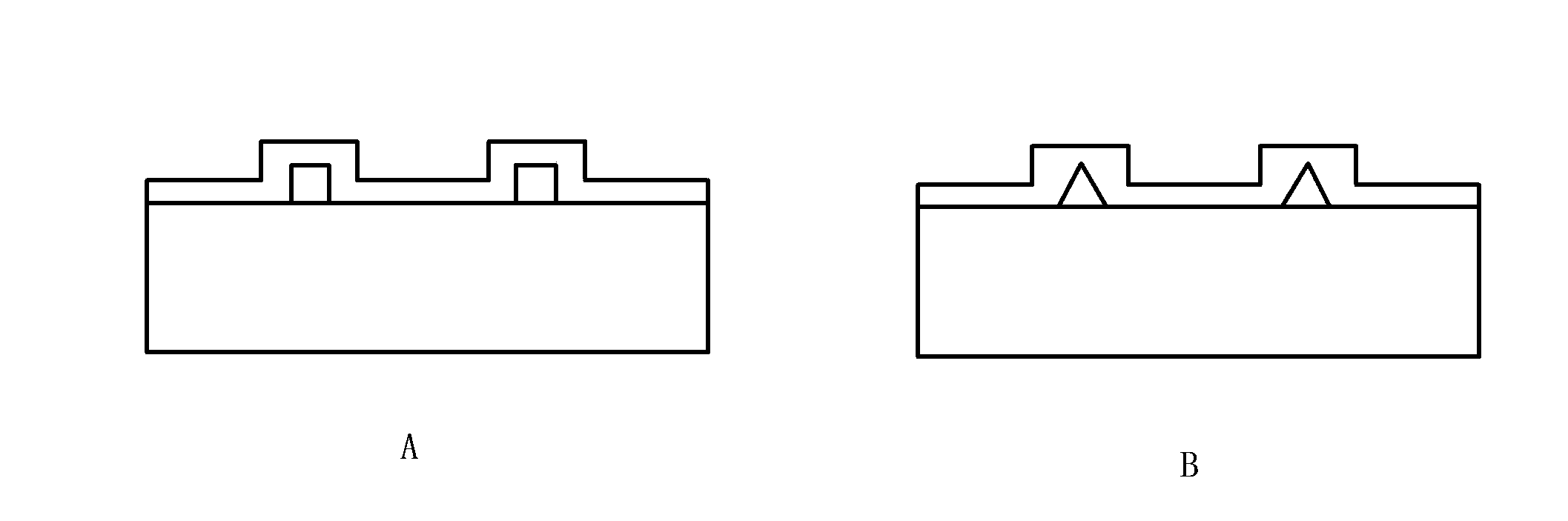

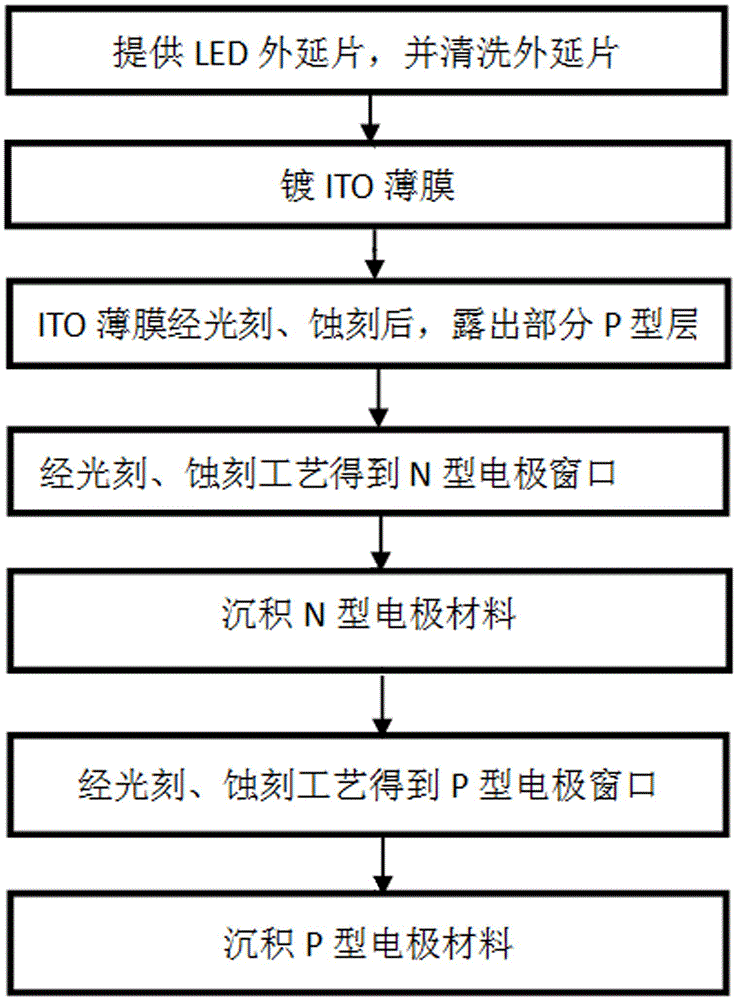

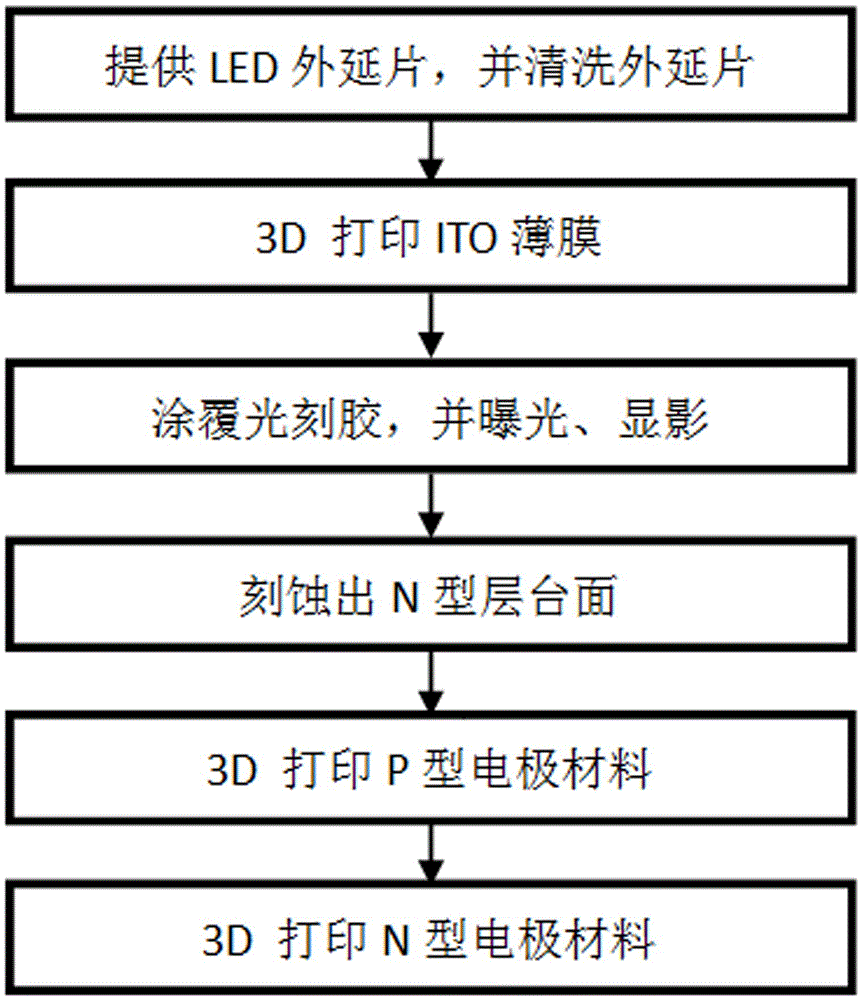

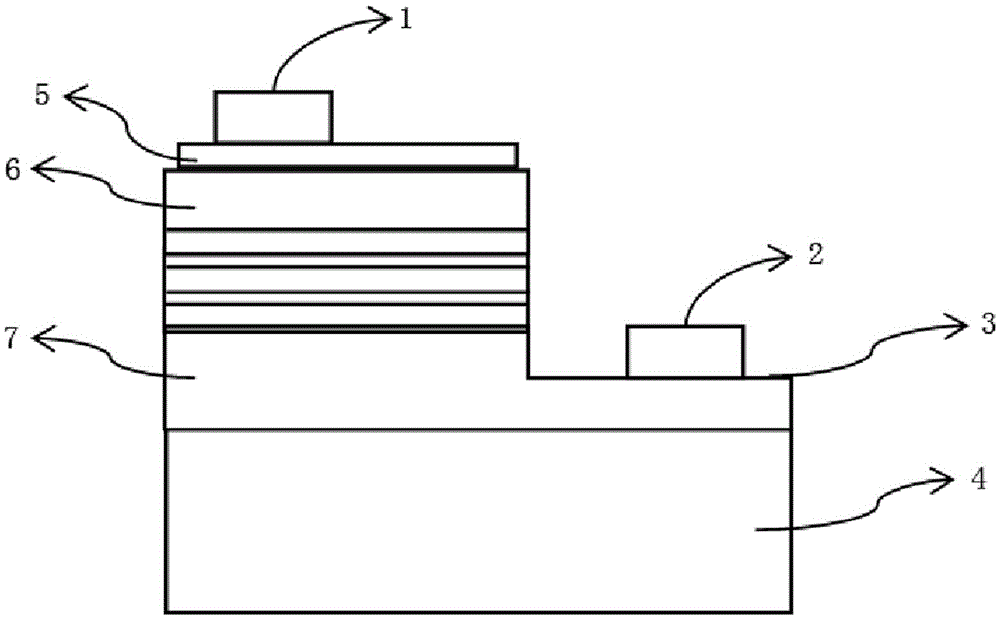

Method based on 3D printing for manufacturing LED devices

ActiveCN105576099AImprove light extraction efficiencyThe process steps are simpleSemiconductor devicesQuantum wellEngineering

The invention belongs to the photoelectron device field and particularly relates to a method based on 3D printing for manufacturing LED devices. According to the method, epitaxial wafer which at least has a buffer layer, an N-type layer, a multi-period quantum well active layer and a P-type layer and is generated by MOCVD or MBE is taken as a substrate material, an ITO conduction layer is printed on a P-type layer table top through 3D printing, an N-type layer table top is then etched, and N-type electrode and P-type electrode layers are then printed. The LED device electrode structure is formed through 3D printing, steps of photoetching and corrosion in an electrode manufacturing process can not only be reduced, the production period is shortened, pollution and damage to the epitaxial wafer in a photoetching and corrosion process can be reduced, damage of a high temperature annealing process during electrode formation to the quantum well active region interface structure can be reduced, and thereby light emitting efficiency of the LED devices can be improved.

Owner:TAIYUAN UNIV OF TECH

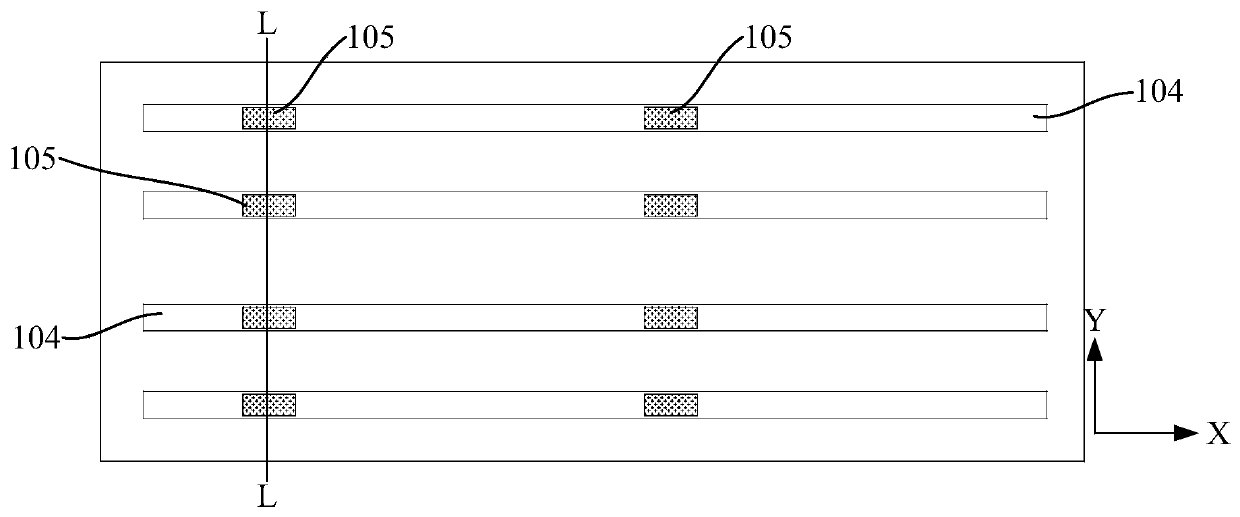

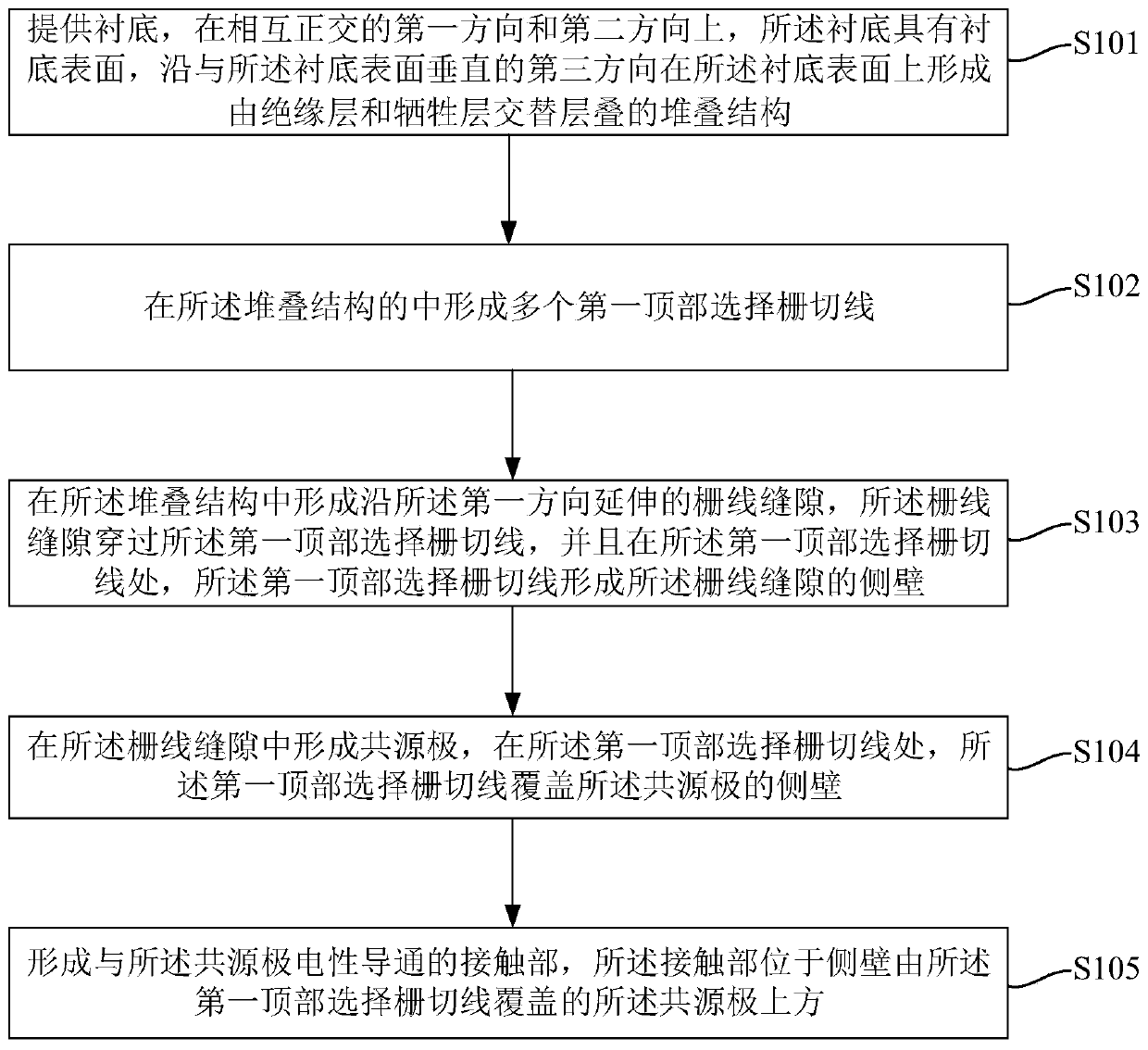

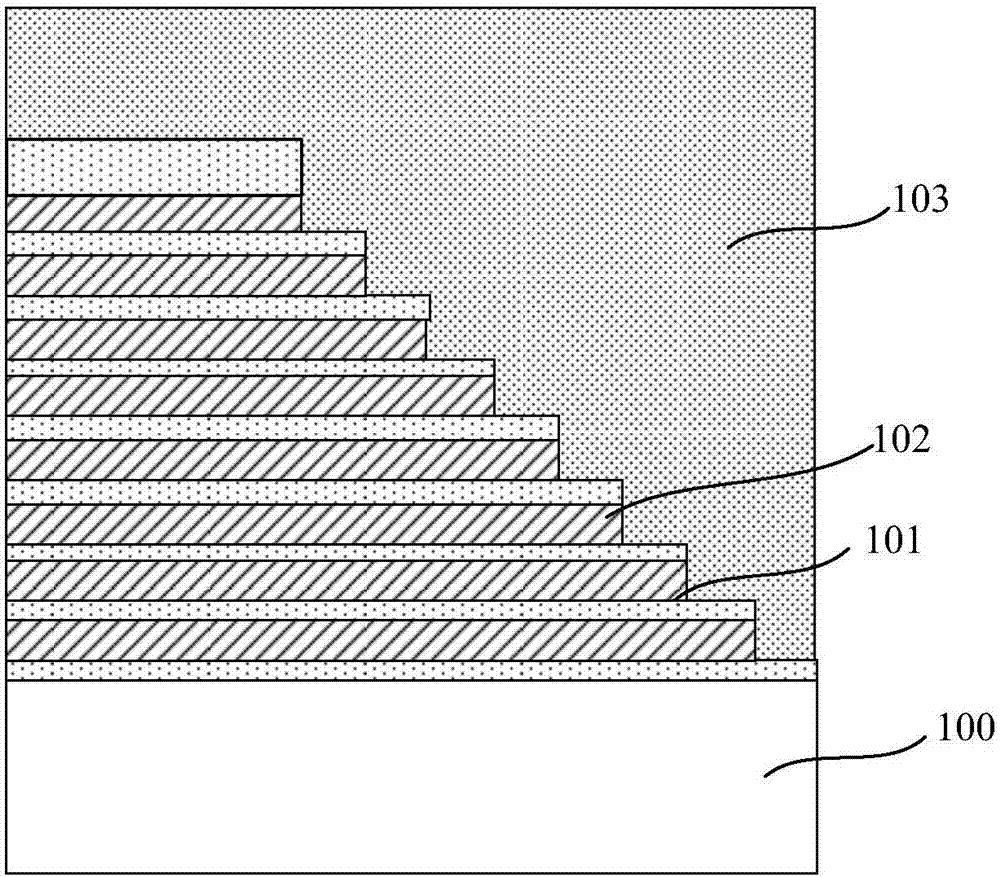

3D NAND memory and manufacturing method thereof

ActiveCN111403397AReduce the risk of electric leakageImprove yieldSolid-state devicesSemiconductor devicesEngineeringElectrode Contact

The invention provides a 3D NAND memory and a manufacturing method thereof. Before a grid line gap is formed, a first part selection grid tangent line is formed at a position where a common source electrode contact part is to be formed; the width of the first top selection grid tangent line is greater than that of the grid line gap, so the formed common source contacts the periphery; the stacked layer is replaced by the insulating material for forming the top selection gate tangent, so that a forming window for forming the contact part of the common source electrode is enlarged, even if the contact part is slightly deviated from the common source electrode, the contact part cannot be in contact with the gate layers on the two sides of the bridging common source electrode, the electric leakage risk of the device is reduced, and the yield of the device is improved. Meanwhile, the forming window of the contact part is enlarged, so that the manufacturing difficulty of the contact part is reduced to a certain extent. In addition, the first top selection gate tangent line and the second top selection gate tangent line can be formed by using the same mask, so that the preparation of the mask and the etching step are saved, and the manufacturing cost of the memory is reduced.

Owner:YANGTZE MEMORY TECH CO LTD

Manufacture process of copper interconnection line

InactiveCN102938392AFewer etch stepsReduce manufacturing costSemiconductor/solid-state device manufacturingPolyamine CompoundEtching

The invention relates to the semiconductor manufacture field and particularly relates to a manufacture process of a copper interconnection line. According to the manufacture process of the copper interconnection line, an isolating membrane is formed between two layers of light resistance in a double exposure technology by using polyamine compound materials in a copper interconnection process with grooves preferred, and through holes and metal groove structures in the light resistance are transferred to a media layer successively, so that the prior art that metal groove etching and through hole etching are divided into two independent steps is replaced, etching steps in a dual damascene metal interconnection line process are effectively reduced, the productivity is improved, and the manufacture cost is decreased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Manufacturing method for stepped silicon germanium source/drain structures

ActiveCN102403227BDepth is easy to controlShape is easy to controlSemiconductor/solid-state device manufacturingIon implantationSilicon-germanium

The invention provides a manufacturing method for stepped silicon germanium source / drain structures, which includes firstly, providing a silicon substrate, wherein a grid structure, first gap walls on two sides of the grid structure and second gap walls on two sides of each first gap wall are formed on the silicon substrate, secondly, performing multiple times of ion implantation technology by different directions and depths to form a first amorphous state region in the silicon substrate on two sides of each second gap wall and form at least one second amorphous state region in the silicon substrate below the second gap walls, thirdly, removing the second gap walls, fourthly, removing the first amorphous state regions and the second amorphous state regions to form a stepped recess, and fifthly, forming a doped stepped silicon germanium source / drain structure in the stepped recess. Compared with the prior art, the manufacturing method for stepped silicon germanium source / drain structures can reduce etching procedures and lower control difficulty of the etching process.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Method for manufacturing phase shift photomask

InactiveCN102879996AFewer etch stepsReduce manufacturing costPhotomechanical exposure apparatusMicrolithography exposure apparatusPhase shiftedOptoelectronics

The invention provides a method for manufacturing a phase shift photomask. The method comprises the following steps of: forming a first layout graphics structure in a first photoresist in a first photoetching way on a phase shift photomask substrate comprising the first photoresist capable of forming a hard film; coating a micro auxiliary film on the first photoresist to cure the first layout graphics structure in the first photoresist, performing heating to react the micro auxiliary film and the surface of the first photoresist to form a separation film insoluble in a second photoresist, and removing a redundant micro auxiliary film by using de-ionized water or the de-ionized water solution of a surfactant; coating the second photoresist on the cured first photoresist; performing second photoetching, thereby forming a second layout graphics structure in a second photoresist film; and performing etching to transfer the first and second layout graphics structures in the photoresists into a partially transparent molybdenum silicide thin film and a non-transparent chromium thin film respectively to finish manufacturing the phase shift photomask. According to the method, the etching step of a phase shift photomask manufacturing process is eliminated, so that yield can be effectively improved, and manufacture cost can be reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Semiconductor device, manufacture method for the same and electronic device

ActiveCN107546228AReduce photolithography processFewer etch stepsSolid-state devicesSemiconductor devicesDielectric layerElectron

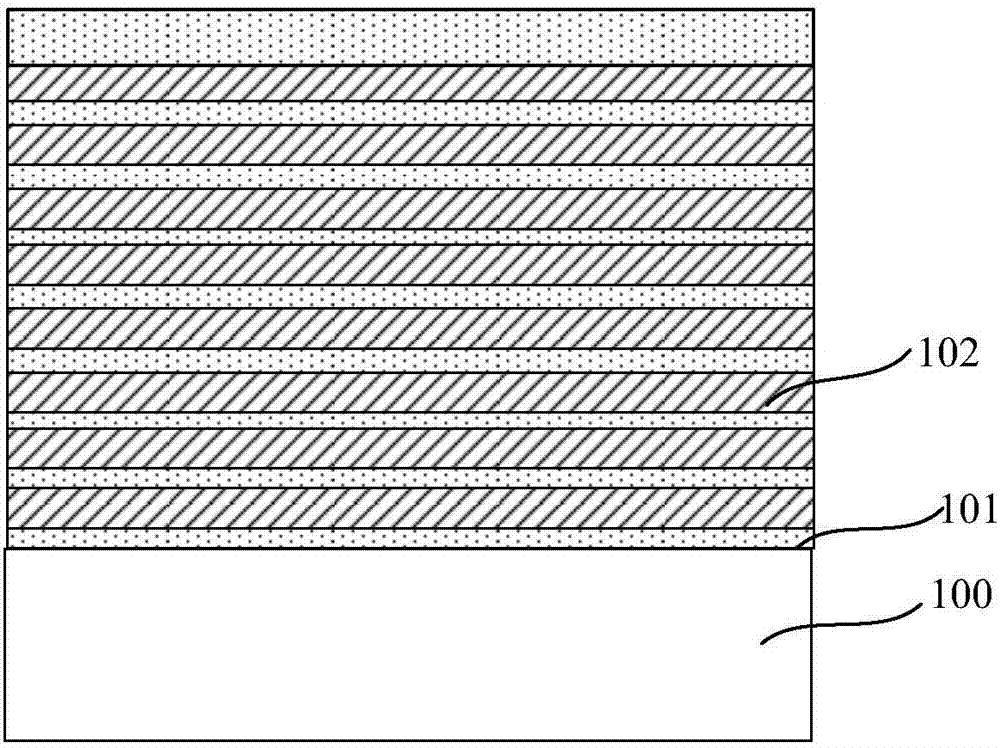

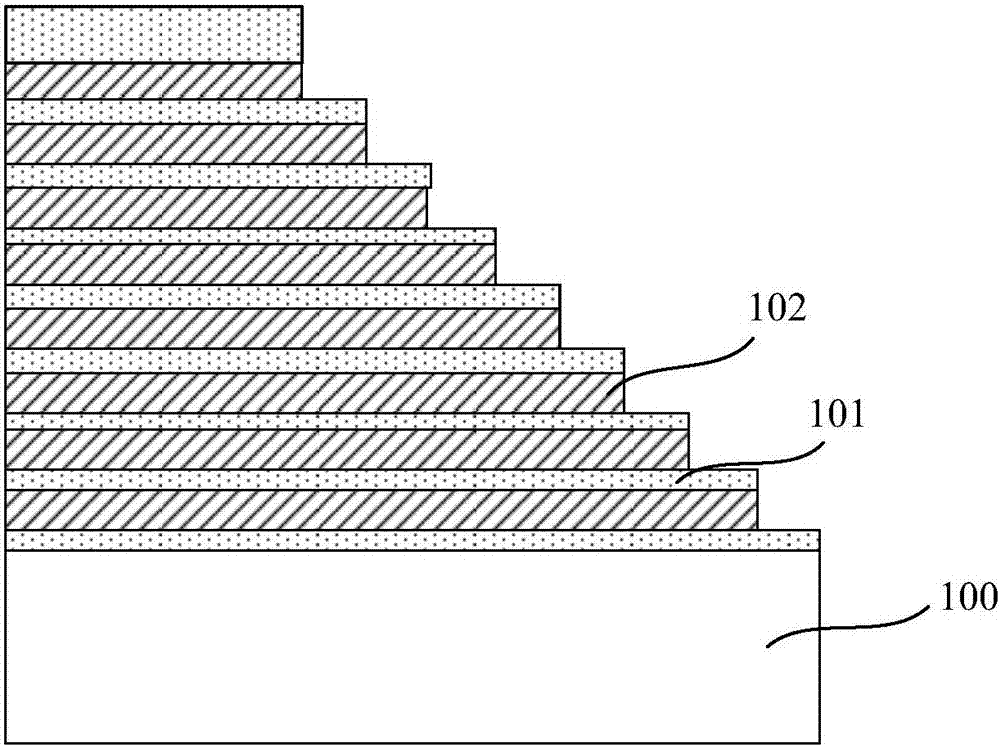

The invention provides a semiconductor device, a manufacture method for the same and an electronic device. The manufacture method for the semiconductor device comprises steps of providing a semiconductor substrate, wherein the semiconductor substrate at least comprises a storage area and a contact plugging area, forming multiple layers of laminating structures on the semiconductor substrate in thestorage area and each laminating layer structure comprises a dielectric layer and a control gate layer arranged over the dielectric layer, forming a first dielectric layer covering the multiple layers of laminating layer structures and the contact plugging area, forming multiple first contact plugs which correspond to the control gate layer in the multiple layers of laminating layers in the firstdielectric layer in the contact plugging area, forming a second dielectric layer on the first dielectric layer and forming multiple second contact plugs which are in corresponding connection with multiple first contact plugs in the second dielectric layer. The manufacture method can reduce technology difficulty and cost and the semiconductor device and the electronic device are simple in structure and low in cost.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Manufacturing process for copper interconnection line

ActiveCN102832107AFewer etch stepsReduce manufacturing costSemiconductor/solid-state device manufacturingEtchingMetallurgy

The invention relates to the manufacturing field of semiconductors, in particular to a manufacturing process for a copper interconnection line. According to the manufacturing process for the copper interconnection line disclosed by the invention, silanization materials are adopted in a trench-preference copper interconnection process to form an isolating film between two layers of photoresists in a dual-exposure technology, and through holes and metal trench structures in the photoresists are transferred to dielectric layers in sequence, so that the existing process, in which the etching of the metal trench and the etching of the through hole are carried out in two independent steps, can be replaced, the etching steps in dual-Damascus metal interconnection line process are effectively reduced, the production capacity is increased and the manufacturing cost is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

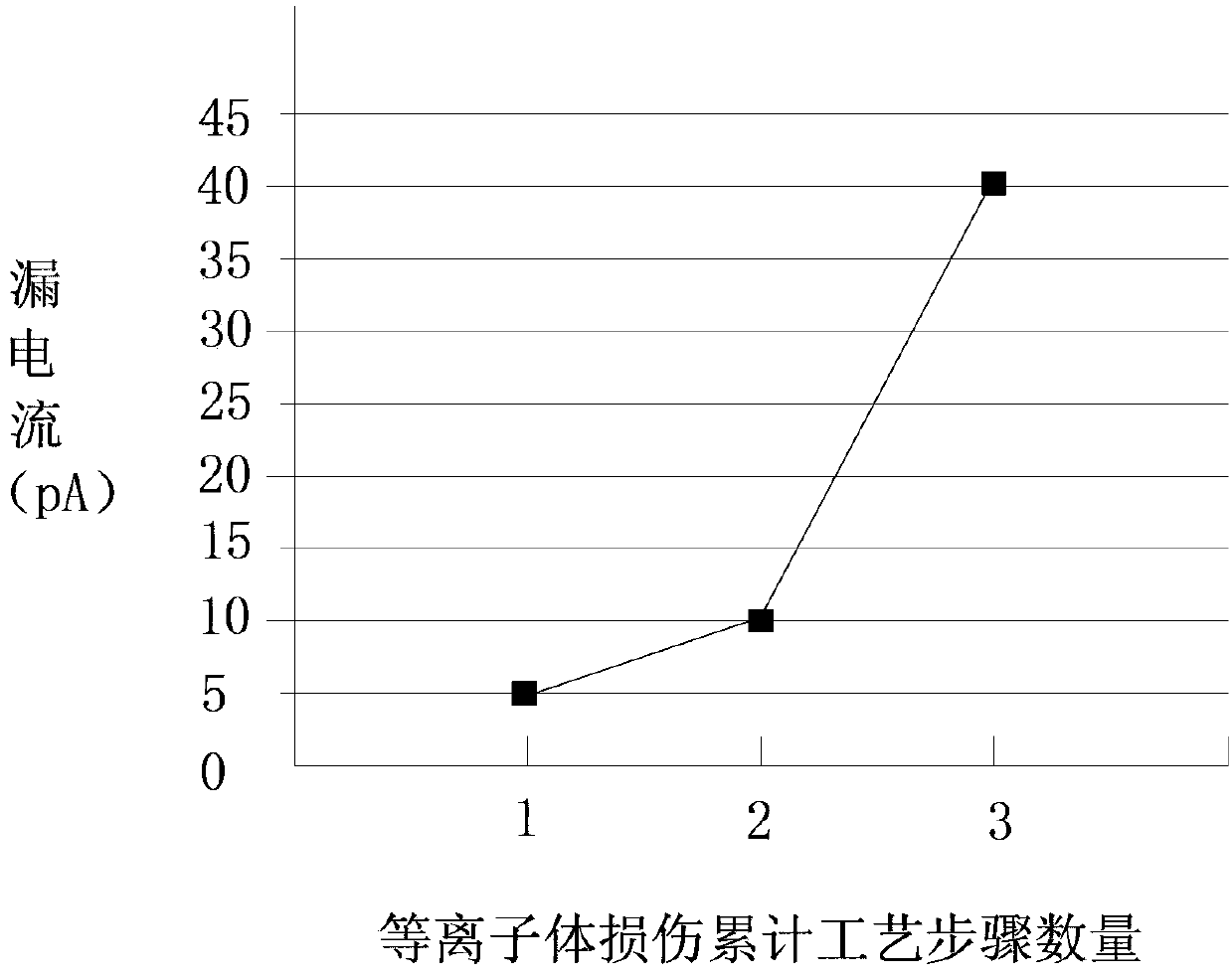

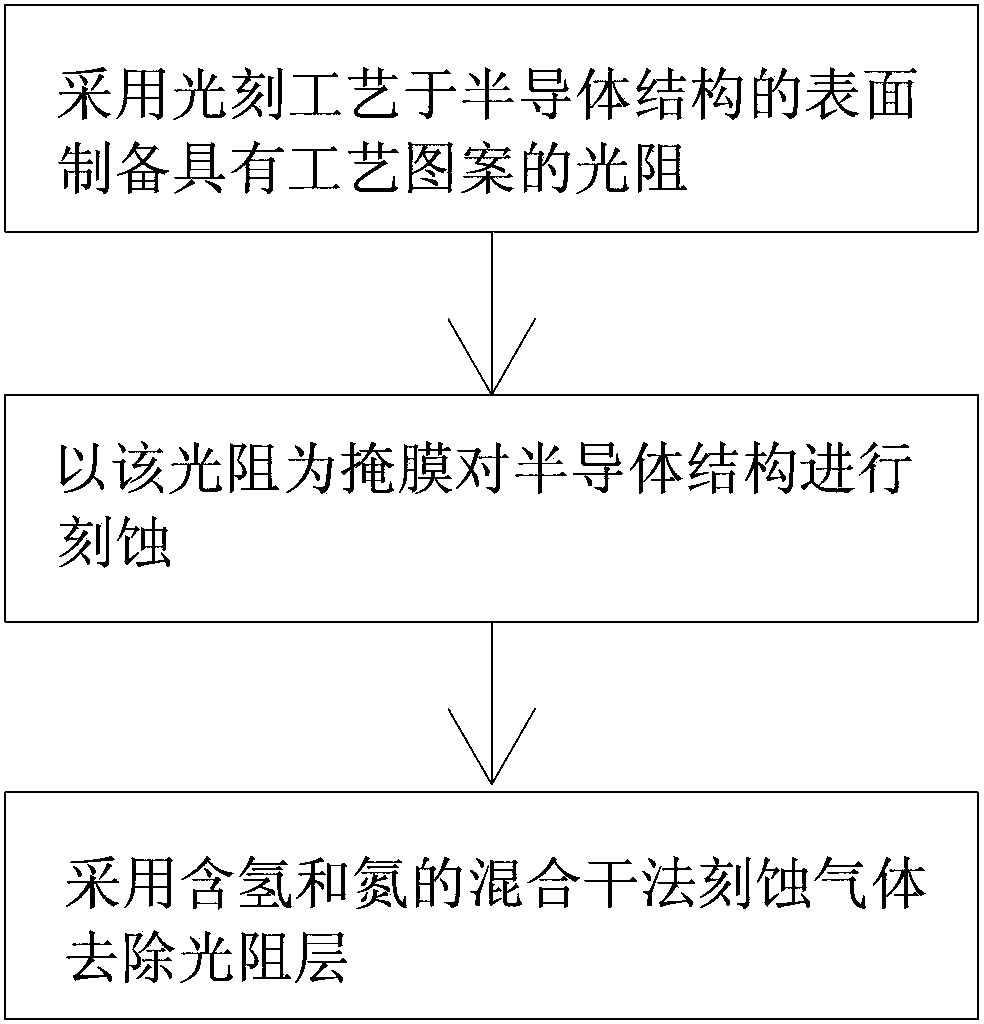

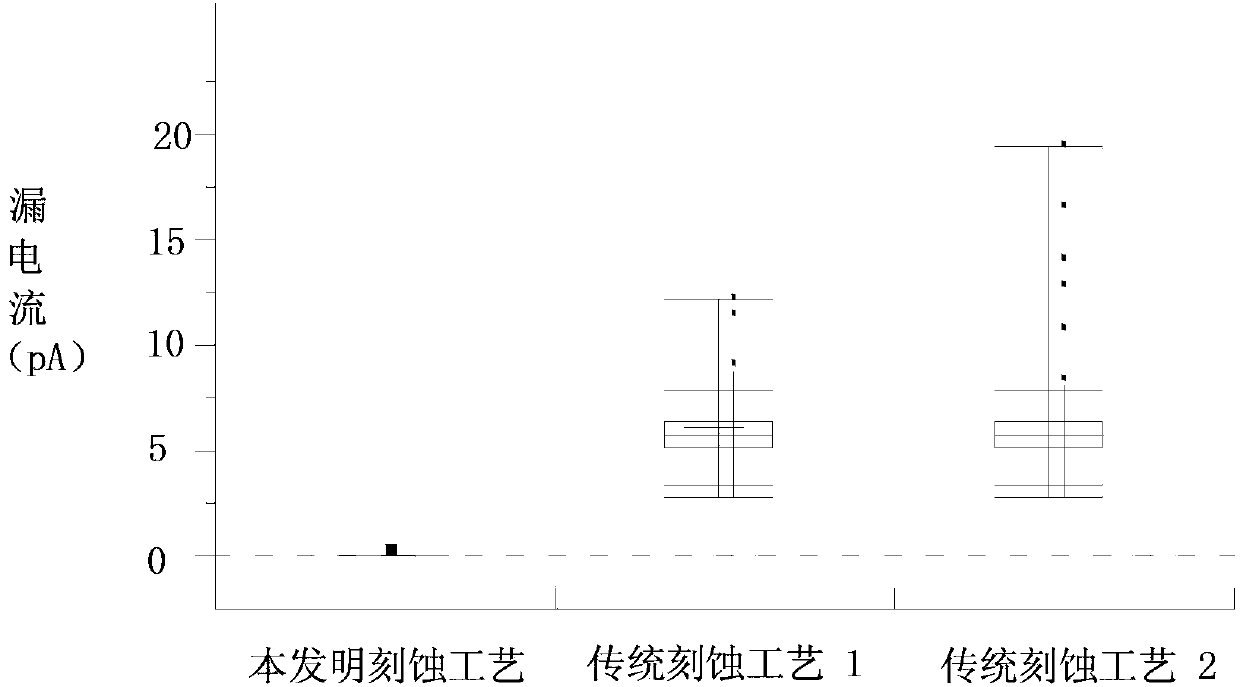

Method for repairing plasma damage in metal interconnection layer process

InactiveCN103426818ARepair damageFewer etch stepsSemiconductor/solid-state device manufacturingResistMetal interconnect

The invention relates to a method for repairing plasma damage in a metal interconnection layer process. The method is applied to a semiconductor structure formed after a top passivating film deposition process in a preparation process of a rear metal interconnection layer. The method includes the steps: preparing a photo-resist layer with process patterns on the surface of the semiconductor structure by a photolithographic process; removing the photo-resist layer by mixed dry etching gas containing hydrogen and nitrogen after continuously etching the semiconductor structure by taking the photo-resist layer as a mask to repair the plasma damage in the semiconductor structure. The process effects of dry photo-resist removal and plasma damage repair can be simultaneously achieved only by one etching step. Compared with a traditional process, the method saves process steps.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

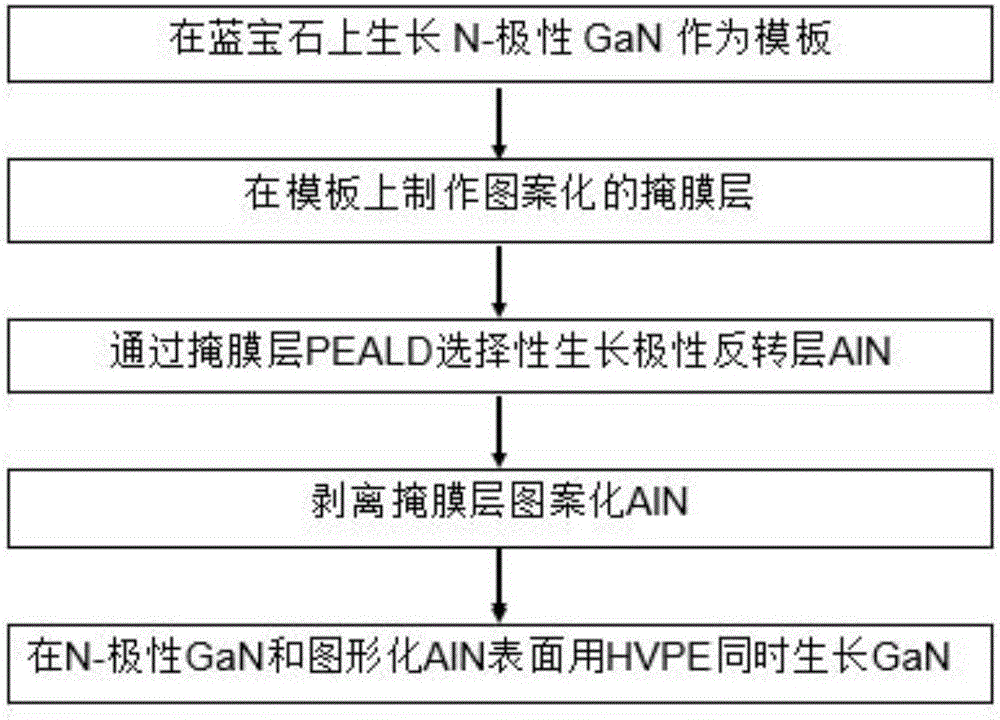

Method for growing polarity alternate GaN structure on N-polar GaN template

InactiveCN106783551AAvoid damageAvoid mismatchSemiconductor/solid-state device manufacturingPhysicsPhotoresist

The invention discloses a method for growing polarity alternate GaN structure on N-polar GaN template, belong to the field of semiconductor process and devices. The N-polar GaN grown by MOCVD on sapphire substrate serves as a template, and a patterned photoresist is fabricated on the template as a mask layer by photolithographic process. An AlN selectively grows for polarity inversion on the mask layer with T-ALD method, wherein the T-ALD method can make the process temperature lower than the melting point of the mask layer to ensure that the mask layer is not deformed, and an AlN thin-film with good uniformity and precisely controllable thickness can be prepared. The stripping patterned AlN on the mask layer eliminates the etching step of the traditional patterning process and avoids the damage of the etching to the device structure. Finally, a GaN thick-film grows on the bare N-polar GaN template and the patterned AlN by HVPE method, and a polarity alternate GaN structure with a thickness of 1mm is expected to be obtained to meet the requirements of high-power component for the thick-film polarity alternate GaN.

Owner:UNIV OF SCI & TECH BEIJING

Through-hole-priority dual damascene copper interconnection method for reducing coupling capacitance of redundant metal

ActiveCN103268866AImprove performanceCoupling capacitance is reduced or eliminatedSemiconductor/solid-state device manufacturingPhotosensitive material processingCapacitanceInterconnection

The invention discloses a through-hole-priority dual damascene copper interconnection method for reducing coupling capacitance of redundant metal. According to the through-hole-priority dual damascene copper interconnection method for reducing the coupling capacitance of the redundant metal, a dielectric layer is firstly deposited on a substrate silicon wafer and then the dielectric layer is coated with first photoresist; a through hole structure and a redundant metallic groove structure are formed in a first photoresist film through exposure and development, and the metallic groove structure formed in the first photoresist penetrates through the first photoresist; in the same developing machine, the first photoresist is coated with chemical shrink material RELACS to solidify the through hole structure and the redundant metallic groove structure which are formed in the first photoresist, the RELACS can react with the surface of the first photoresist to form an isolating film which can not dissolve in second photoresist under the heating condition, and then the remaining RELACS which does not react with the surface of the first photoresist is removed; the first photoresist on which the isolating film is formed is coated with the second photoresist, and the anti-etching capacity of the first photoresist is stronger than that of the second photoresist; a metallic groove structure located in the through hole structure is formed in a second photoresist film through exposure and development.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

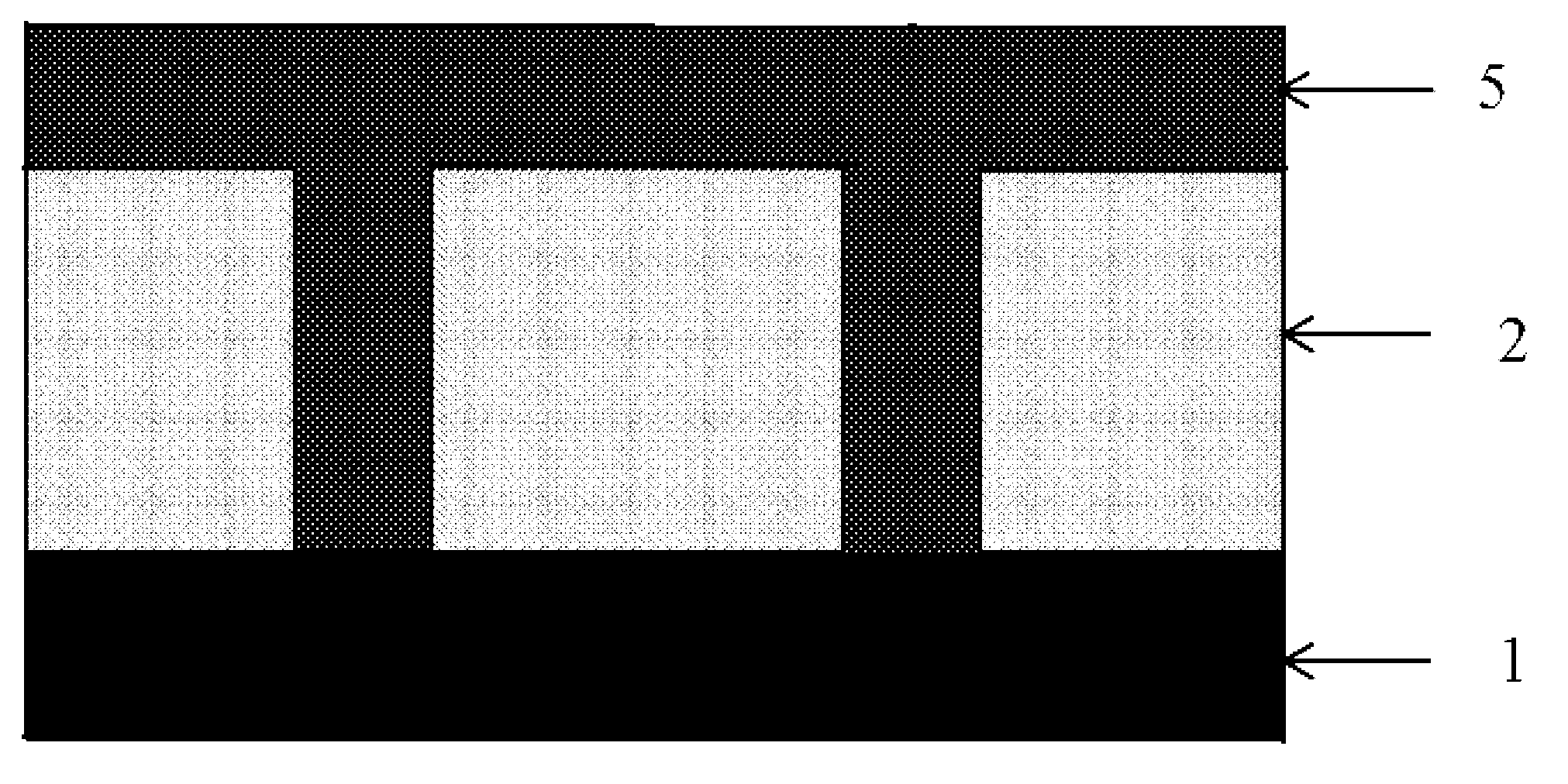

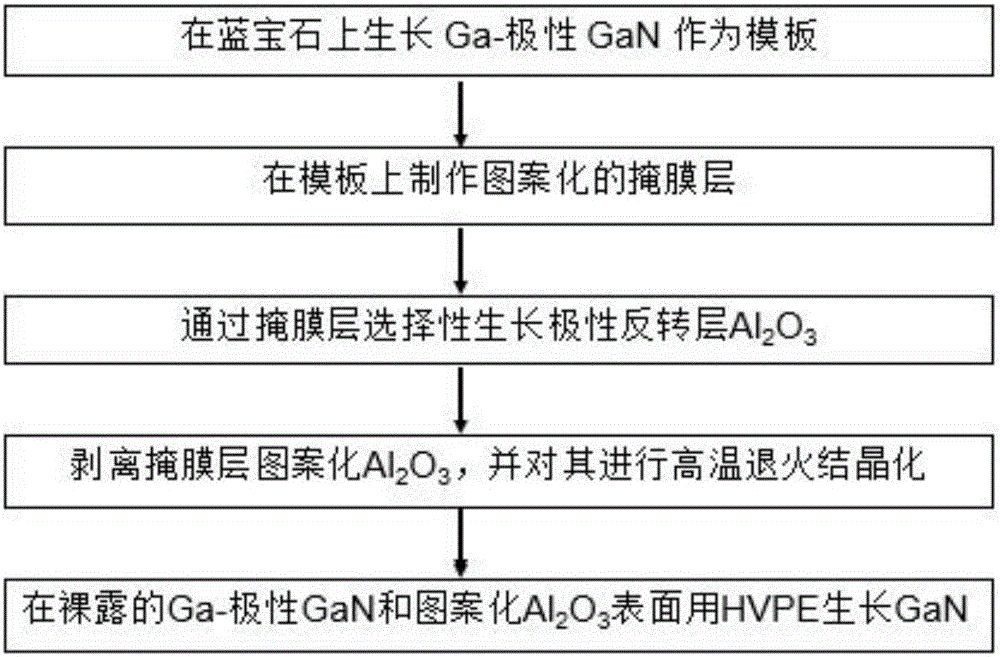

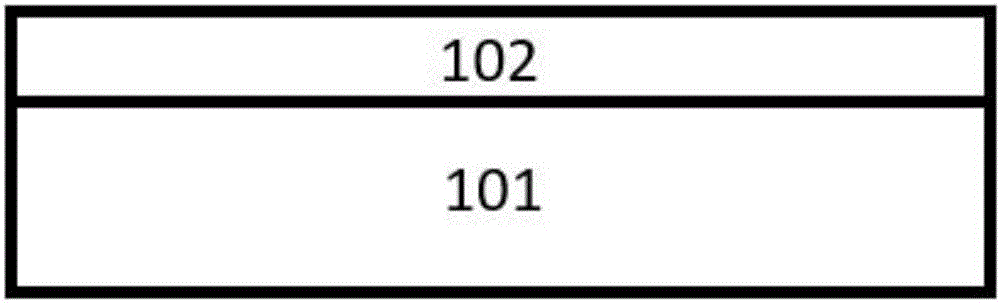

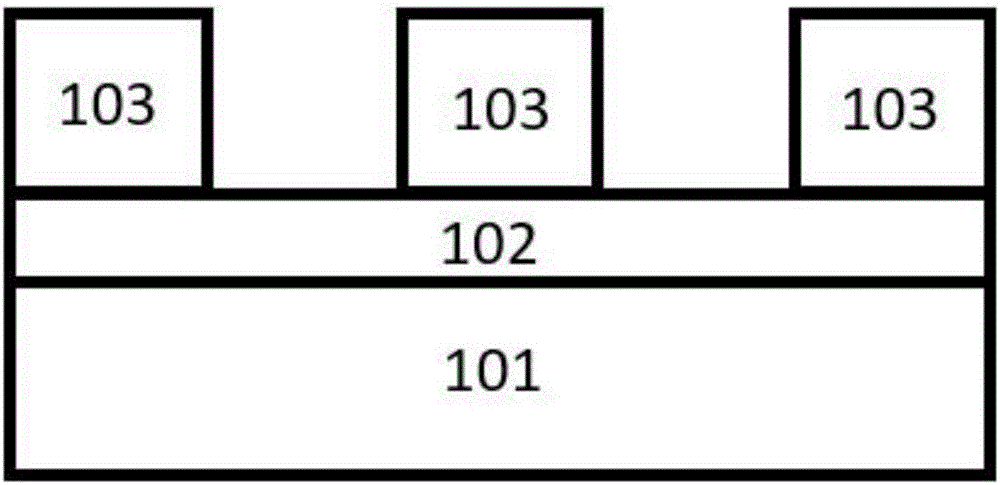

Method for growing alternating polarity GaN structure on Ga-polar GaN template

InactiveCN106847668AImprove crystal qualityGuaranteed to be intactSemiconductor/solid-state device manufacturingVapor phaseSemiconductor

The invention provides a method for growing alternating polarity GaN structure on a Ga-polar GaN template and belongs to the field of semiconductor technologies and devices. Ga-polar GaN growing on a sapphire substrate through MOCVD serves as the template, a patterned polyvinylpyrrolidone film is manufactured on the template through the photoetching technology to serve as a mask layer, Al2O3 used for polarity inversion selectively grows on the mask layer by means of the PE-ALD method, the PE-ALD method can make the process temperature lower than the melting point of the mask layer, a Al2O3 thin film which is good in uniformity and whose thickness can be precisely controlled can be prepared while it is guaranteed that the mask layer does not deform, the patterned Al2O3 of the mask layer is stripped and subjected to crystallization through high-temperature annealing, finally, thick film GaN growth is conducted on the exposed Ga-polar GaN template and the patterned Al2O3 through the hydride vapor phase epitaxy method, and the alternating polarity GaN requirement that the thickness of a high-power device needs to reach 1 mm is hopeful to be met.

Owner:UNIV OF SCI & TECH BEIJING

Groove-preferential dual-damascene copper-connection method reducing redundant metal coupling capacitance

InactiveCN103258792AImprove performanceCoupling capacitance is reduced or eliminatedSemiconductor/solid-state device manufacturingCapacitanceCoupling

The invention provides a groove-preferential dual-damascene copper-connection method reducing redundant metal coupling capacitance. A medium layer is firstly deposited on a substrate silicon wafer, and then first photoresist is coated on the medium layer. A metal groove structure is formed in a first photoresist film through exposure and development, and the metal groove structure formed in the first photoresist penetrates through the first photoresist. In an identical development machine stand, a miniature auxiliary film is coated on the first photoresist to solidify the figure of the metal groove structure in the first photoresist, the miniature auxiliary film and the surface of the first photoresist is made to react through heating to form an isolating film not soluble in second photoresist, and then the miniature auxiliary film which does not react with the surface of the first photoresist and is left is removed. The second photoresist is coated on the first photoresist with the isolating film. A through hole structure arranged in the metal groove structure and a redundant metal groove structure arranged on the first photoresist are formed in the second photoresist through the exposure and the development.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

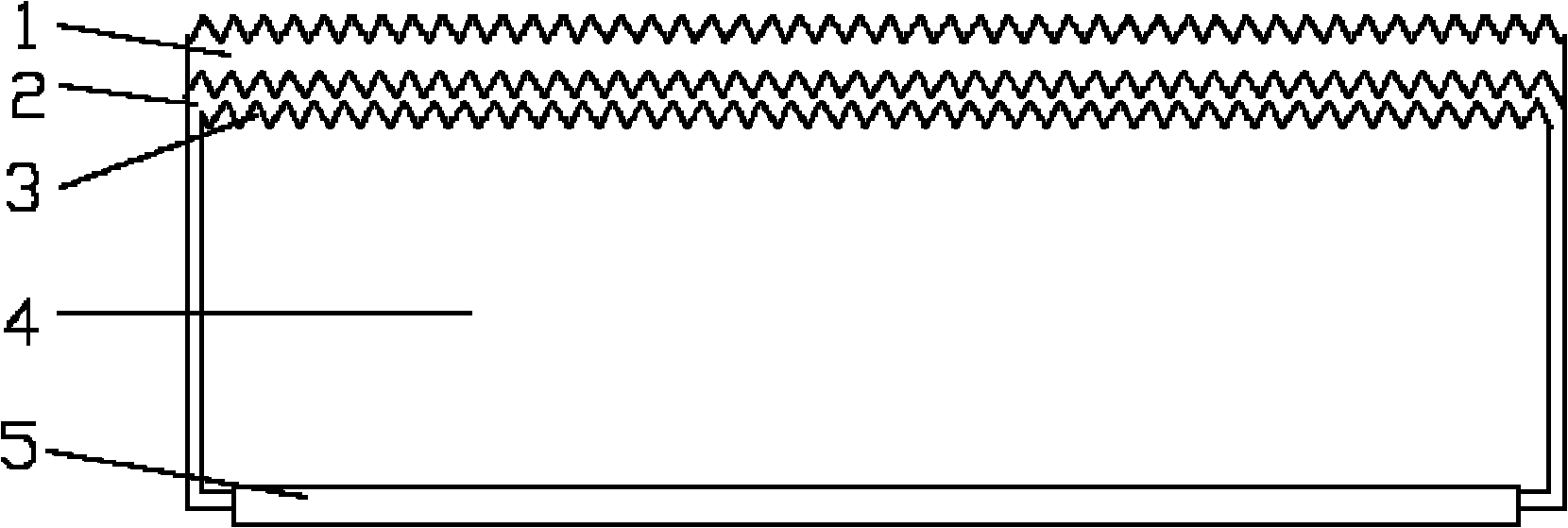

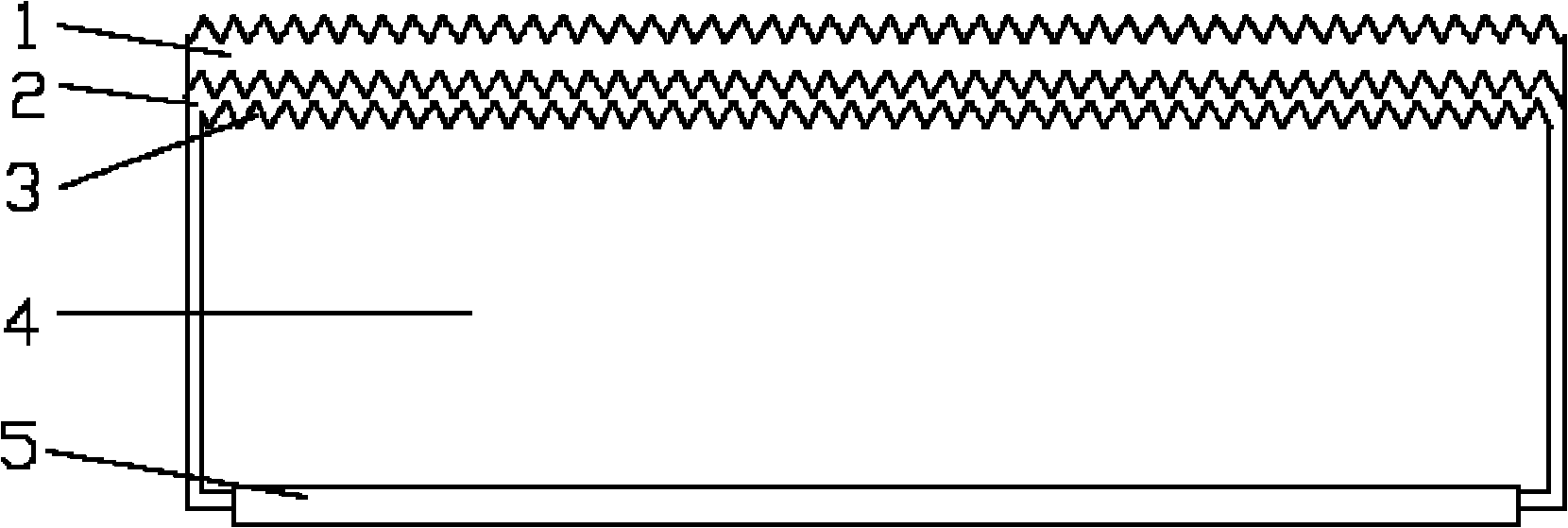

Production process of N-type back contact solar cell

InactiveCN102569518ARealize thermal diffusionReduce etchingFinal product manufactureSemiconductor devicesScreen printingSolar cell

The invention relates to a production process of an N-type back contact solar cell. The production process comprises the following steps of: flocking a silicon substrate so that a light reflective surface has a flock surface; oxidizing the silicon substrate; manufacturing a diffusion window on a back side of the silicon substrate; carrying out selective boron source thermal diffusion to enable the exposed silicon to be doped by boron to form a PN junction; removing an oxide layer and impurities; oxidizing the silicon substrate again; plating an anti-reflecting film on the light reflective surface of the silicon substrate; carrying out screen printing by using metal electrode paste; and sintering to obtain a metal electrode to finish the manufacturing of the cell. The production process disclosed by the invention is artful in concept, compatible with conventional industrial cell production and easy to realize industrial manufacturing; meanwhile, relative to the conventional solar cell, the N-type back contact solar cell manufactured by the production process disclosed by the invention has the advantages that: an etching step with higher cost is saved, and metal electrode screen printing is changed into a one-step screen printing from three-step metal electrode screen printing of the conventional solar cell. The production process disclosed by the invention is widely applied in the photovoltaic field and has favorable market prospect.

Owner:杨正刚

Manufacturing method for copper interconnection lines

InactiveCN102810511AFewer etch stepsReduce manufacturing costSemiconductor/solid-state device manufacturingEtchingSemiconductor

The invention relates to the field of semiconductor manufacturing, in particular to a manufacturing method for copper interconnection lines. According to the manufacturing method for copper interconnection lines, provided by the invention, miniature solidified materials are adopted in a slot-prior copper interconnection process to form an isolating film between two layers of light resistors in a double-exposure technology, and through holes and metal slot structures in the light resistors are shifted to media layers sequentially, so that the existing process in which metal slot etching and through hole etching are traditionally regarded as two independent steps is replaced, and further the etching steps in a double Damascus metal interconnection line process are reduced effectively. Therefore, the productivity is improved and the manufacturing cost is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for fabricating phase shift photomask

InactiveCN102902153AFewer etch stepsReduce manufacturing costOriginals for photomechanical treatmentPolyamine CompoundPhase shifted

The invention provides a method for fabricating a phase shift photomask, comprising the following steps of: on a phase shift photomask substrate containing a first photoresist capable of forming a hard film, forming a first layout pattern structure in the first photoresist through first photoetching; applying a polyamine compound on the first photoresist so as to solidify the first layout pattern structure in the first photoresist, heating to react the polyamine compound with the surface of the first photoresist so as to form an isolation film insoluble in a second photoresist, and removing the redundant polyamine compound; applying the second photoresist to the solidified first photoresist; performing second photoetching so as to form a second layout pattern structure in the second photoresist film; and transferring the first layout pattern and the second layout pattern in the photoresists to a partially light-pervious molybdenum silicide thin film and a light-tight chromium thin film through etching, respectively, thereby completing the fabrication of the phase shift photomask. The process is omitted from the etching step in the phase shift photomask fabrication process and is capable of effectively improving the productivity and reducing the fabrication cost.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Groove-priority dual damascene copper interconnection method for reducing coupling capacitance of redundant metal

InactiveCN103268865AImprove performanceCoupling capacitance is reduced or eliminatedSemiconductor/solid-state device manufacturingPhotosensitive material processingCapacitanceInterconnection

The invention provides a groove-priority dual damascene copper interconnection method for reducing coupling capacitance of redundant metal. According to the groove-priority dual damascene copper interconnection method for reducing the coupling capacitance of the redundant metal, a dielectric layer is firstly deposited on a substrate silicon wafer and then the dielectric layer is coated with first photoresist; metallic grooves are formed in a first photoresist film through exposure and development, and the metallic grooves formed in the first photoresist penetrate through the first photoresist; in the same developing machine, the first photoresist is coated with RELACS to solidify the metallic grooves in the first photoresist, the RELACS can react with the surface of the first photoresist to form an isolating film which can not dissolve in second photoresist under the heating condition, and then the remaining RELACS which does not react with the surface of the first photoresist is removed; the first photoresist on which the isolating film is formed is coated with the second photoresist; a through hole in each metallic groove and a redundant metallic groove located in the first photoresist are formed in a second photoresist film through exposure and development.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Forming method for embedded flash memory structure

ActiveCN109768046AFewer etch stepsReduce processing costsSolid-state devicesSemiconductor devicesEngineeringElectrical and Electronics engineering

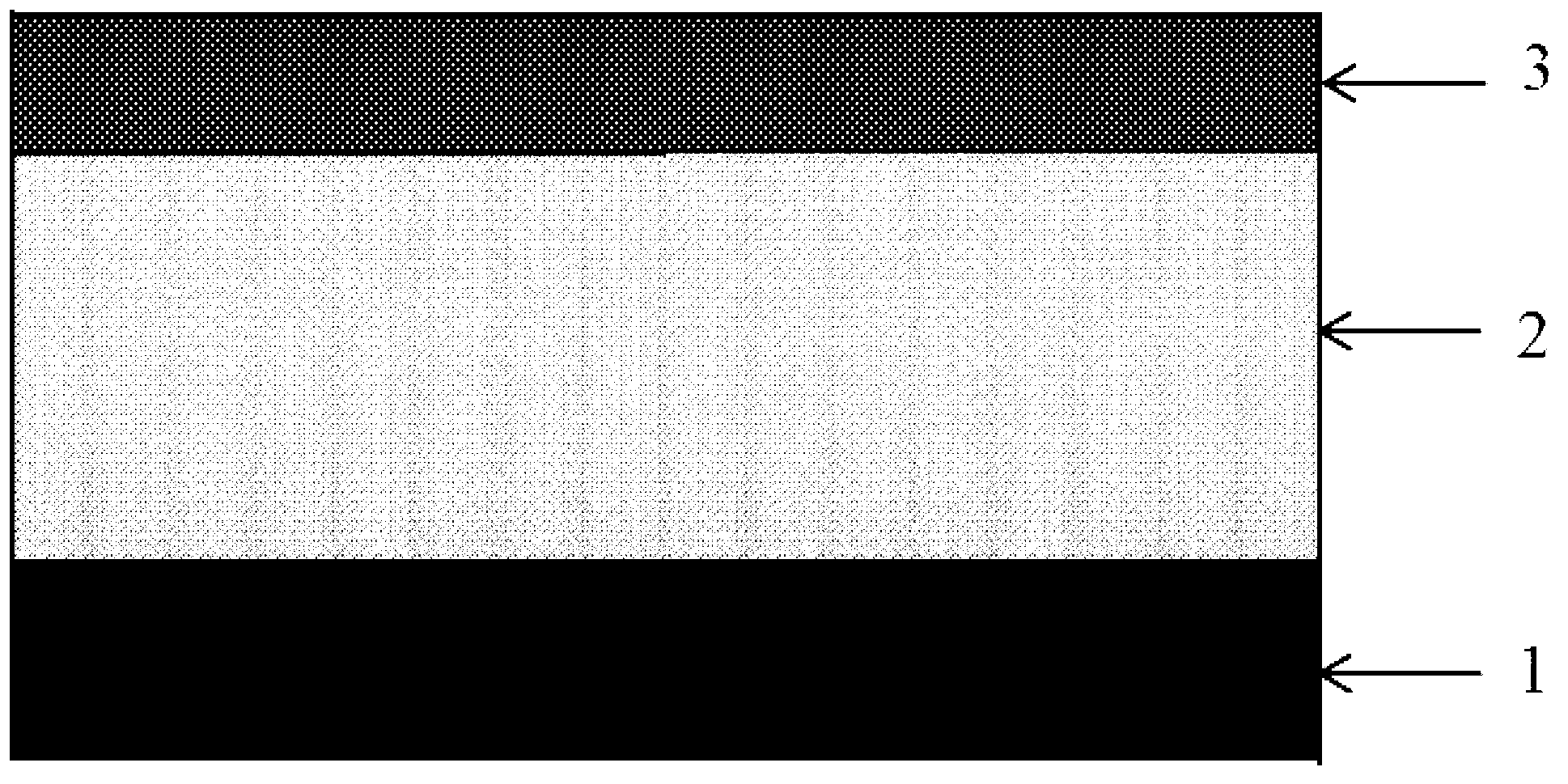

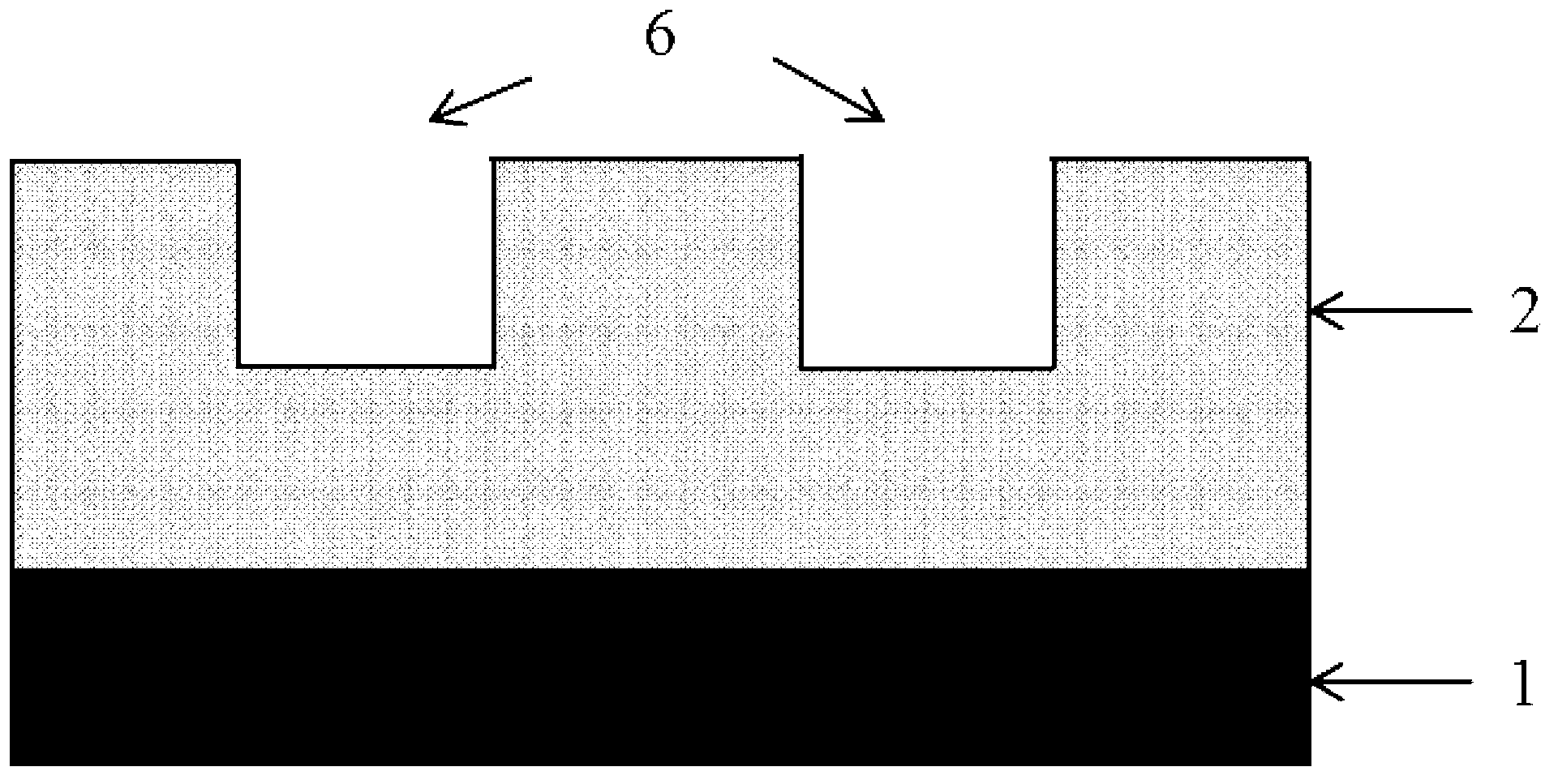

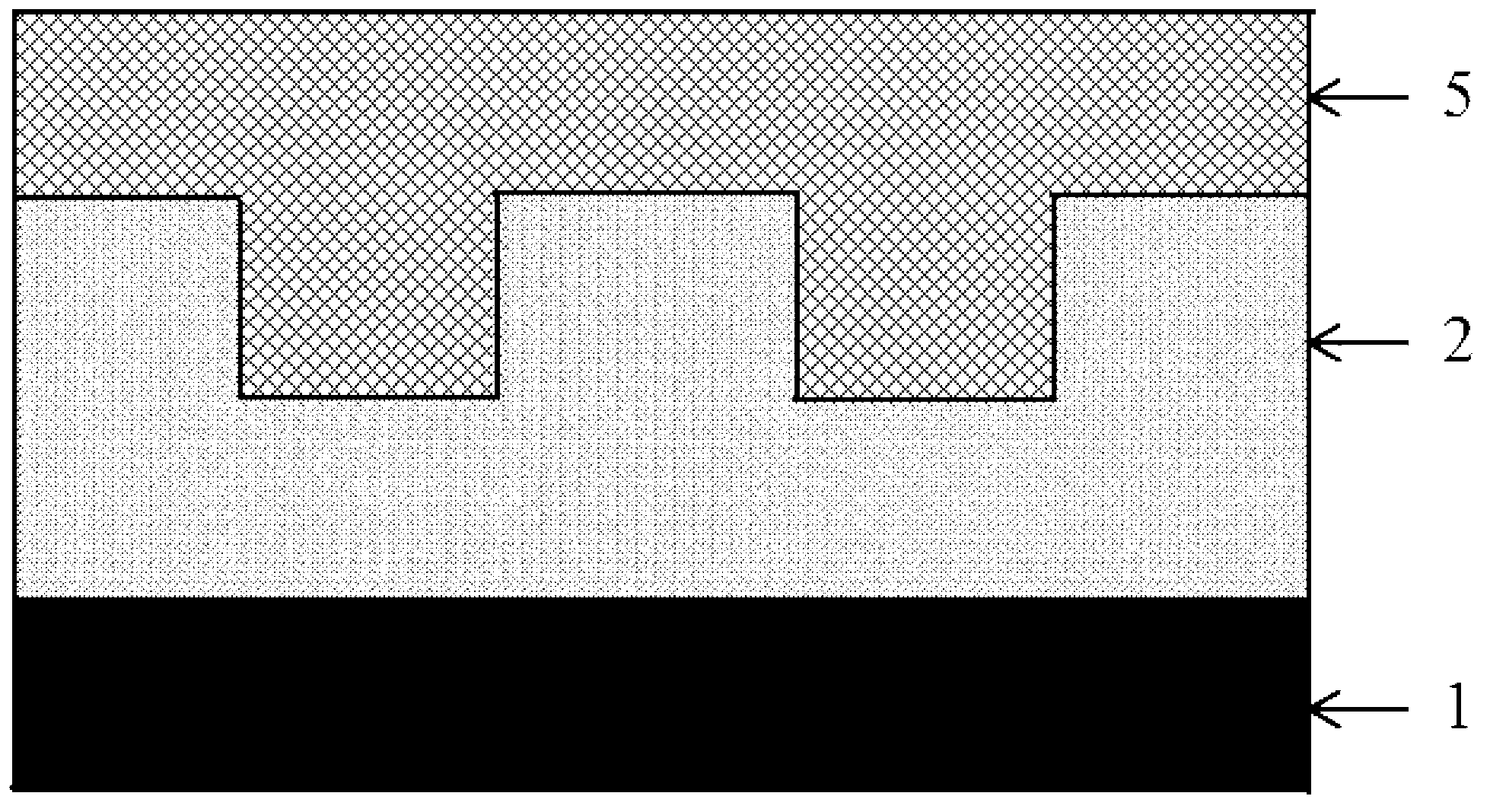

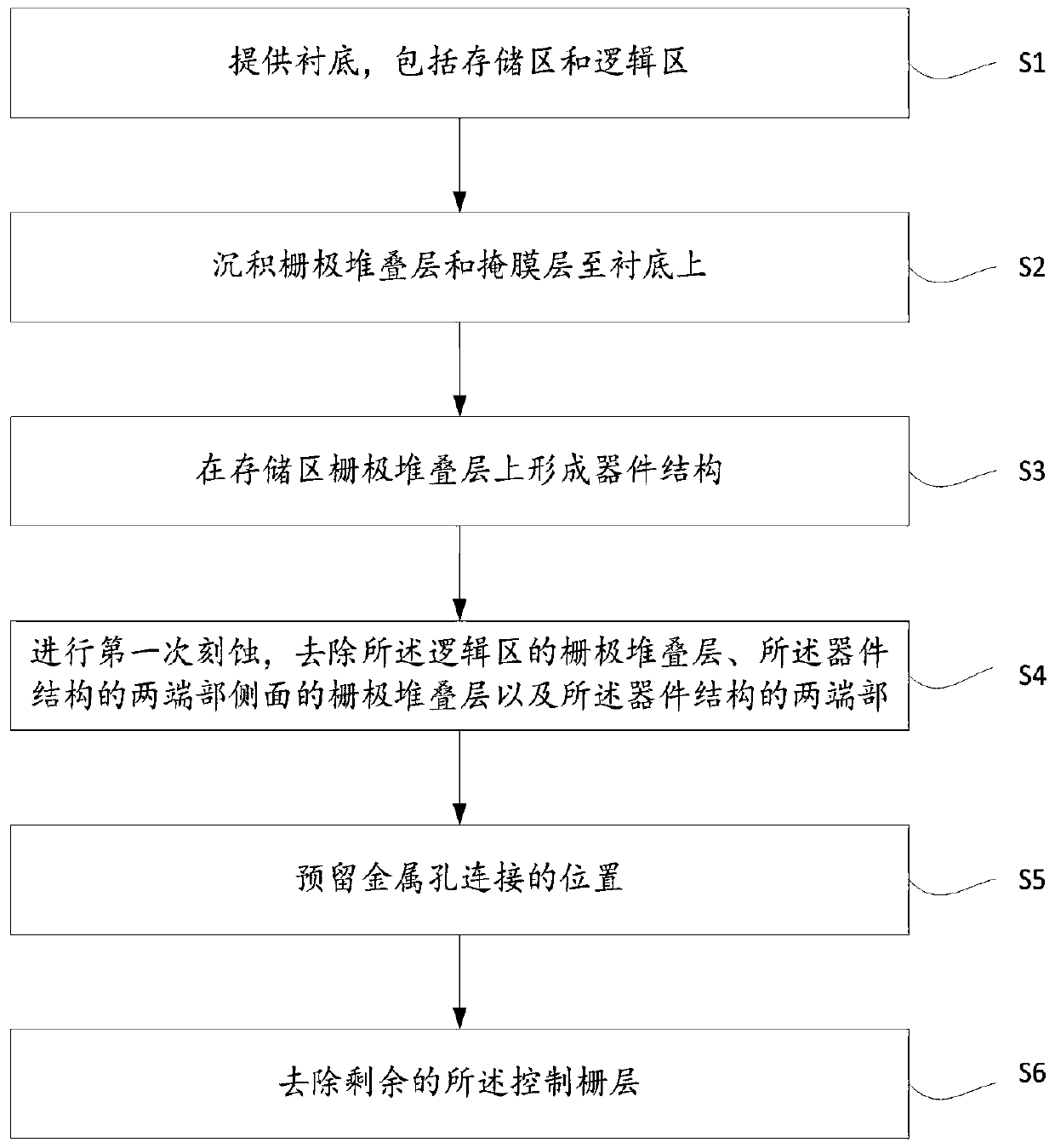

The invention relates to a forming method for an embedded flash memory structure. The method comprises the steps that a substrate is provided, wherein the substrate comprises a storage region and a logic region; grid stacking layers are deposited on the substrate; a device structure is formed on the grid stacking layer of the storage region; first etching is performed, and the grid stacking layeron the logic region, the grid stacking layers on the side faces of the two ends of the device structure and the grid stacking layers at the two ends of the device structure are removed; and second etching is performed, wherein metal hole connection positions are reserved first, and then remaining control grid layers are removed. According to the method, the grid stacking layers are deposited on the storage region and the logic region at the same time; and by simultaneously removing the grid stacking layer on the logic region, the grid stacking layers at the ends of the device structure on thestorage region and the grid stacking layers around the ends of the device structure, the control grid layers connected to the ends of the device structure are cut off and redundant grid stacking layers are removed in the same process, therefore, etching steps are reduced, and process cost is saved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A manufacturing process of copper interconnection wire

ActiveCN102832107BFewer etch stepsReduce manufacturing costSemiconductor/solid-state device manufacturingEtchingCopper interconnect

The invention relates to the manufacturing field of semiconductors, in particular to a manufacturing process for a copper interconnection line. According to the manufacturing process for the copper interconnection line disclosed by the invention, silanization materials are adopted in a trench-preference copper interconnection process to form an isolating film between two layers of photoresists in a dual-exposure technology, and through holes and metal trench structures in the photoresists are transferred to dielectric layers in sequence, so that the existing process, in which the etching of the metal trench and the etching of the through hole are carried out in two independent steps, can be replaced, the etching steps in dual-Damascus metal interconnection line process are effectively reduced, the production capacity is increased and the manufacturing cost is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

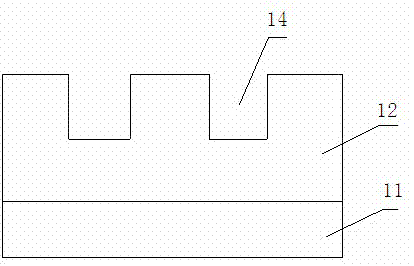

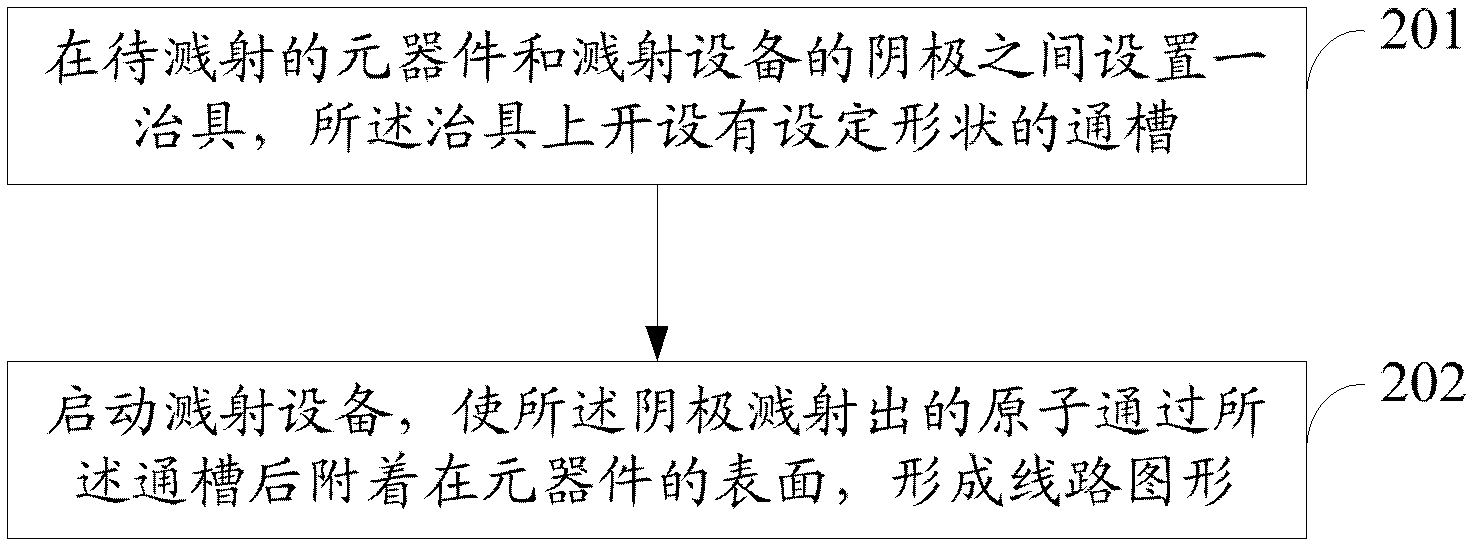

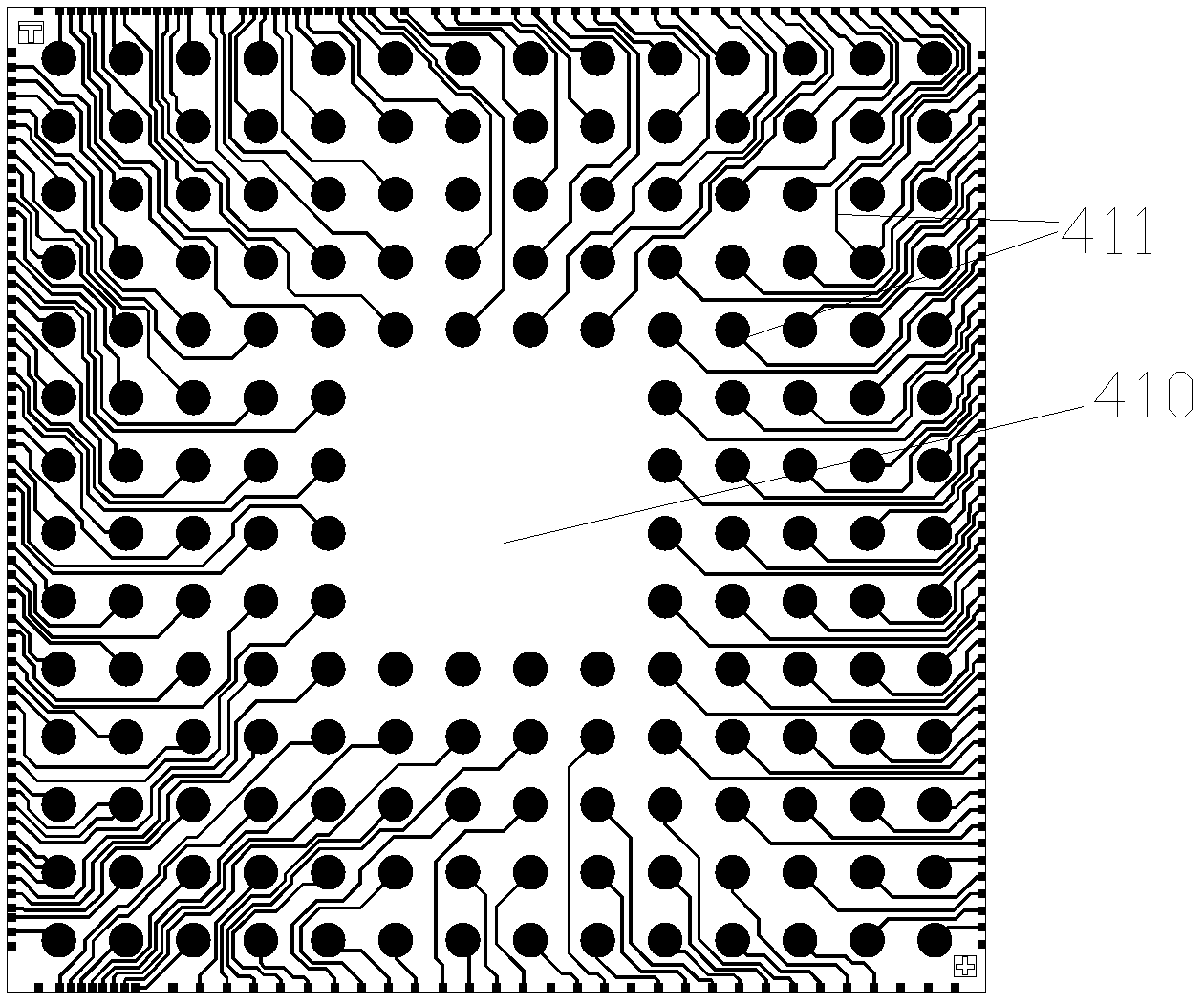

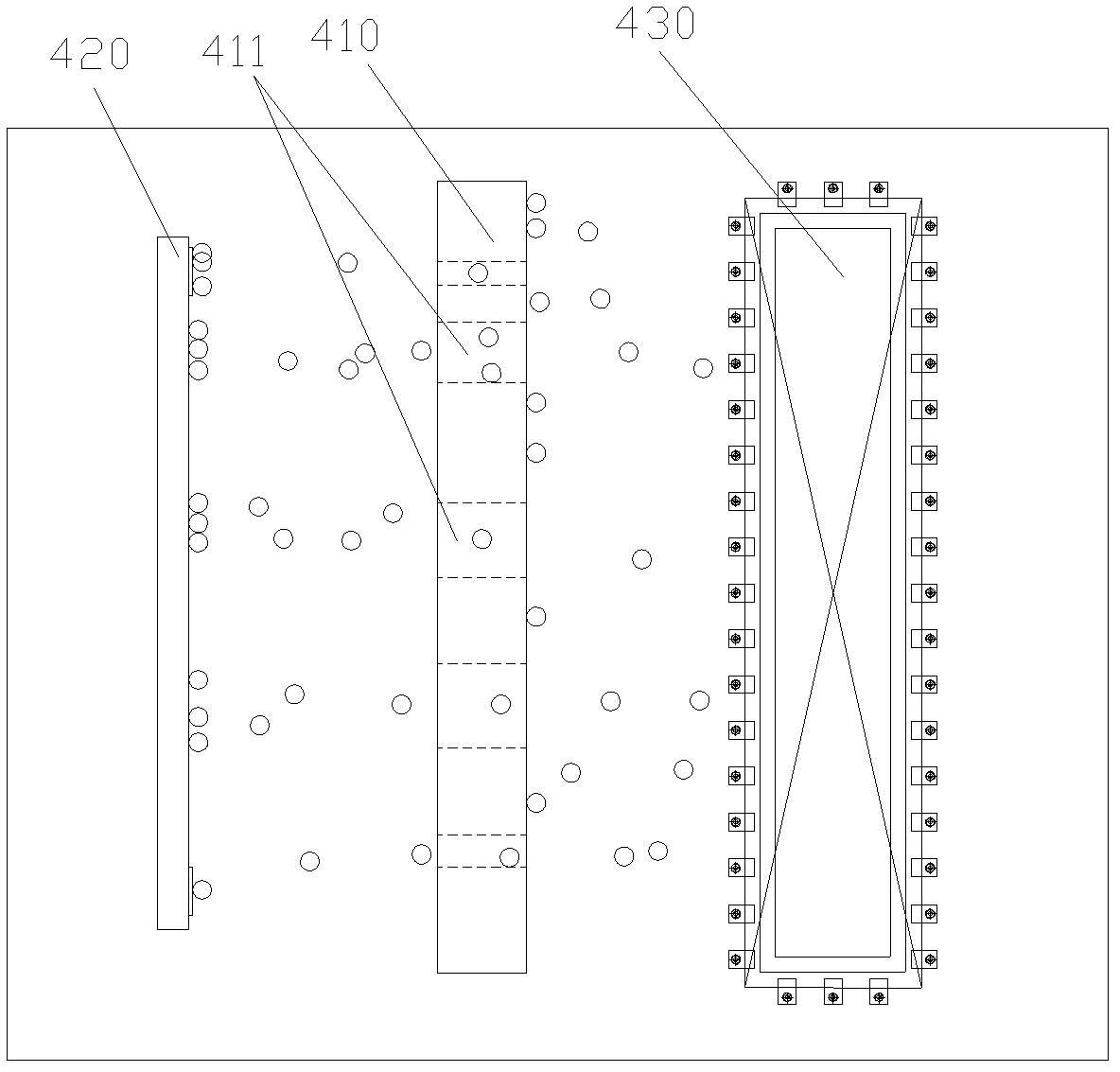

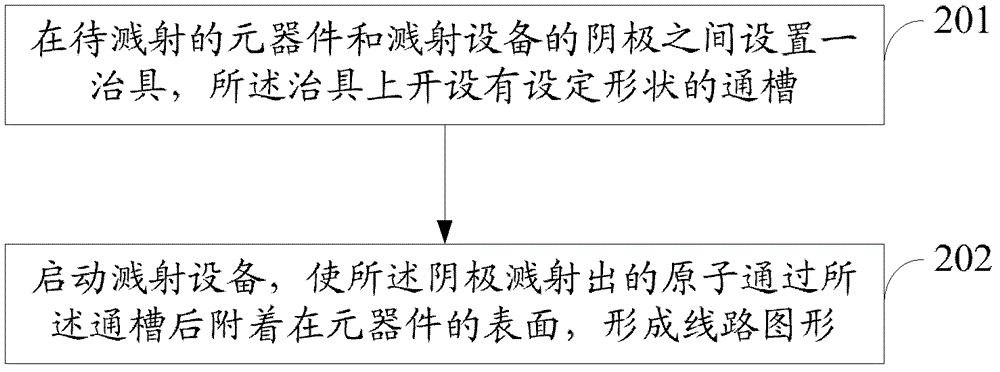

Method of manufacturing circuit pattern through sputtering technology and rewiring method of chip

ActiveCN102427058AFewer etch stepsShort processSemiconductor/solid-state device manufacturingEngineeringCathode

The invention discloses a method of manufacturing a circuit pattern through a sputtering technology and a rewiring method of a chip; the method of manufacturing the circuit pattern through the sputtering technology comprises the following steps of: arranging a jig between a component to be sputtered and a cathode of sputtering equipment, and arranging a through groove with a set shape on the jig; starting the sputtering equipment, leading atoms sputtered by the cathode to pass through the through groove and then be adhered on the surface of the component, and forming the circuit pattern. According to the technical scheme of the embodiment, the circuit pattern with the set shape can be directly manufactured by sputtering; and compared with the traditional technical scheme of firstly sputtering a whole surface and then etching the circuit pattern, the technical scheme has the advantages that an etching step is omitted, a technological process is shortened and the technology difficulty is reduced.

Owner:SHENNAN CIRCUITS

A direct light-emitting micro-display array device and its preparation method

InactiveCN102820315BAchieve integrationImprove reliabilitySolid-state devicesSemiconductor devicesDisplay deviceProtection layer

The invention relates to a direct-light-emitting-type micro display array device and a preparation method thereof. A display array comprises a substrate epitaxial wafer, semiconductor matrix isolating regions, electron-type conducting layers, light emitting layers, hole-type conducting layers, electron-type conducting electrodes, hole-type conducting electrodes, isolating protection layers, anode lines and cathode lines. The preparation method comprises the steps of: etching an epitaxial layer by adopting a dry-process etching method to obtain the electron-type conducting layers and form a plurality of array units; implanting ions into the electron-type conducting layers till to a substrate by adopting an ion implantation method to realize isolation of adjacent units and obtain the semiconductor matrix isolating regions; evaporating metal through electron beams to form the electron-type conducting electrodes and leading out the cathode lines; depositing the isolating protection layers through PECVD (Plasma Enhanced Chemical Vapor Deposition); and evaporating metal through electron beams to form the hole-type conducting electrodes and leading out the cathode lines, wherein regions formed by the anode lines and the cathode lines which are spatially intersected are display pixels.

Owner:BEIJING UNIV OF TECH

Method of manufacturing circuit pattern through sputtering technology and rewiring method of chip

ActiveCN102427058BFewer etch stepsShort processSemiconductor/solid-state device manufacturingSputteringEngineering

Owner:SHENNAN CIRCUITS

Manufacture process of copper interconnection line

ActiveCN102938391BFewer etch stepsReduce manufacturing costSemiconductor/solid-state device manufacturingEtchingMetallurgy

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Simultaneous Etching Process of Dual Structure Contact Holes

ActiveCN103337475BReduce the process risk of abnormal connectionReduce lossesSemiconductor/solid-state device manufacturingRadiation controlled devicesEtchingDielectric layer

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A Via-First Dual Damascus Copper Interconnect Method for Reducing Redundant Metal Coupling Capacitance

ActiveCN103268864BImprove performanceCoupling capacitance is reduced or eliminatedSemiconductor/solid-state device manufacturingPhotosensitive material processingCapacitanceCoupling

The invention discloses a through-hole-priority dual damascene copper interconnection method for reducing coupling capacitance of redundant metal. According to the through-hole-priority dual damascene copper interconnection method for reducing the coupling capacitance of the redundant metal, a dielectric layer is firstly deposited on a substrate silicon wafer and then the dielectric layer is coated with first photoresist; a through hole and a redundant metallic groove are formed in a first photoresist film through exposure and development, and the metallic groove formed in the first photoresist penetrates through the first photoresist; in the same developing machine, the first photoresist is coated with a SAFIER to solidify the through hole and the redundant metallic groove which are formed in the first photoresist, the SAFIER can react with the surface of the first photoresist to form an isolating film which can not dissolve in second photoresist under the heating condition, and then the remaining SAFIER which does not react with the surface of the first photoresist is removed; the first photoresist on which the isolating film is formed is coated with the second photoresist, and the anti-etching capacity of the first photoresist is larger than that of the second photoresist; a metallic groove located in the through hole is formed in a second photoresist film through exposure and development.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

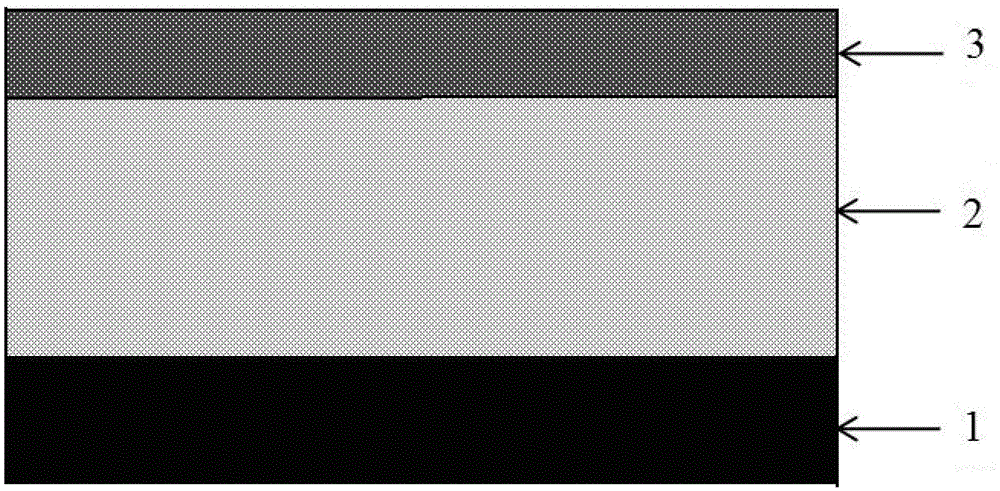

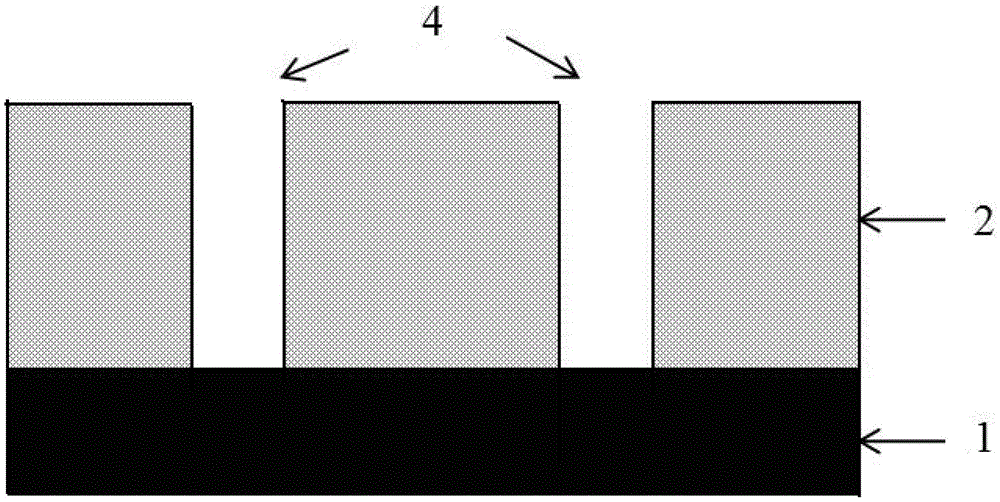

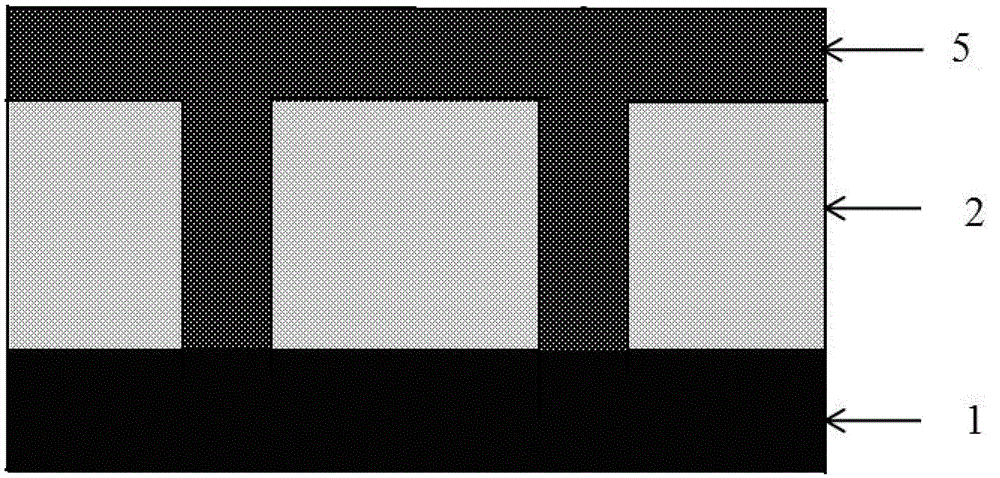

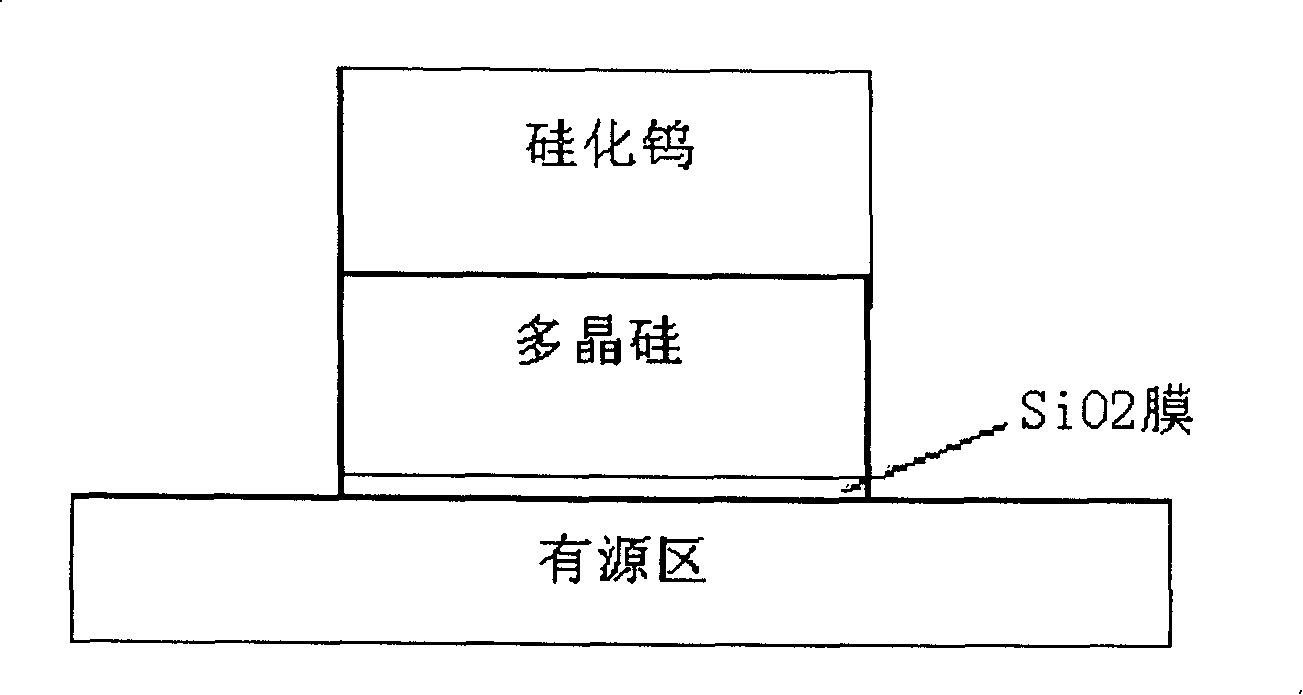

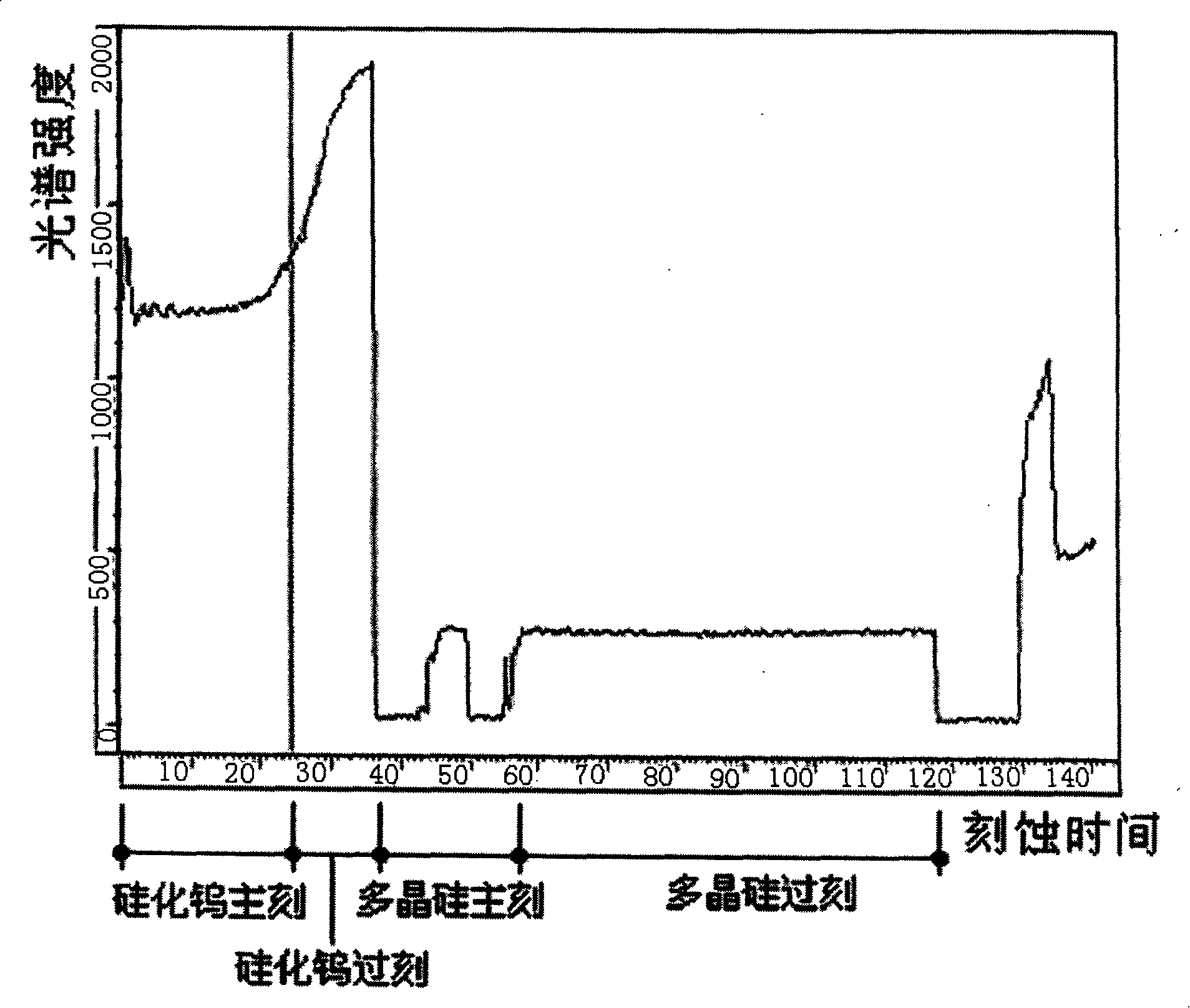

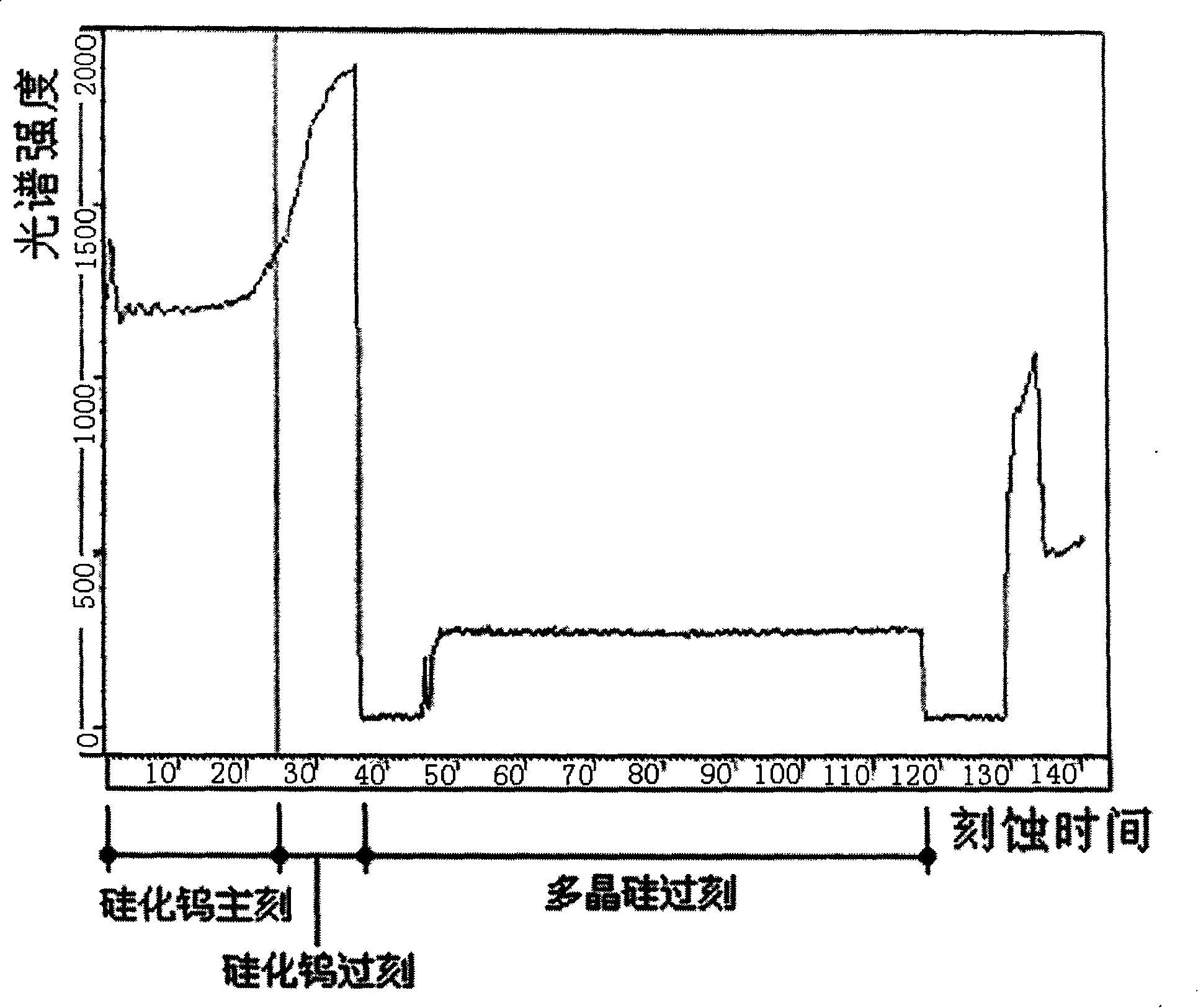

Method for etching tungsten-silicide silicon-die

ActiveCN101207038AImprove yieldFewer etch stepsSemiconductor/solid-state device manufacturingSalicideEtching

The invention discloses a method of etching the tungsten silicide silicon chips, which is used for etching process lines on a tungsten silicide silicon chip. The method comprises the following steps: tungsten silicide main etching, tungsten silicide excessive etching and polysilicon excessive etching, the tungsten silicide excessive etching and the polysilicon main etching in the prior art are combined into one step, thus reducing the etching steps, further reducing the particulate pollution and defects generated during the technological process, improving the defect-free rate of the silicon chip, and improving the production efficiency. The invention is mainly suitable for etching the tungsten silicide silicon chips, and is also suitable for etching other metal silicide silicon chips.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD