Impedance simulation method for chip capacitor in power-supply distribution network

A technology of power distribution network and simulation method, applied in the field of power distribution network decoupling system design, can solve the problems of difficult resonance point measurement, large parasitic inductance, large package volume, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The specific implementation and effect of the present invention will be further described below in conjunction with accompanying drawing:

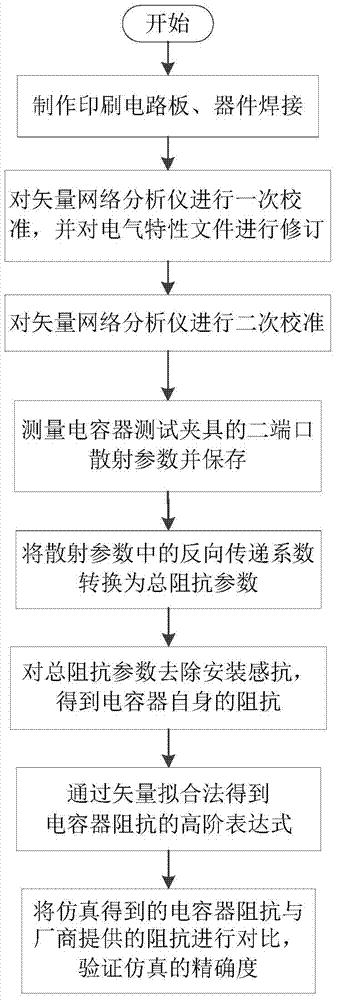

[0044] refer to figure 1 , the implementation steps of the present invention are as follows:

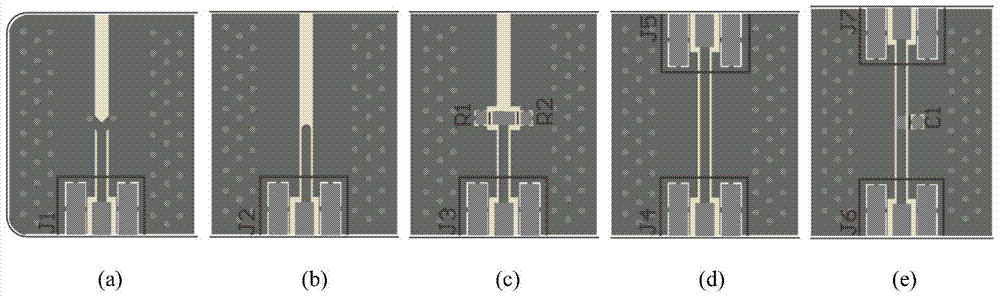

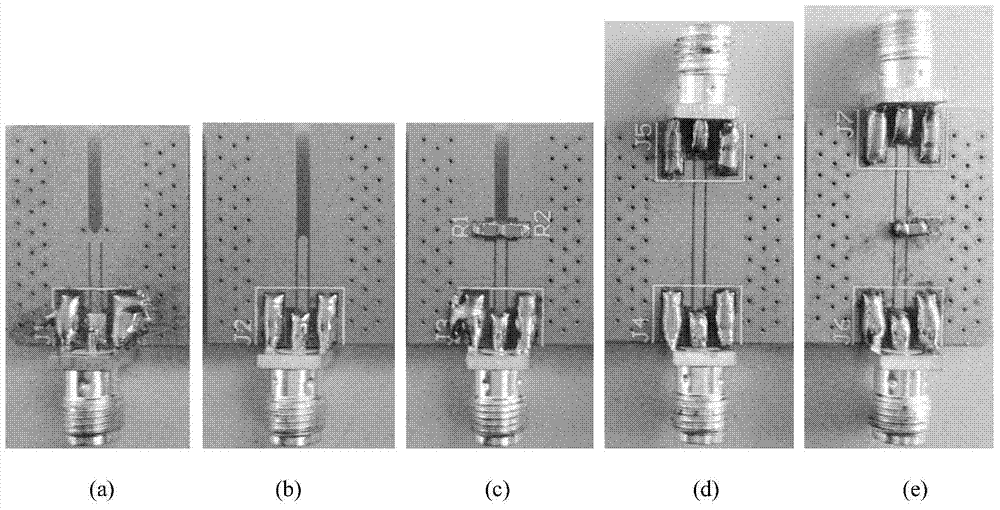

[0045] Step 1. Design a printed circuit board for a two-port test fixture for M types of capacitors, M≥1:

[0046] (1a) Basic parameter design

[0047] The printed circuit board of the two-port test fixture for each type of capacitor is set with the same parameters, that is, the dielectric material is FR4, the conductor material is copper, the solder resist material is green oil, and the transmission line is a grounded coplanar waveguide transmission line with a characteristic impedance of 50Ω. The central body of the transmission line is arranged in the middle of the printed circuit board, and the upper ground plane of the transmission line is connected to the lower ground plane of the transmission line through a via hole;

[0048] (1b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More