Formation method for transistor

A transistor and gas technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as unstable performance of transistors, and achieve the effect of stable performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

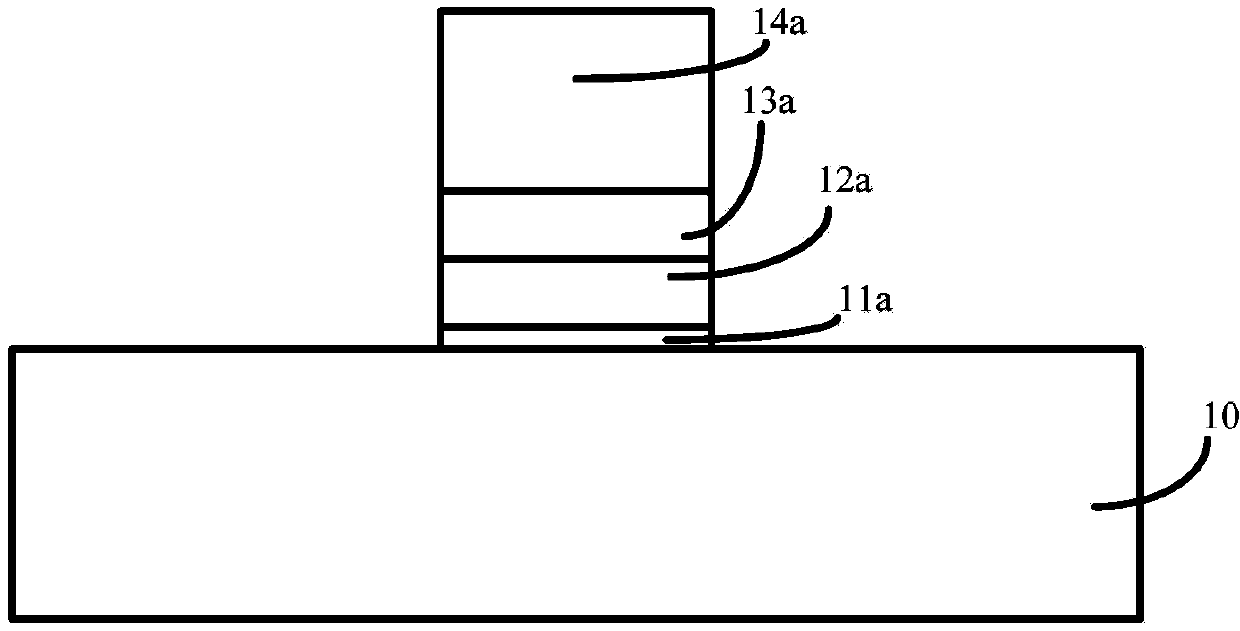

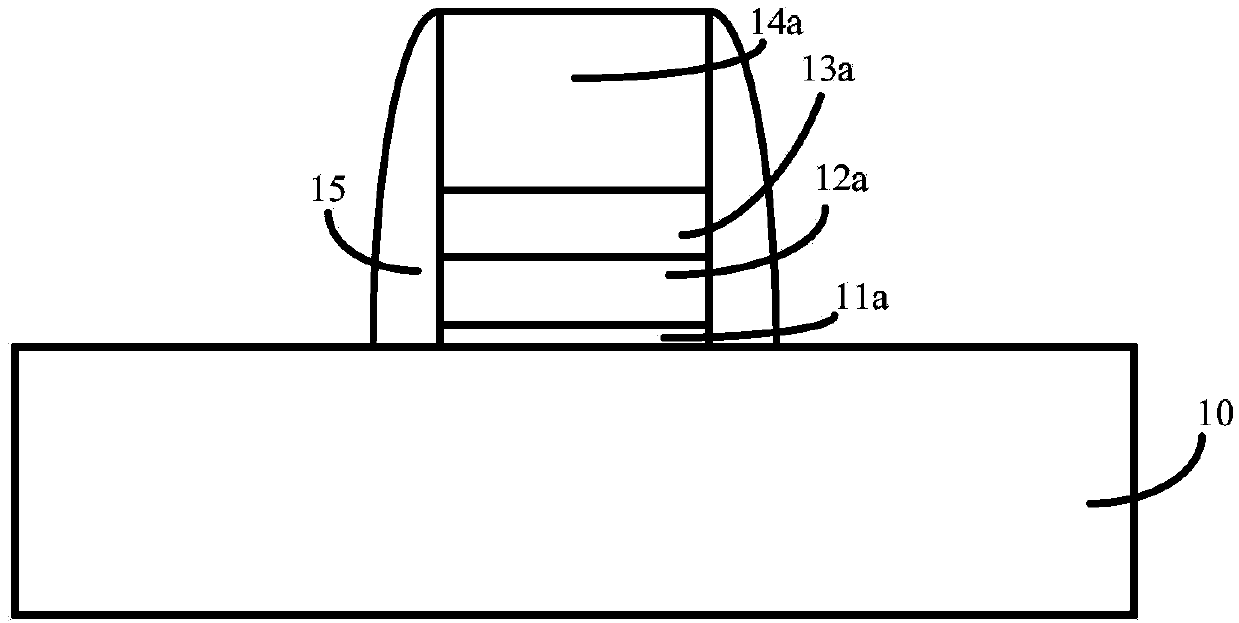

[0047] Figure 7 to Figure 10 It is a schematic cross-sectional structure diagram of the first embodiment of the formation process of the transistor of the present invention.

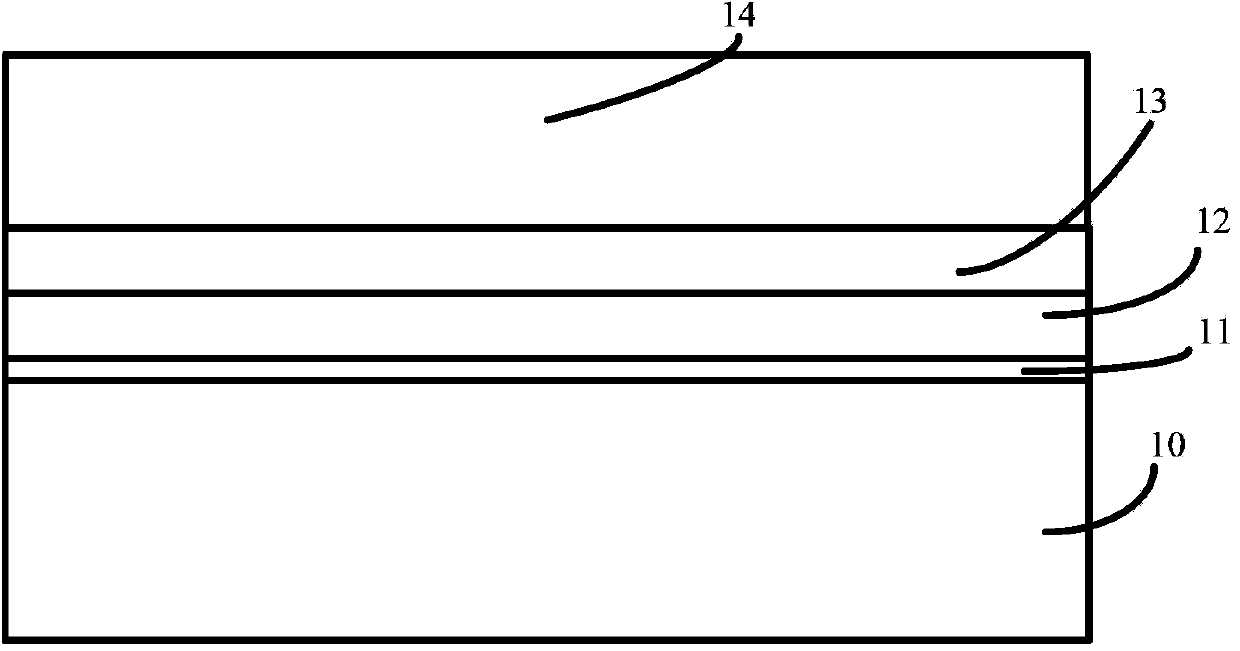

[0048] Please refer to Figure 7 , providing a semiconductor substrate 200; forming an insulating film 201 on the surface of the semiconductor substrate 200, a high-K dielectric film 202 on the surface of the insulating film 201, a protective film 203 on the surface of the high-K dielectric film 202, and a The gate electrode film 204 on the surface of the protection film 203 .

[0049] The semiconductor substrate 200 is used to provide a working platform for subsequent processes, and the material of the semiconductor substrate 200 is silicon, silicon germanium, silicon carbide, silicon-on-insulator or III-V compounds (silicon nitride or gallium arsenide, etc. ).

[0050] The material of the insulating film 201 is silicon oxide, and the forming process is a thermal oxidation process or a chemical vapo...

no. 2 example

[0075] Figure 11 to Figure 13 It is a schematic cross-sectional structure diagram of the second embodiment of the formation process of the transistor of the present invention.

[0076] Please refer to Figure 11 , providing a semiconductor substrate 300; on the surface of the semiconductor substrate 300, an insulating layer 301, a high-K dielectric layer 302 located on the surface of the insulating layer 301, and a The protective layer 303, and the gate electrode layer 304 located on the surface of the protective layer 303; after etching, the gate electrode layer 304, the protective layer 303, the high-K dielectric layer 302 and the insulating layer 301 are cleaned; after cleaning , performing thermal annealing, the gas of the thermal annealing is hydrogen; and, after cleaning, forming First spacers 305; after thermal annealing and formation of first spacers 305, lightly doped regions 306 are formed on both sides of the gate electrode layer 304 and first spacers 305; after ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More