Method for preparing h-BN medium graphene integrated circuits on large scale

A large-scale graphene technology, applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve problems such as low yield, high process difficulty, and poor performance, so as to improve performance, simplify the process, and promote development Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

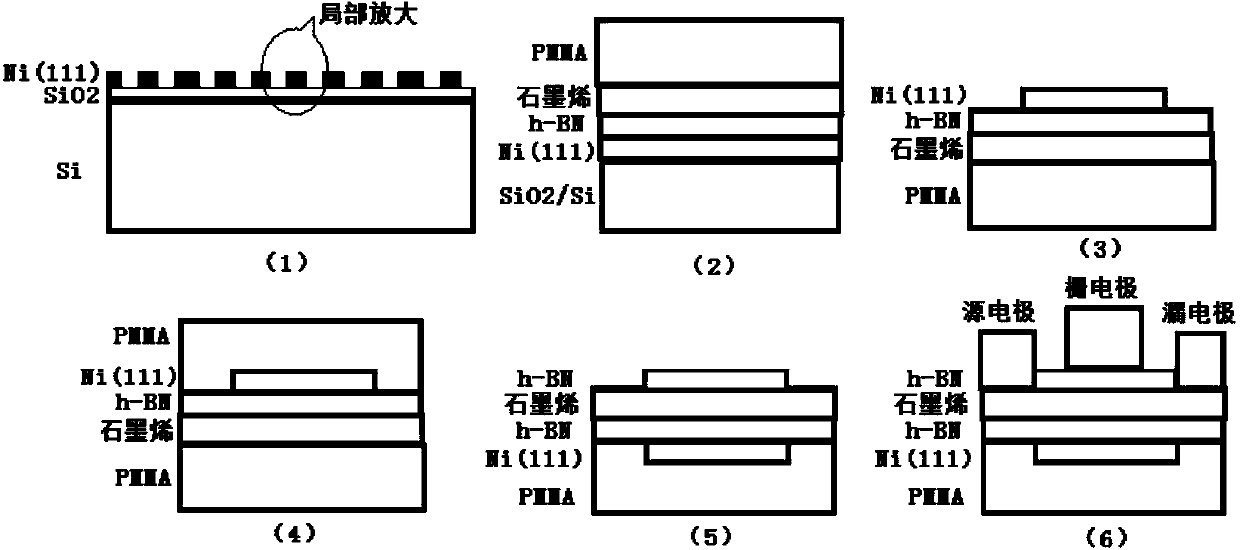

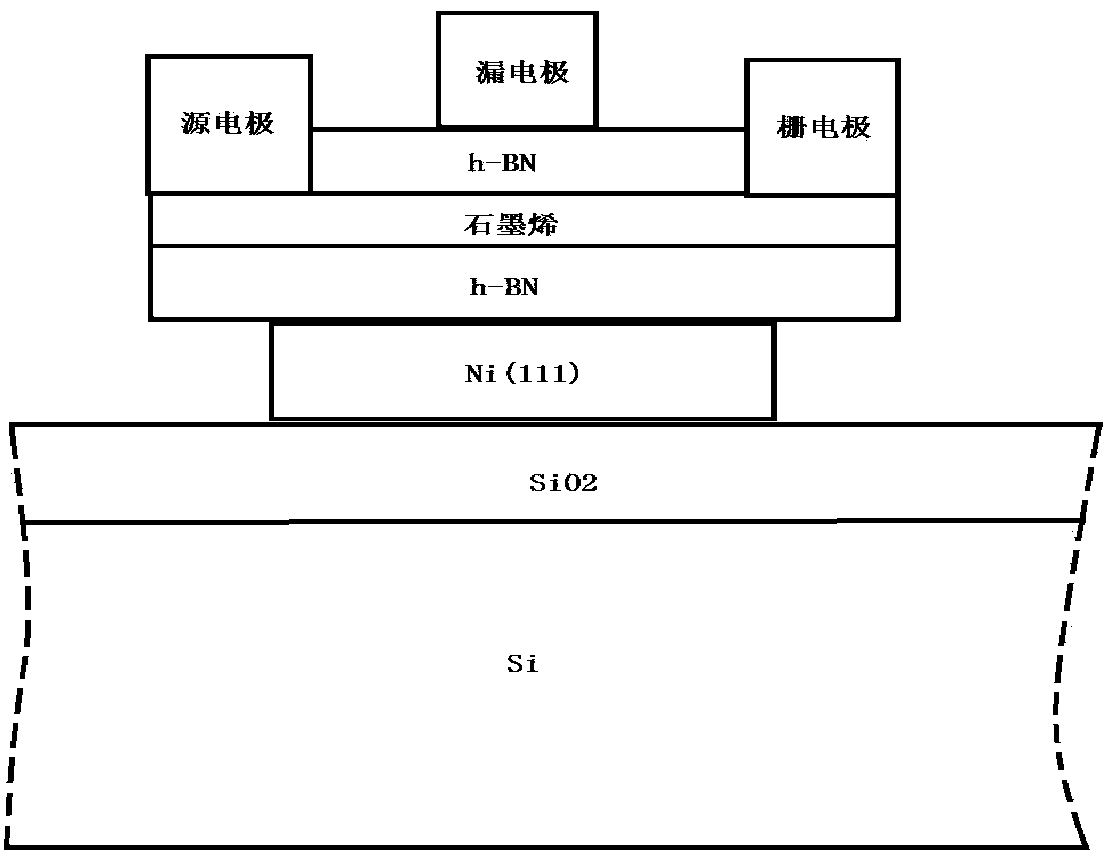

[0040] Embodiment: the preparation of large-scale h-BN dielectric graphene integrated circuit

[0041] In making large-scale h-BN dielectric graphene integrated circuits, the present invention takes the following technical solutions:

[0042] 1. Making SiO2 2 / Si substrate: 300nm SiO grown on a 4-inch Si wafer by dry oxidation 2 film;

[0043] 2. Catalytic metal layer growth: using electron beam evaporation process on SiO 2 A layer of Ni(111) film with a thickness of 250nm was grown on the Si substrate;

[0044] 3. Catalytic metal layer photolithography: use standard photolithography process to photolithographically prepare the catalytic metal layer on the Si wafer, each with a square catalytic metal pattern;

[0045]4. Bottom layer h-BN medium growth: use CVD method to selectively grow a layer of hexagonal boron nitride (h-BN) on the Ni(111) layer, with a thickness of about 20nm, and the grown h-BN pattern is similar to Ni(111) ) with the same graphics;

[0046] 5. Grap...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More