Small-sized high-speed large dynamic digital receiver system and method

A digital receiver and large dynamic technology, applied in the field of signal processing, can solve the problems of high power consumption, low utilization of logic resources, large size, etc., and achieve the effects of increased signal processing capability, enhanced hardware reliability, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

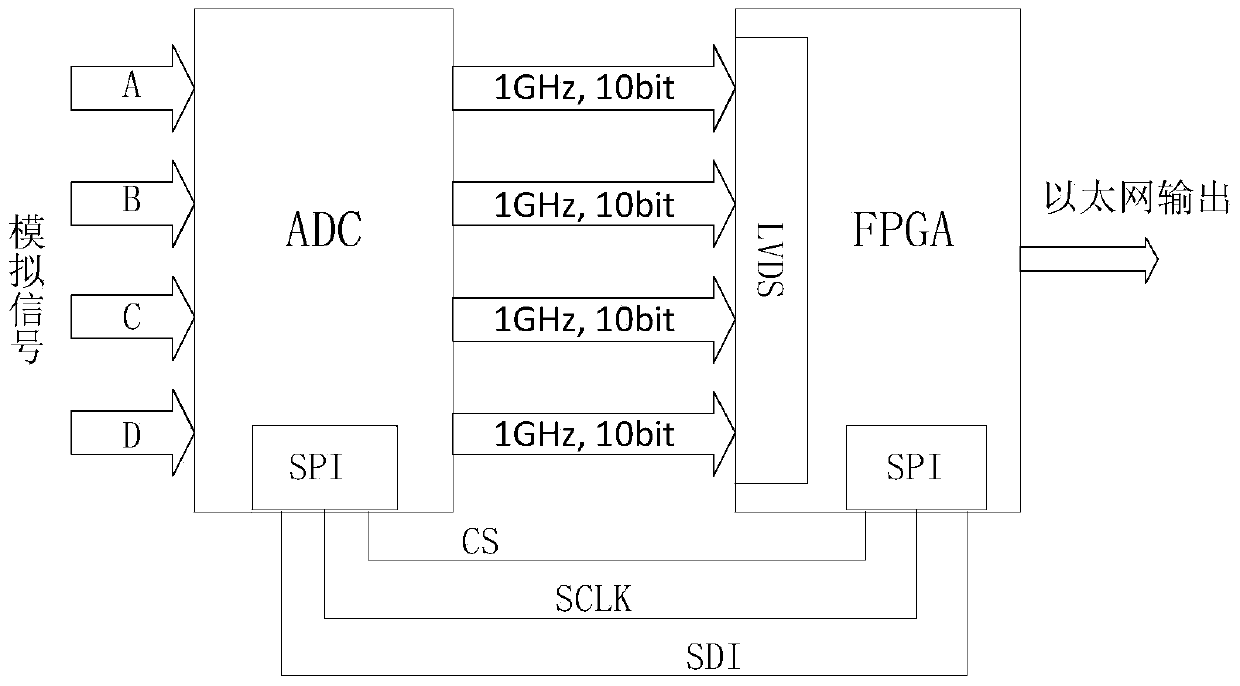

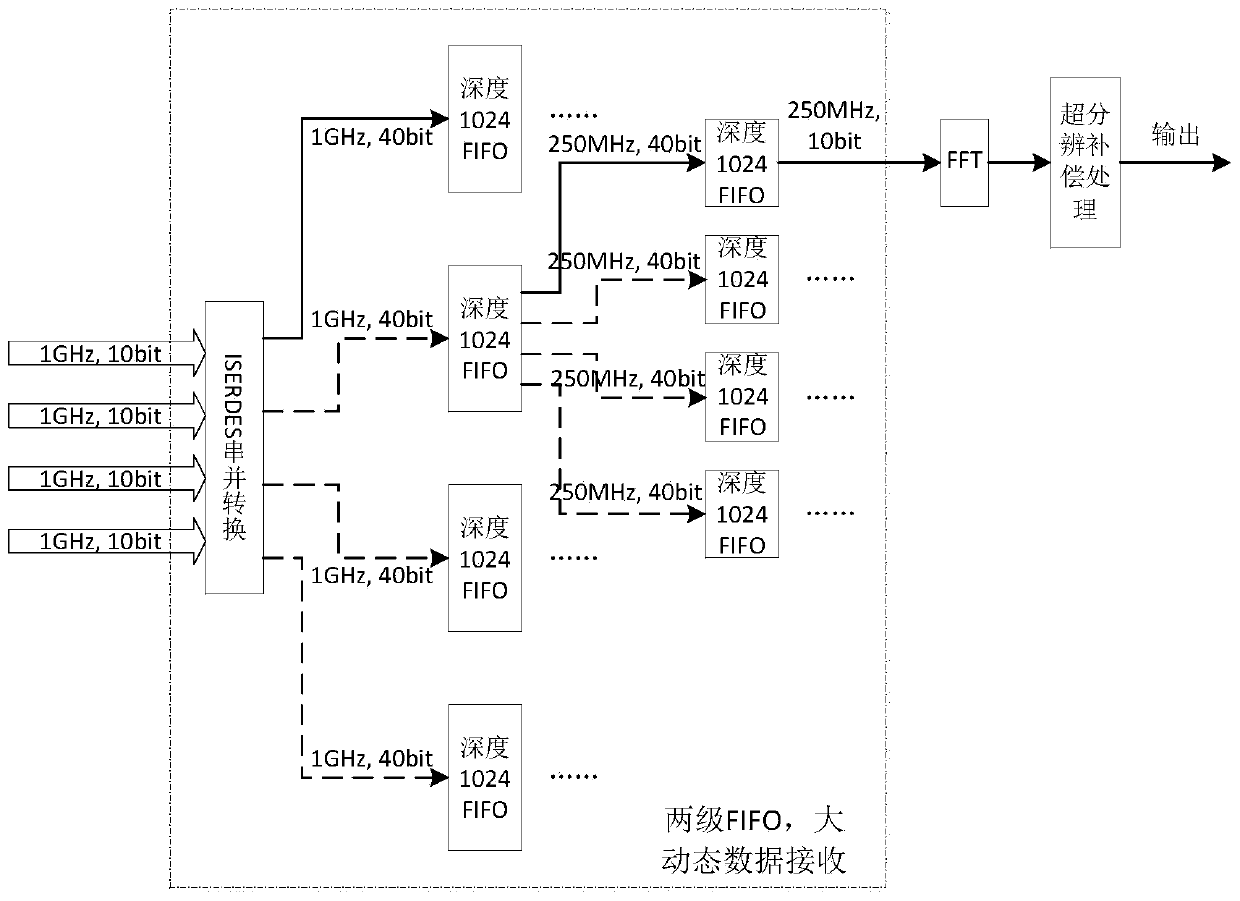

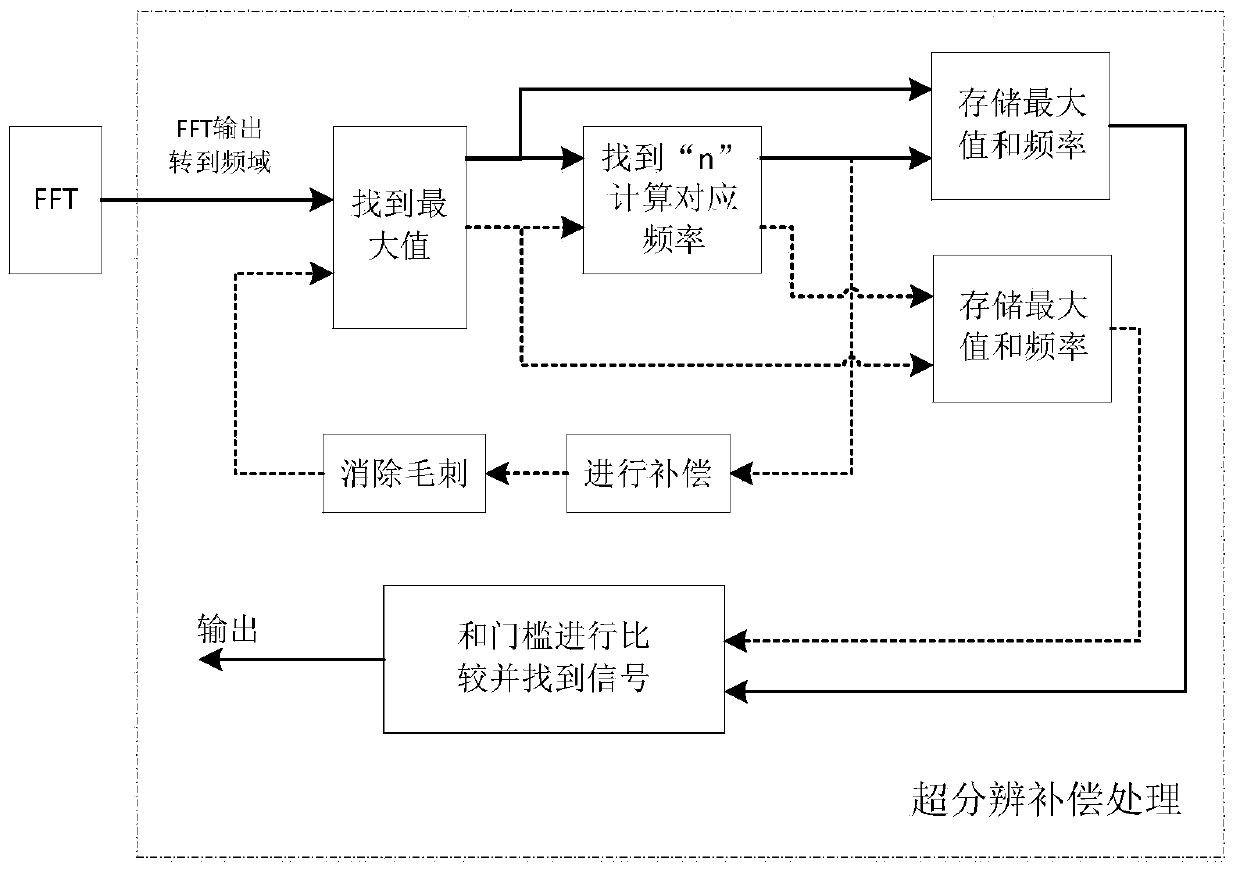

[0039] The present invention is firstly a small-sized high-speed large dynamic digital receiver system, including an analog-to-digital conversion part and a signal extraction part, see appended figure 1 , The analog-to-digital conversion part of the small high-speed and large-dynamic digital receiver system uses a high-speed digital signal acquisition ADC chip to realize the analog-to-digital conversion of the analog signal collected by the radar. The intermediate frequency signal collected by the radar antenna is connected to the ADC chip through the SMA interface. The signal extraction part of the small high-speed and large dynamic digital receiver system uses a digital signal processing FPGA chip to realize signal extraction. The output of the ADC chip is directly connected to the logic function module of the FPGA through 48 data lines, and one or more of the FPGA chip outputs The digital target signal is output through Gigabit Ethernet, and the output signal is used for rad...

Embodiment 2

[0046] The overall composition and connection mode of the small-scale high-speed large-dynamic digital receiver system are the same as those in Embodiment 1. Reference attached figure 1 , the digital receiver system in this example uses a high-speed ADC chip and a FPGA chip as the basic structure, and consists of two parts: digital-to-analog conversion and signal extraction. The FPGA chip of the signal extraction part is connected with an Ethernet physical layer chip to form a connection with the radar subsequent processing. The Ethernet physical layer chip is used to realize the physical layer output of the target signal through Ethernet.

[0047] In this example, the ADC chip of the analog-to-digital conversion part adopts the EV10AQ190 chip of E2V Company, and the FPGA chip of the signal extraction part adopts the VIRTEX-6 series XC6VLX315T chip of Xilinx Company.

[0048] The EV10AQ190 chip integrates 4 channels of 10-bit ADC cores. In the four-channel mode, the maximum s...

Embodiment 3

[0051] The overall structure and connection mode of the small-scale high-speed large-dynamic digital receiver system are the same as those in Embodiment 2. The EV10AQ190 chip can have a four-channel working mode, a dual-channel working mode and a single-channel working mode. Different working modes are controlled through the SPI digital interface connected to the FPGA.

[0052] In this example, the EV10AQ190 chip uses alternate sampling technology, so that the A, B, C, and D channels of the chip alternately sample one analog signal, achieving a sampling rate up to 4Gsps and a sampling bit width of 10bit. Use the LVDS DDR data output mode to reduce the associated clock by half, which is beneficial to the reception of data by the back-end FPGA. The EV10AQ190 chip has a high signal-to-noise ratio, and the bit error rate is as low as 10 when sampling at full speed -16 , to ensure the accuracy of signal sampling. The EV10AQ190 chip also has a large industrial-grade temperature ra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More