Array substrate, preparing method thereof and display device

A technology of an array substrate and a manufacturing method, applied in the display field, can solve the problems of decreased product yield, low production efficiency, high alignment accuracy, etc., and achieve the effects of small parasitic capacitance and excellent electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] An embodiment of the present invention provides a method for manufacturing an array substrate, and the method includes the following steps:

[0041] Step S21: providing a base substrate 201, such as figure 2 shown.

[0042] In order to ensure better performance of the product, it is preferable to perform initial cleaning on the base substrate 201 to remove impurity particles remaining on the surface of the base substrate during the production process.

[0043] The specific material of the provided base substrate 201 can be determined according to the actual situation. If the display device to be produced is non-flexible, the base substrate 201 is preferably a glass substrate. If a flexible or bendable display device needs to be produced, Then, the base substrate 201 may preferably be a flexible or bendable material such as a plastic film.

[0044] Step S22: forming a buffer layer 202 on the base substrate 201, such as image 3 shown.

[0045] Specifically, PECVD (P...

Embodiment 2

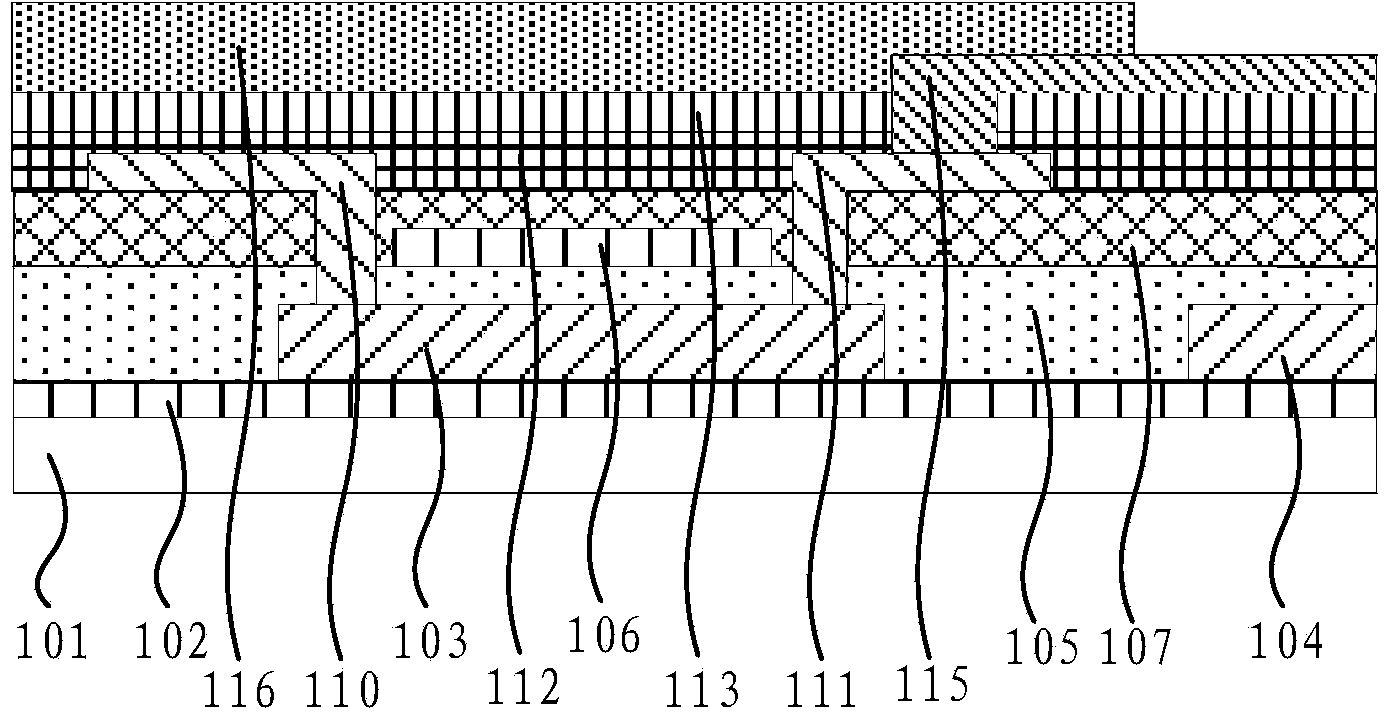

[0121] This embodiment provides an array substrate, such as Figure 13 As shown, the array substrate provided in this embodiment includes: an active layer 203 on the base substrate 201; a gate insulating layer 205 covering the active layer 203; Gate 206, source 207, drain 208, gate line and data line, gate line or data line are disconnected at the intersection of gate line and data line; cover gate 206, source 207, drain 208 , the passivation layer 209 of the gate line and the data line; the source contact hole, the drain contact hole and the bridge structure contact hole located inside the passivation layer 209 and the gate insulating layer 205, and the source contact hole exposes part of the source electrode 207 and part of the active layer 203, the drain contact hole exposes part of the drain electrode 208 and part of the active layer 203, and the bridge structure contact hole exposes part of the disconnected gate line or data line; the source located in the same film layer...

Embodiment 3

[0135] Based on the second embodiment, this embodiment provides a display device, which includes the array substrate described in the second embodiment.

[0136] The display device provided in this embodiment can preferably be an OLED (Organic Light Emitting Diode, organic light emitting diode) display device, such as: AMOLED (Active Matrix Organic Light Emitting Diode, active matrix organic light emitting diode) display device; it can also be LCD (Liquid Crystal Display, liquid crystal display device), such as: IPS (In-Plane Switching, in-plane switching) type LCD, etc.

[0137] In the display device provided by this embodiment, the gate and the source and drain of the TFT are in the same film layer, so there is no parasitic capacitance between the gate and the source and drain, thereby improving the performance of the display device.

[0138] Moreover, since the array substrate of the display device in this embodiment can be fabricated using fewer patterning processes, the p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More