Thick-film coating process for preparing TSV three-dimensional integrated RDL electroplated mask

A mask and process technology, applied in the field of microelectronics, can solve the problems that affect the dimensional accuracy of the electroplating pattern, the difficulty in obtaining the ideal film, and the increase in the thickness of the secondary coating, so as to improve the reliability of electrical interconnection and improve the electrical interconnection. The effect of improving the connection characteristics and improving the surface uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

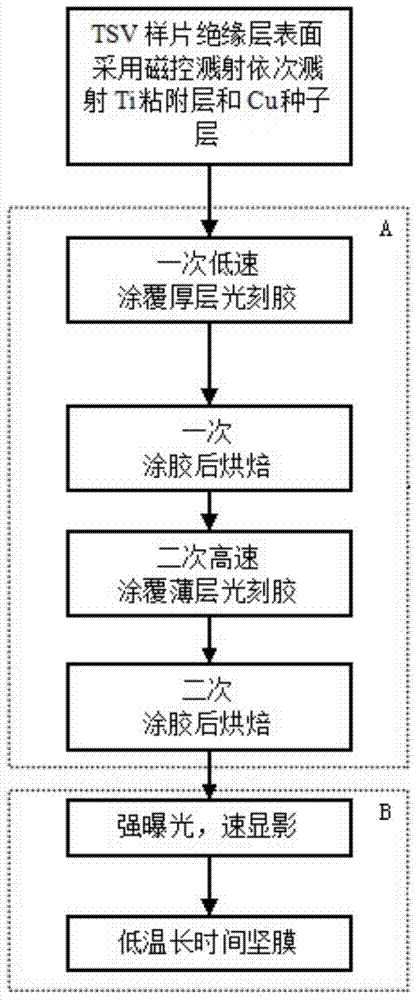

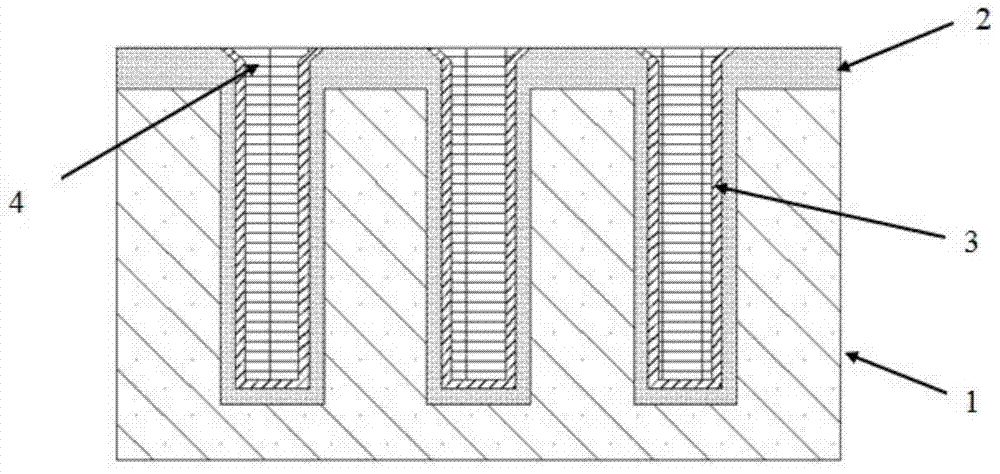

[0038]This embodiment is used to make a high RDL line electroplating mask on the surface of the insulating layer of the TSV blind via electroplating wafer, the average thickness of the mask is 25.96 μm, and the TTV is less than 1.5 μm. Such as figure 2 As shown, the TSV blind hole electroplating operation wafer adopts Si substrate 1, and SiO is arranged between the blind hole and Si substrate 1. 2 Insulating layer 2, the wall of the blind hole is provided with Ti adhesion layer 3 and Cu column 4 sequentially from outside to inside, and the implementation steps of its electroplating mask are as follows, as figure 1 Shown:

[0039] Step 1. First, use acetone and isopropanol to ultrasonically clean the operating wafer for 5 minutes respectively to remove the polishing liquid particles and impurities remaining in the CMP process; 2 On the insulating layer 2, a 100nm Ti adhesion layer 3 and a 600nm Cu seed layer, namely the UBM layer, are sequentially sputtered, such as image ...

example 2

[0052] The present invention is a thick glue process for preparing TSV three-dimensionally integrated RDL electroplating mask, and the specific process steps are as follows:

[0053] Step 1, one glue coating is divided into two steps: Step1 rotates at 600rpm, spin coating time is 5s, and acceleration is 6000rpm / s; Step2 rotates at 1000rpm, spins for 30s, and accelerates at 10000rpm / s.

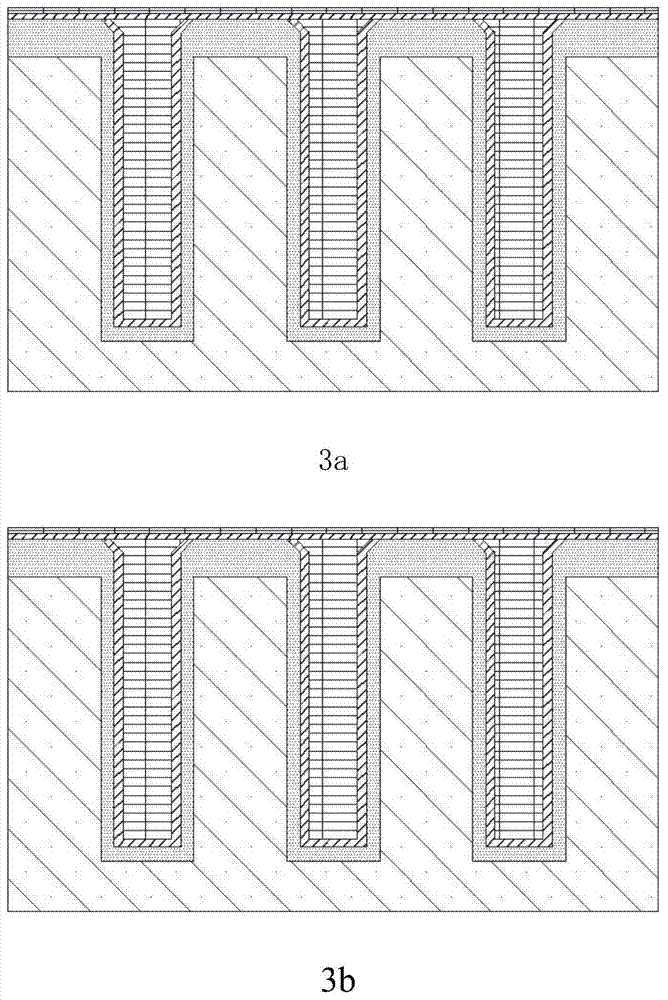

[0054] Step 2: Baking after coating once, the baking temperature is 100°C, and the baking time is 3 minutes, such as image 3 As shown in b, the time interval between primary baking and secondary gluing is 1min.

[0055] Step 3, the second glue coating is divided into three steps: Step1 is 400rpm, time is 4s, acceleration is 6000rpm / s; Step2 is 1000rpm, time is 4s, acceleration is 8000rpm / s; Step3 is 3000rpm, spin coating The time is 40s and the acceleration is 10000rpm / s.

[0056] Step 4, bake after the second glue coating, the baking temperature is 100°C, and the baking time is 7 minutes, s...

example 3

[0060] The present invention is a thick glue process for preparing TSV three-dimensionally integrated RDL electroplating mask, and the specific process steps are as follows:

[0061] Step 1, one glue application is divided into two steps: Step1 rotates at 500rpm, spin coating time is 6s, and acceleration is 6000rpm / s; Step2 rotates at 1000rpm, spins for 35s, and accelerates at 10000rpm / s.

[0062] Step 2: Baking after coating once, the baking temperature is 100°C, and the baking time is 3 minutes, such as image 3 As shown in b, the time interval between primary baking and secondary gluing is 1min.

[0063] Step 3, the second glue coating is divided into three steps: Step1 rotates at 400rpm, time is 3s, acceleration is 6000rpm / s; Step2 rotates at 1300rpm, time is 5s, acceleration is 8000rpm / s; Step3 rotates at 4000rpm, spin coating The time is 35s and the acceleration is 10000rpm / s.

[0064] Step 4, bake after the second glue coating, the baking temperature is 100°C, and the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| The average thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More