Transverse diffusion semiconductor device and preparation method thereof

A semiconductor and device technology, which is applied in the field of lateral diffusion semiconductor devices and their preparation, can solve the problems of low breakdown voltage, easy source and drain breakdown, and failure to meet the needs of device development.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

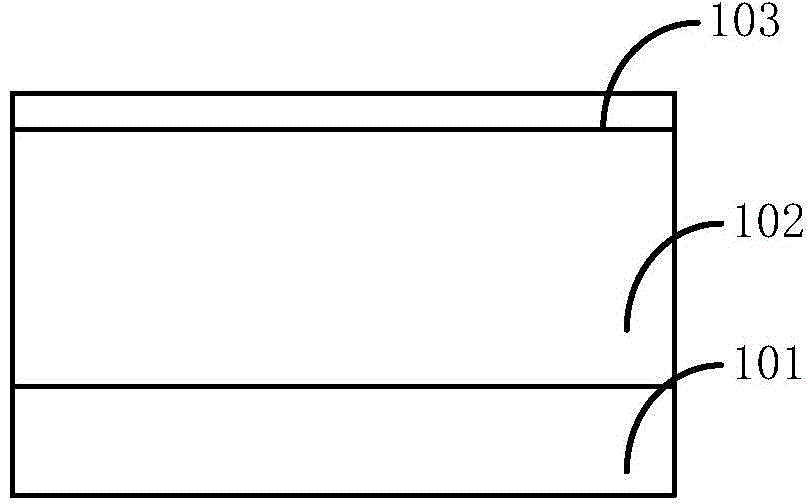

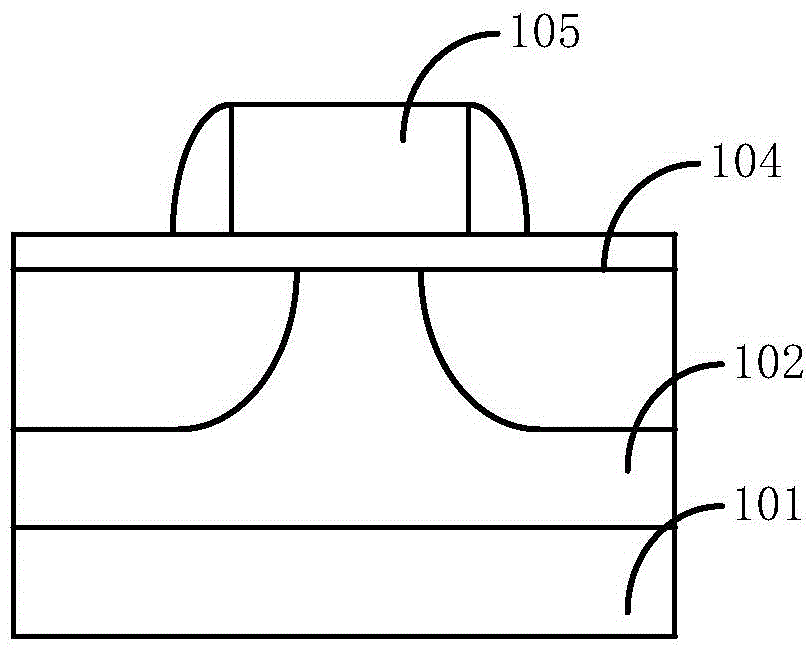

[0046]First, step 201 is performed to provide a semiconductor substrate 201 in which a well region 202 is formed.

[0047] Specifically, refer to Figure 2a , including a semiconductor substrate 201, wherein the semiconductor substrate 201 can be silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), silicon-germanium-on-insulator ( SiGeOI) and germanium on insulator (GeOI), etc.

[0048] A well region 202 is formed in the semiconductor substrate 201, which has a first conductivity type. In a specific embodiment of the present invention, the first well region is N+ or P+ doped, for example, N-type dopant (such as phosphorus) is implanted into the semiconductor substrate, and the dopant is driven in by a heat treatment process, thereby forming the N-type well region.

[0049] Before performing ion implantation to form the well region 202, it also includes the step of forming a shielding layer (screen) (not shown in the fig...

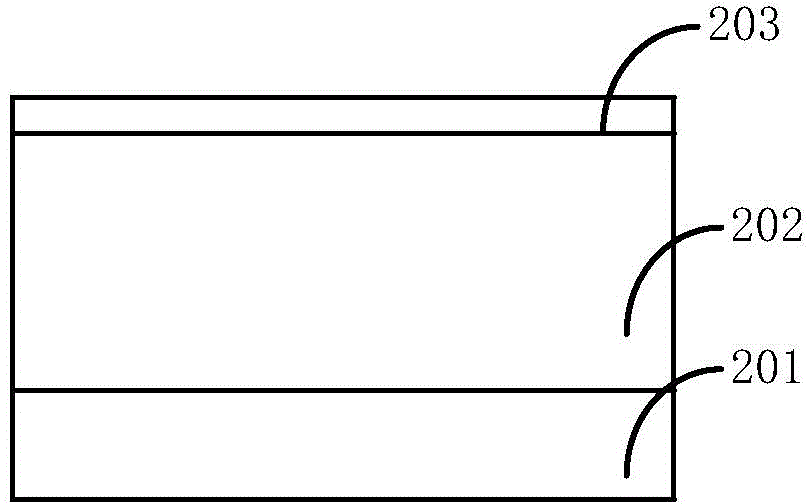

Embodiment 2

[0079] As a preferred embodiment, such as Figure 3a-3b As shown, after forming the well region 202 and before forming the drift region, a step of forming a shallow trench isolation structure in the well region 202 is also included.

[0080] A method for forming a shallow trench isolation structure includes the following steps:

[0081] First, a first oxide layer and a first nitride layer are sequentially formed on the semiconductor substrate 201 . The first oxide layer can be obtained by high temperature oxidation, and its thickness can be 100-200 angstroms. The first oxide layer may serve as an isolation layer to protect the semiconductor substrate 301 from damage and contamination. The first nitride layer may be formed by a chemical vapor deposition (CVD) method, a physical vapor deposition (PVD) method, an atomic layer deposition (ALD) method, or the like. As an example, the first nitride layer may be formed by low pressure chemical vapor deposition using ammonia and di...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com