III-V family nitride semiconductor epitaxial structure, device comprising epitaxial structure and preparation method thereof

A nitride semiconductor, III-V technology, used in semiconductor devices, electrical components, circuits, etc., can solve the problems of affecting device consistency, small process window, and high production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

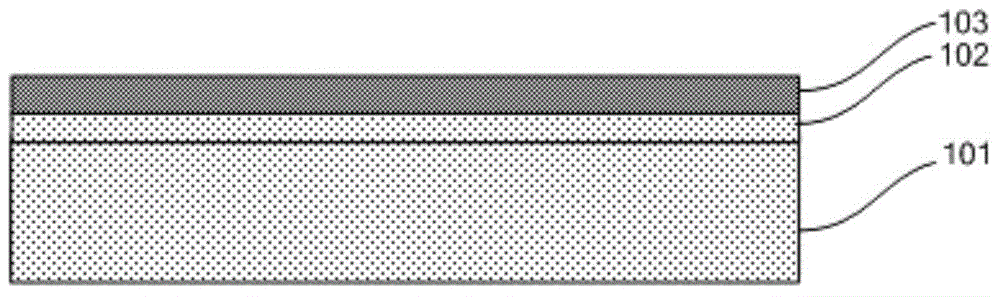

[0130] Such as Figure 1 - Figure 1 As shown in 1, this embodiment provides a III-V group nitride device structure including a microscopic cavity structure and a manufacturing method thereof, comprising the following steps:

[0131] 1. If figure 1 As shown, in this embodiment, the growth substrate 101 is a commercially available flat Al 2 o 3 The substrate, whose surface crystal orientation (0001), has atomic-level flatness. In this embodiment, a no-clean substrate is used, which can be used directly without cleaning. Place the above substrate on a graphite tray with a SiC protective layer and send it into a metal organic chemical vapor deposition (MOCVD) reaction chamber; heat the above substrate to 1100°C under a hydrogen atmosphere and keep it at this temperature for 10 minutes ; Then the substrate temperature is reduced to 550°C, and ammonia gas, trimethylaluminum (TMAl) and trimethylgallium (TMGa) are simultaneously fed into the reaction chamber, wherein the standard...

Embodiment 2

[0153] Such as Figure 1 - Figure 1 As shown in 1, the III-V group nitride device including the microscopic cavity structure provided by this embodiment, its basic steps are as in embodiment 1, the only difference is the third step: patterning the semiconductor dielectric layer 103 as periodic Sexually spaced SiO 2 Lines with a width of 7 μm at the bottom of the line and a spacing of 3 μm.

[0154] The luminous flux of the packaged 14mil*28mil LED chip prepared in this embodiment is 20.21lm, and its ESD human body model 4000V passing rate is 93% on average.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com