Low-temperature polycrystalline silicon thin film transistor and preparation method thereof

A technology of thin-film transistors and low-temperature polysilicon, which is applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., and can solve problems such as low production efficiency, increased process complexity, and high manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

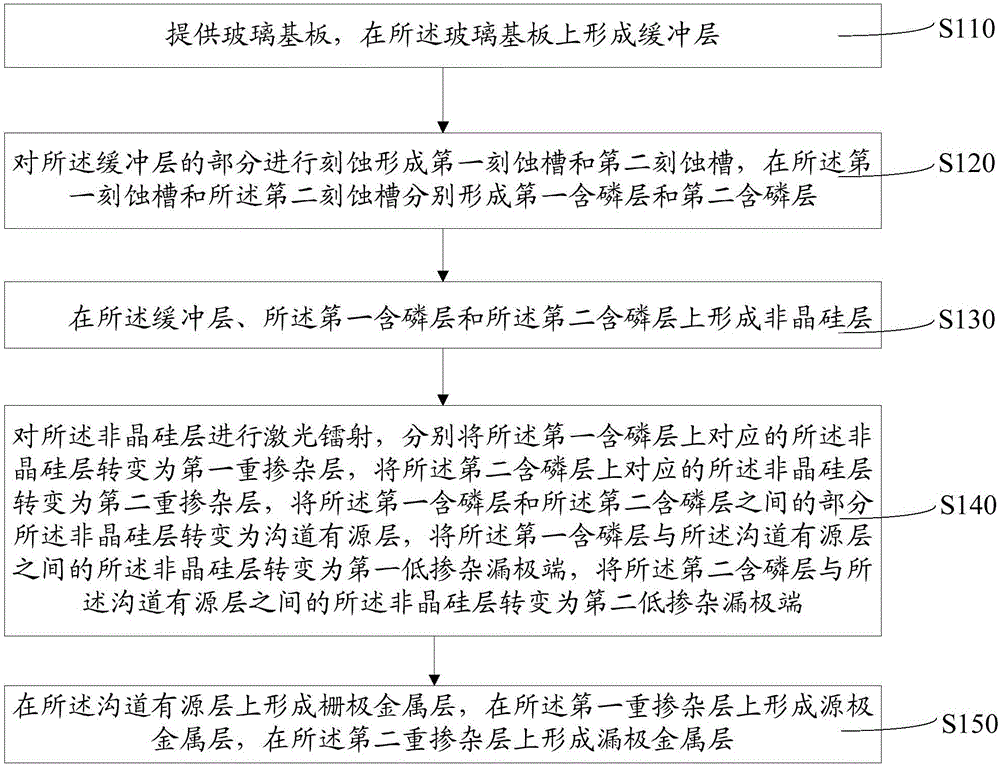

[0036] like figure 1 As shown, the method for preparing a low-temperature polysilicon thin film transistor according to an embodiment of the present invention includes the following steps:

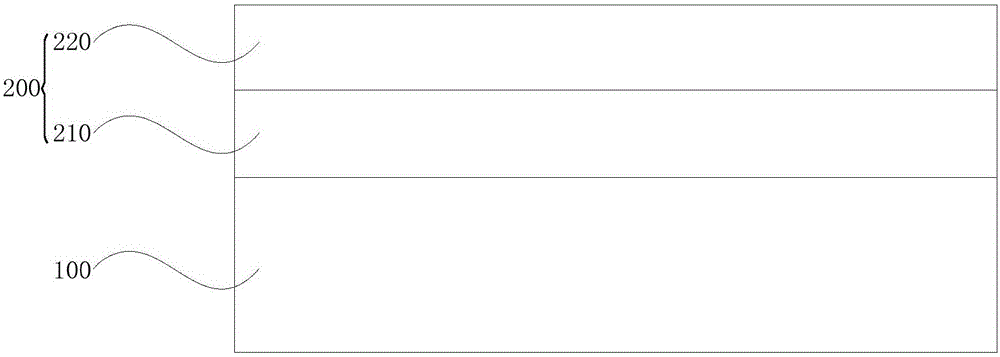

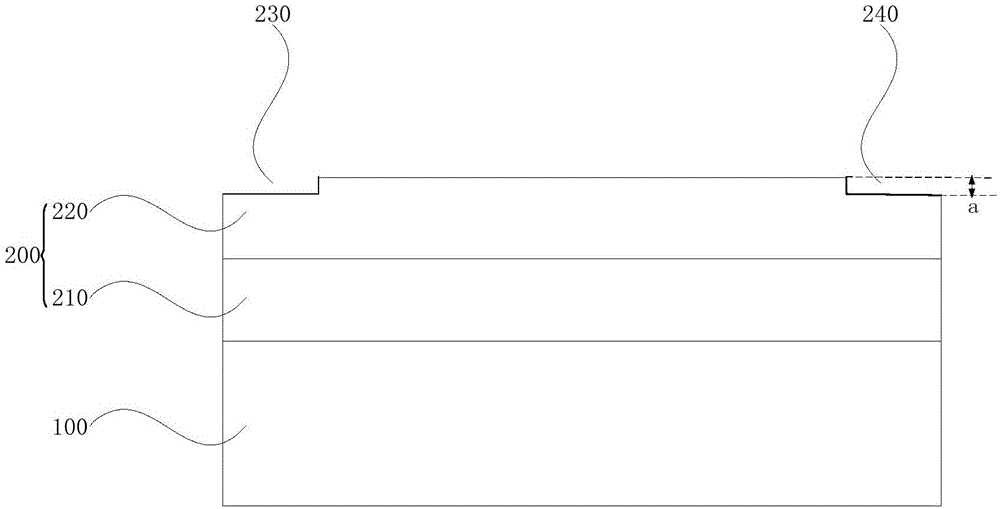

[0037] S110: Provide a glass substrate, and form a buffer layer on the glass substrate.

[0038] In practical applications, the glass substrate needs to have high transparency, low reflectivity, good thermal stability and corrosion resistance, high mechanical strength and good mechanical processing characteristics. In addition, the glass substrate also Good electrical insulation is required. Preferably, the glass substrate is borosilicate glass or alkali-free aluminosilicate glass without alkali ions.

[0039] In order to prevent the metal ions in the glass substrate from entering the amorphous silicon layer during the deposition process of the amorphous silicon layer, for example, the forming of the protective insulating layer buffer layer on the glass substrate specifically includes th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More