SOI base-based low-leakage and low-capacitance TVS array and preparation method thereof

A low-leakage, low-capacitance technology, which is applied in circuits, electrical components, and electric solid-state devices, can solve problems such as tunnel breakdown, thermal effects, and large leakage currents, so as to suppress the interference of pulse currents, avoid data transmission errors, and produce The effect of simple method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

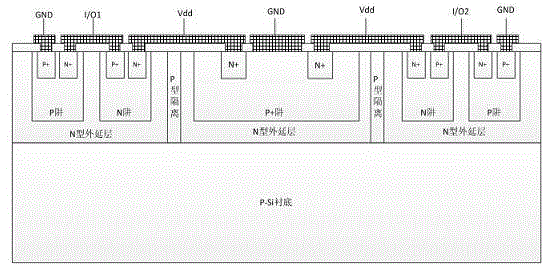

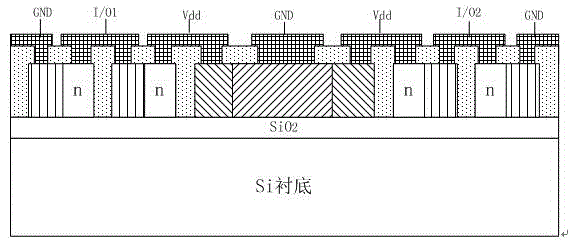

[0050] Such as figure 2 As shown in the structural diagram of the low-leakage and low-capacitance TVS device using the SOI substrate in the present invention, a low-leakage and low-capacitance TVS array based on the SOI substrate, with the SOI substrate as the main body, includes: n-type SOI substrate, p + region, n+ region, p region, silicon nitride isolation and electrode, the n-type SOI substrate is made of Si substrate, SiO 2 Layer and N-type and / or P-type Si three-layer structure, on the P-type and / or N-type Si substrate by diffusion or ion implantation to form a highly doped PN junction, forming the PN junction region and the central TVS region.

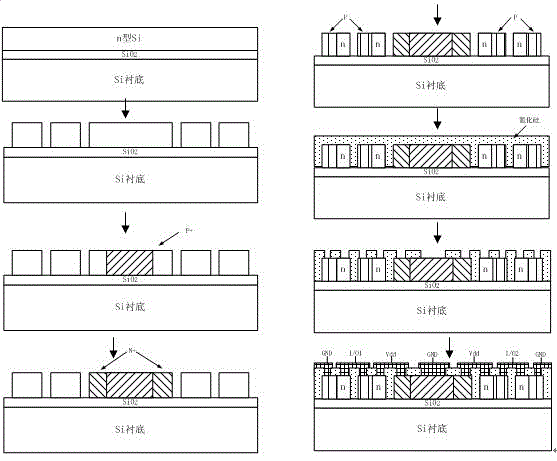

[0051] In order to realize the device of the present invention, in combination with figure 2 with image 3 Given the following implementation steps, such as image 3 as shown,

[0052] step one:

[0053] Take an n-type SOI substrate, clean it to remove surface pollutants, and grow an oxide layer on the surface of the n-t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More