Manufacturing method of anti-PID battery piece and photovoltaic component

A battery sheet and equipment technology, applied in photovoltaic power generation, electrical components, circuits, etc., can solve problems such as rising electrical performance defect rate, loss of efficiency, and loss of benefits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

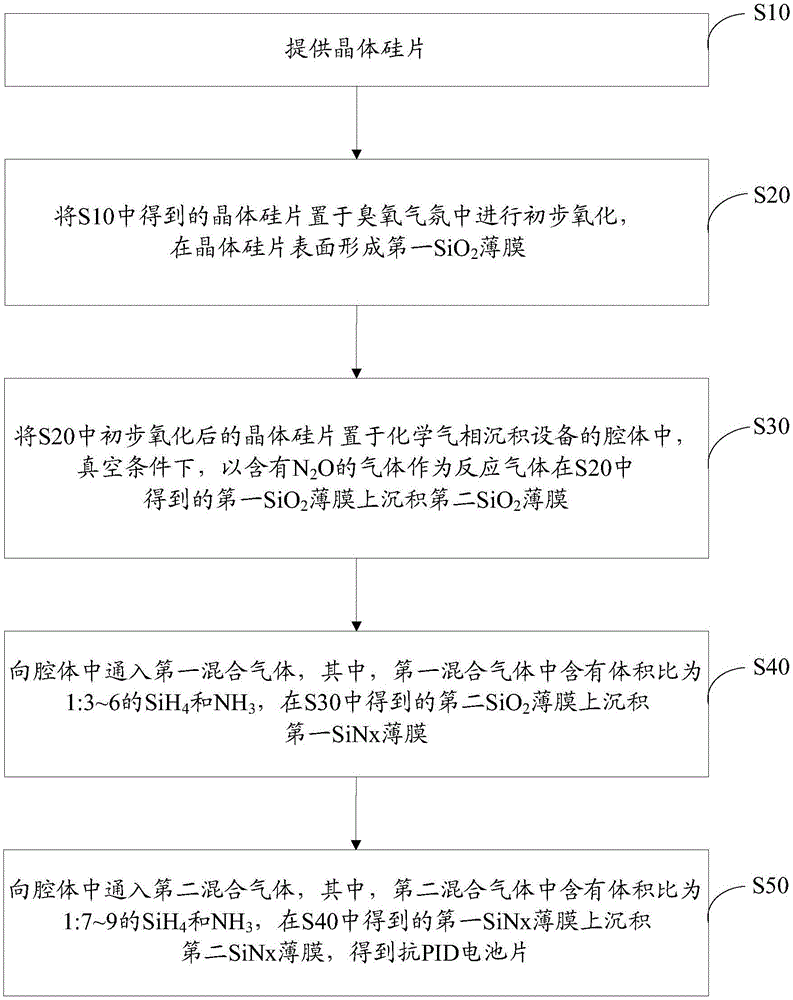

[0028] Such as figure 1 The preparation method of the anti-PID battery sheet of one embodiment shown, comprises the following steps:

[0029] S10, providing a crystalline silicon wafer.

[0030] In one embodiment, the crystalline silicon wafer may be a P-type polycrystalline silicon wafer.

[0031] In another embodiment, the crystalline silicon wafer may be an N-type polycrystalline silicon wafer.

[0032] In other embodiments, the crystalline silicon wafer may also be a single crystal silicon wafer or the like.

[0033] Specifically, before placing the crystalline silicon wafer in an ozone atmosphere for preliminary oxidation, pretreatment of the crystalline silicon wafer is also included, and the pretreatment includes texturing, diffusion and etching cleaning of the crystalline silicon wafer. After pretreatment, the oxidation of crystalline silicon wafers can be promoted, and the anti-PID performance of crystalline silicon wafers can be improved.

[0034] S20, placing th...

Embodiment 1

[0070] The P-type polysilicon wafer is sequentially subjected to conventional acid texturing and diffusion (forming a P-shaped region and an N-shaped region after diffusion), and then wet-etched and cleaned. Put the crystalline silicon wafer in the ozone oxidation equipment, pass oxygen into the ozone oxidation equipment, and oxidize the crystalline silicon wafer under the irradiation of ultraviolet light to form the first SiO2 on the surface of the crystalline silicon wafer. 2 film. Oxygen flow is controlled at 5 sccm, and compressed air flow is controlled at 10 sccm. First SiO 2 The thickness of the film is about 1 nm. Obtain the first SiO deposited on the surface of the crystalline silicon wafer 2 Thin film cells.

Embodiment 2

[0072] Adopt the same method as embodiment 1 to form the first SiO on the surface of crystalline silicon wafer 2 film. Then place the pre-oxidized crystalline silicon wafer in a tubular PECVD furnace tube, and vacuumize to maintain the vacuum degree in the cavity at about 1700mTor. Use N 2 Purge the crystalline silicon wafer after initial oxidation, and then pass N 2 O, the gas flow rate is 7000sccm, the reaction temperature is controlled at 450°C, the sputtering power is 5600W, and the coating time is about 100s. 2 A second SiO with a thickness of about 5 nm is deposited on the film 2 film. pump out the N in the cavity 2 O, keep the vacuum in the cavity at about 1600mTor, and pass the first mixed gas, SiH in the first mixed gas 4 The gas flow is 880sccm, NH 3 The gas flow rate is 3700sccm, the sputtering power is 6400W, and the coating time is about 150s. In the second SiO 2 Deposit the first SiN with a thickness of about 10nm on the film x film. Then pass into the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More