Method for realizing enhanced HEMT (high-electron mobility transistor) by using P-type nitride electrochemical etching

An electrochemical and enhanced technology, applied in the field of microelectronics technology, can solve the problems of small etching selection ratio, difficult to control P-type semiconductor etching, etc., and achieve large etching control window, easy mass production, repeatability Good results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

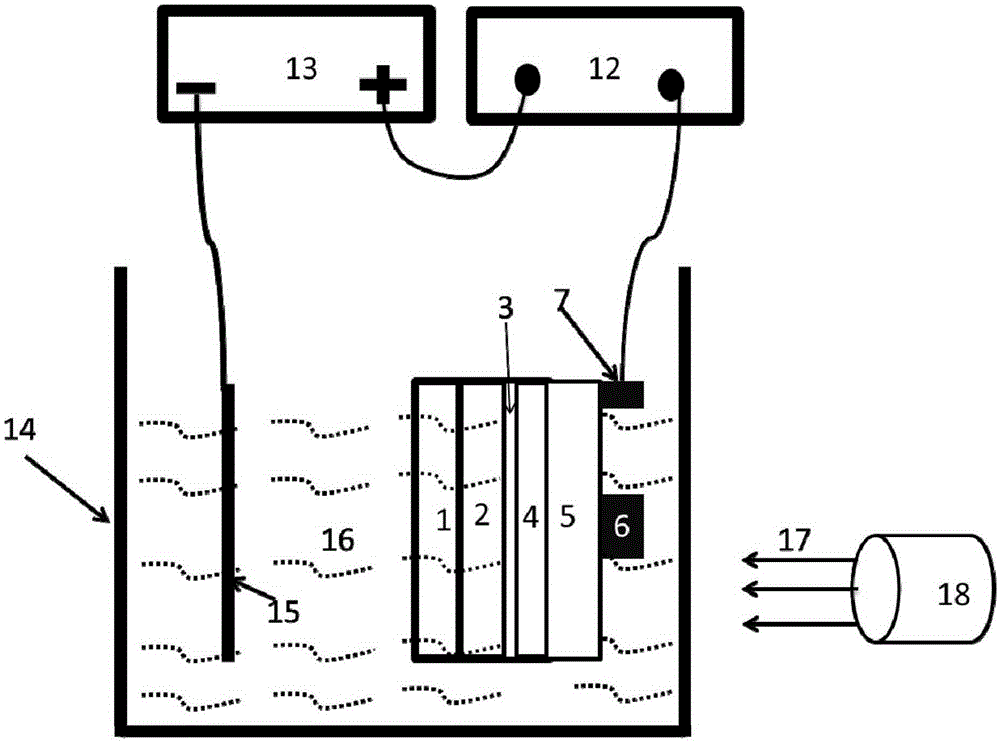

[0016] One aspect of the present invention provides a method for realizing enhanced HEMT by electrochemical etching.

[0017] In some embodiments, the method may include:

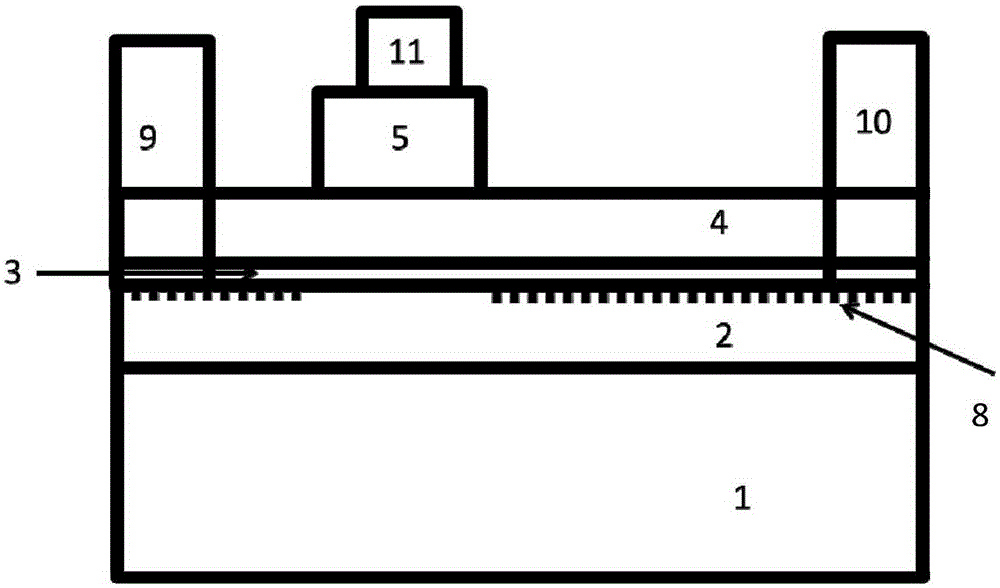

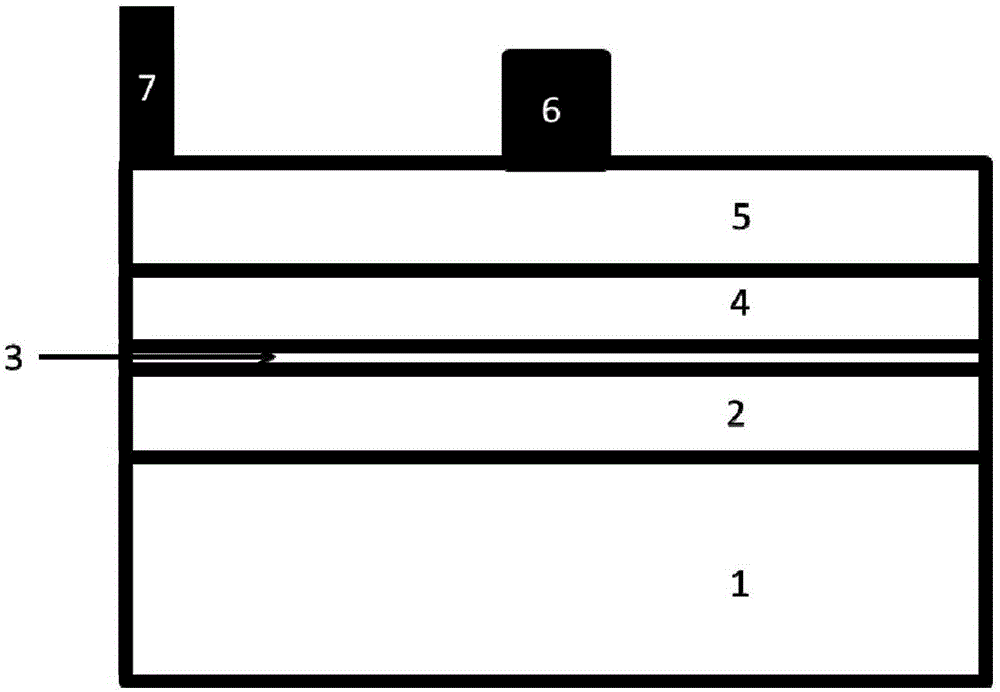

[0018] Provide an etching sample (also referred to as the sample below), the epitaxial structure of the etching sample includes: a heterostructure mainly composed of a first semiconductor layer as a channel layer and a second semiconductor layer as a barrier layer , and, a third semiconductor layer disposed on the second semiconductor layer and depleting the two-dimensional electron gas in the heterostructure conductive channel, and the conductivity of the third semiconductor layer is higher than that of the second semiconductor layer semiconductor layer;

[0019] setting a patterned etching mask on the third semiconductor layer, and directly exposing a region of the third semiconductor layer exposed from the etching mask to an etching solution; The three semiconductor layers provide an etching current wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More