Serial communication clock data recovery system with low sampling rate

A clock data recovery, serial communication technology, applied in the direction of automatic power control, electrical digital data processing, instruments, etc., can solve the problems of increasing the difficulty of clock circuit design, high frequency requirements, etc., to reduce the design difficulty, reduce design requirements, The effect of low dynamic power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Below in conjunction with accompanying drawing and specific embodiment, the present invention is described in further detail:

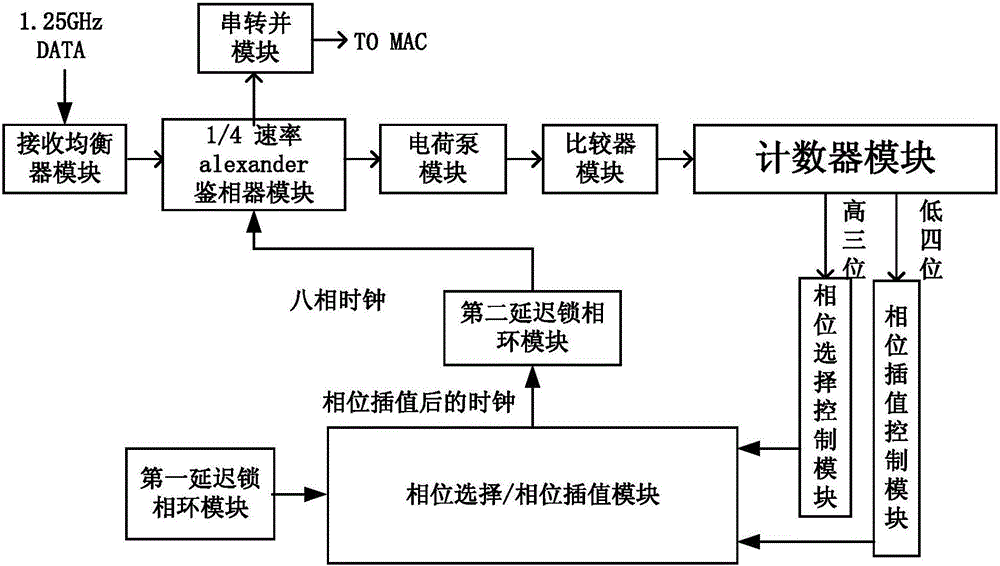

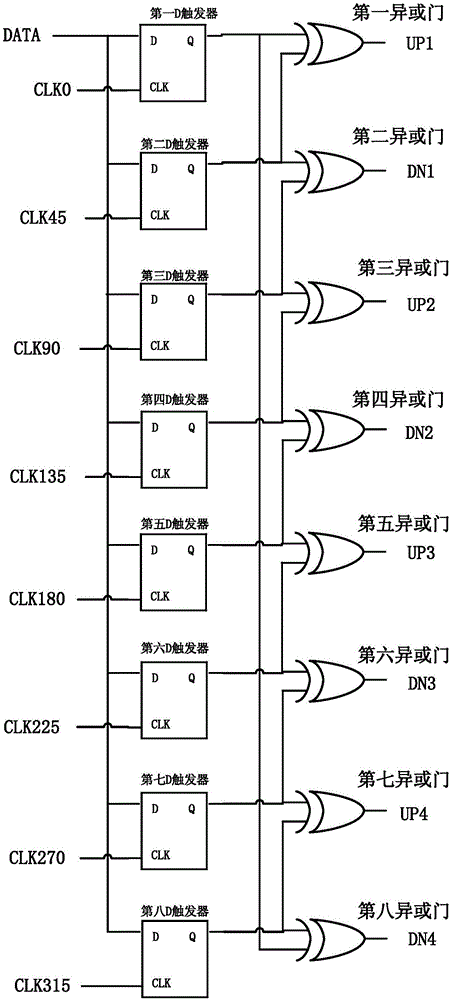

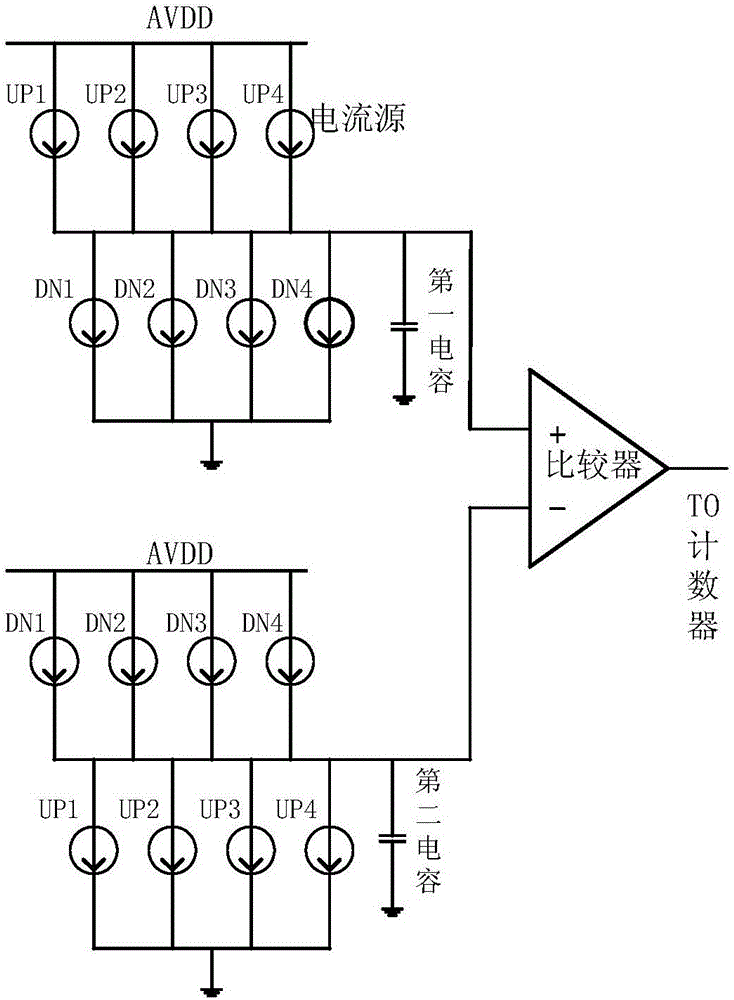

[0036] like figure 1 Shown is a block diagram of the overall structure of the system. It can be seen from the figure that a serial communication clock data recovery system with low sampling rate is characterized in that: it includes a receiving equalizer module, a 1 / 4 rate alexander phase detector module, a serial-to-parallel module, a charge a pump module, a comparator module, a counter module, a first delay phase locked loop module, an 8-phase reference clock module, a phase selection / phase interpolation module, a second delay phase locked loop module, a phase selection control module and a phase interpolation control module;

[0037] Receiving equalizer module: Receive the 1.25GHz serial signal from the external photoelectric conversion module, compensate the serial signal, and generate the compensated serial signal; and transmit the compens...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com