Manufacturing method of vertical device with GaN epitaxial layer growing on silicon substrate

A manufacturing method and epitaxial layer technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

[0066] figure 2 According to the flow chart of the manufacturing method of vertical GaN-based Schottky diode semiconductor device of the present invention, reference will be made below figure 2 , the method for manufacturing the vertical GaN-based Schottky diode semiconductor device of the present invention is described in detail.

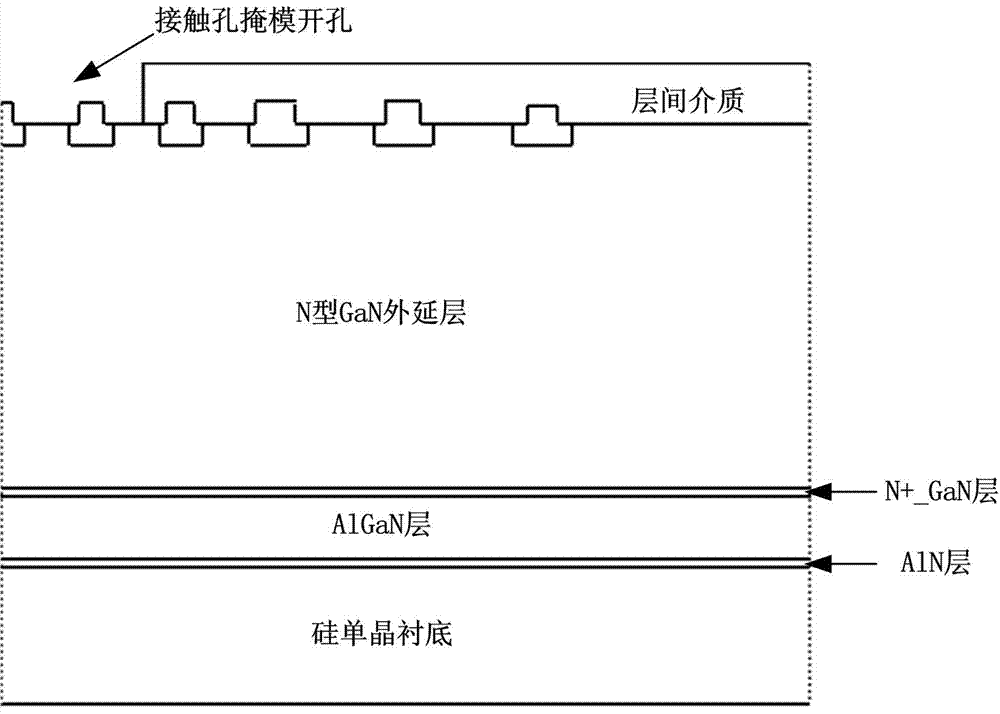

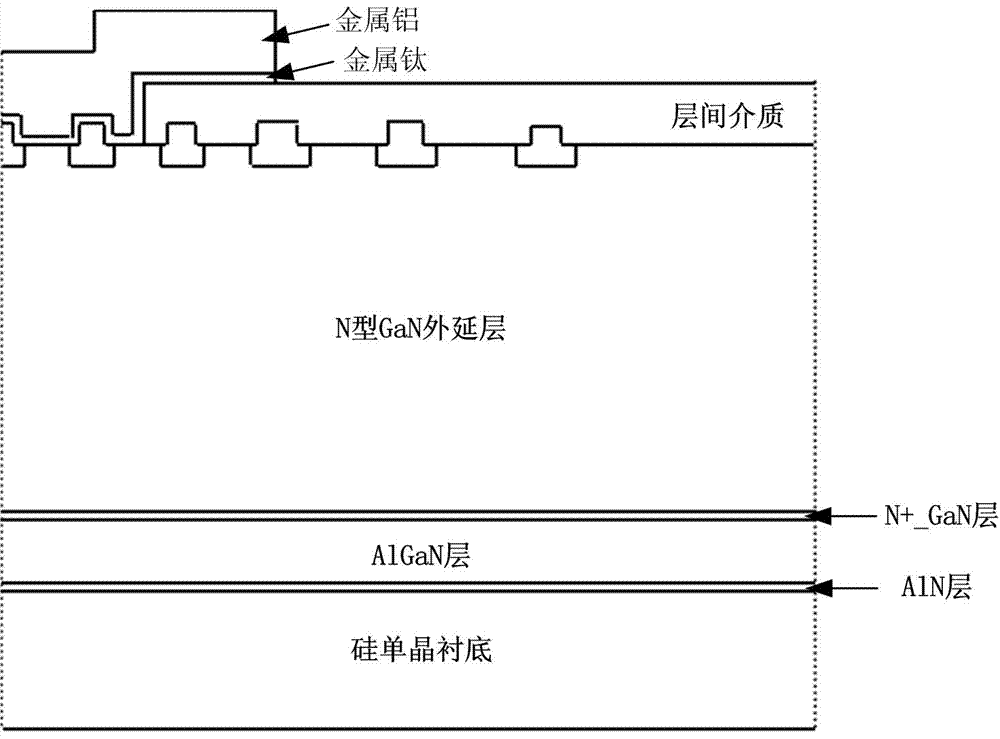

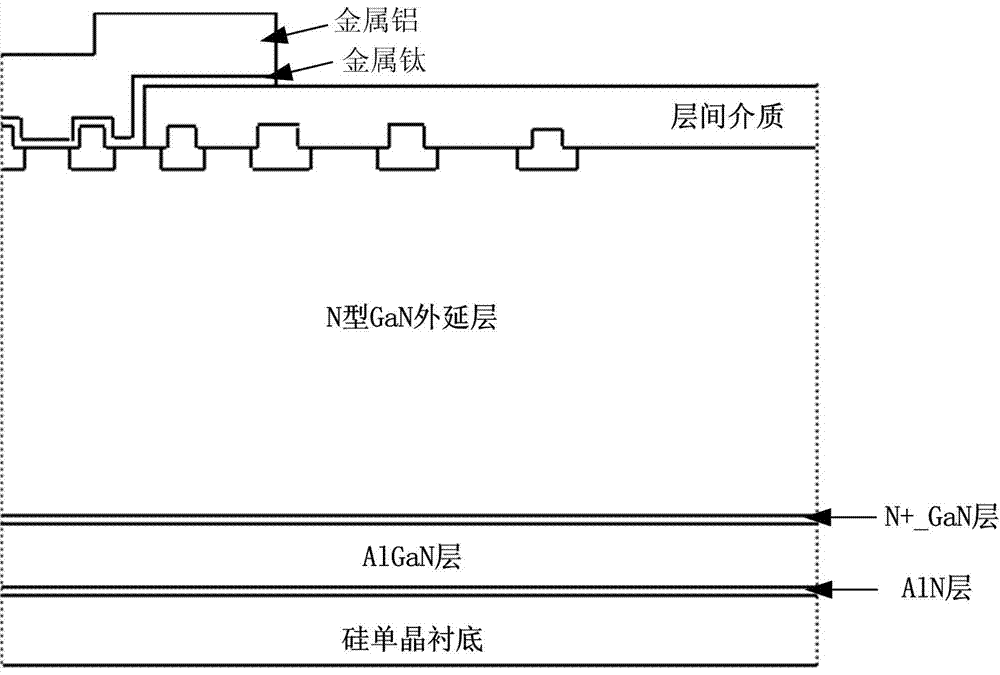

[0067] First, in step 201, an AlN layer, an AlGaN layer, a high electron concentration N-type GaN epitaxial layer (N+_GaN layer), and a low electron concentration N-type GaN epitaxial layer (N type epitaxial layer) are sequentially grown on a silicon single crystal substrate And P type GaN epitaxial layer (P type epitaxial layer). F...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More