P-type crystalline silicon cell structure and manufacturing method thereof

A crystalline silicon battery and battery technology, applied in the field of solar cells, can solve the problems of battery leakage and component packaging problems that have not been solved well, and have not been applied on a large scale, so as to achieve good battery performance, reduce light shading area, and improve the operation process. simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

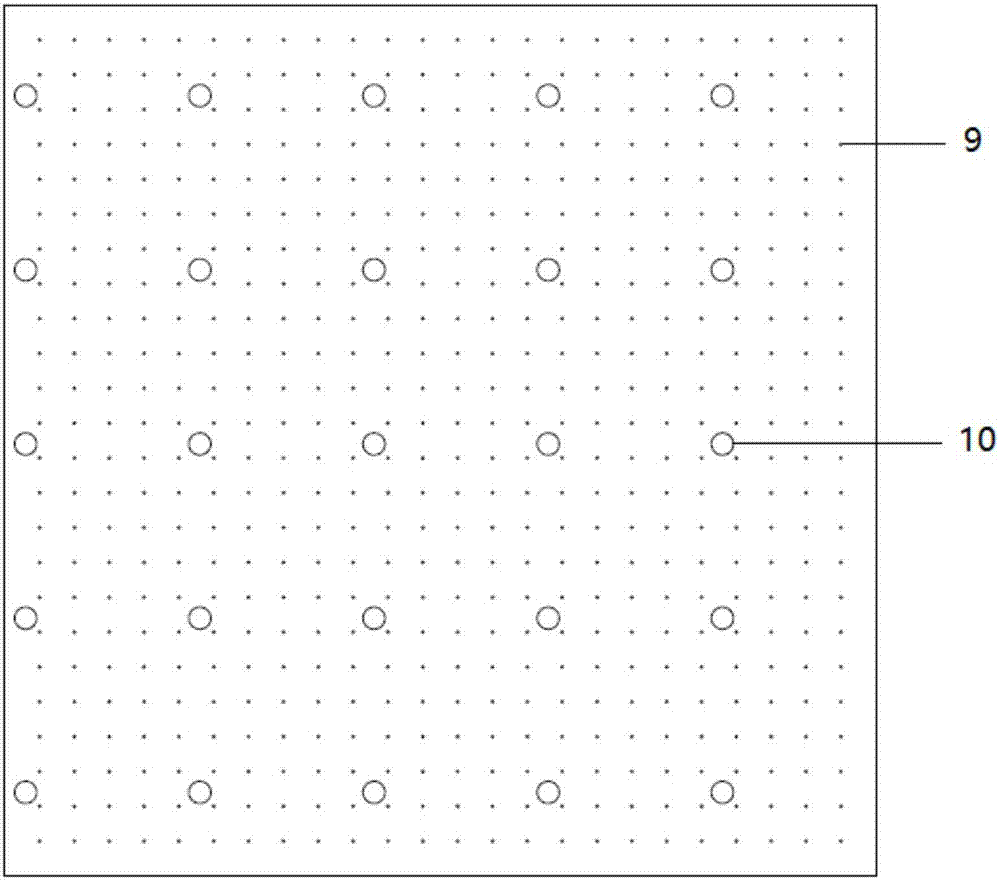

[0052] (1) A laser is used to form 5×5 equally spaced through holes on a P-type monocrystalline silicon wafer, and the diameter of a single through hole is 500um.

[0053] (2) Anisotropically etch the P-type monocrystalline silicon wafers with through holes in a KOH solution at about 80°C to obtain a surface pyramid structure.

[0054] (3) Use POCl3 as the dopant for low-pressure diffusion at 800-900°C to form an N-type layer on the front surface of the silicon wafer and the surface layer of the through-hole wall, and the square resistance after doping is 75Ω / □.

[0055] (4) Using inkjet method to spray wax on the through hole and its surrounding area.

[0056] (5) Use wet etching to remove the phosphosilicate glass, back knots and paraffin wax on the front side of the silicon wafer.

[0057] (6) The etched silicon wafer is annealed in an annealing furnace at 650° C., and a dense thermal silicon oxide is grown on the surface of the silicon wafer.

[0058] (7) A PECVD method was used to d...

Embodiment 2

[0064] (1) A laser is used to form 6×6 equally spaced through holes on the P-type polysilicon wafer, and the diameter of a single through hole is 400um.

[0065] (2) Put the P-type polycrystalline silicon wafers with through holes in a dry plasma texturing equipment to obtain a polymorphic micro-nano structure, and then perform surface modification in a BOE solution.

[0066] (3) Using PH3 as an impurity, doping with ion implantation, forming an N-type layer on the front surface of the silicon wafer and the surface layer of the through-hole wall, the square resistance after doping is 80Ω / □.

[0067] (4) Using inkjet method to spray wax on the through hole and its surrounding area.

[0068] (5) Use wet etching to remove the phosphosilicate glass, back knots and paraffin wax on the front side of the silicon wafer.

[0069] (6) The ALD method is used to deposit 20nm of aluminum oxide and 60nm of silicon nitride on the back of the silicon wafer; the ALD method is used to deposit 20nm of sil...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Line width | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More