double-link interconnection architecture based on a three-dimensional Mesh network-on-chip

An on-chip network and interconnection architecture technology, which is applied to architectures with a single central processing unit, instruments, general-purpose stored program computers, etc. power consumption, signal delay and large crosstalk, etc., to achieve the effect of improving throughput, reducing delay, and alleviating congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

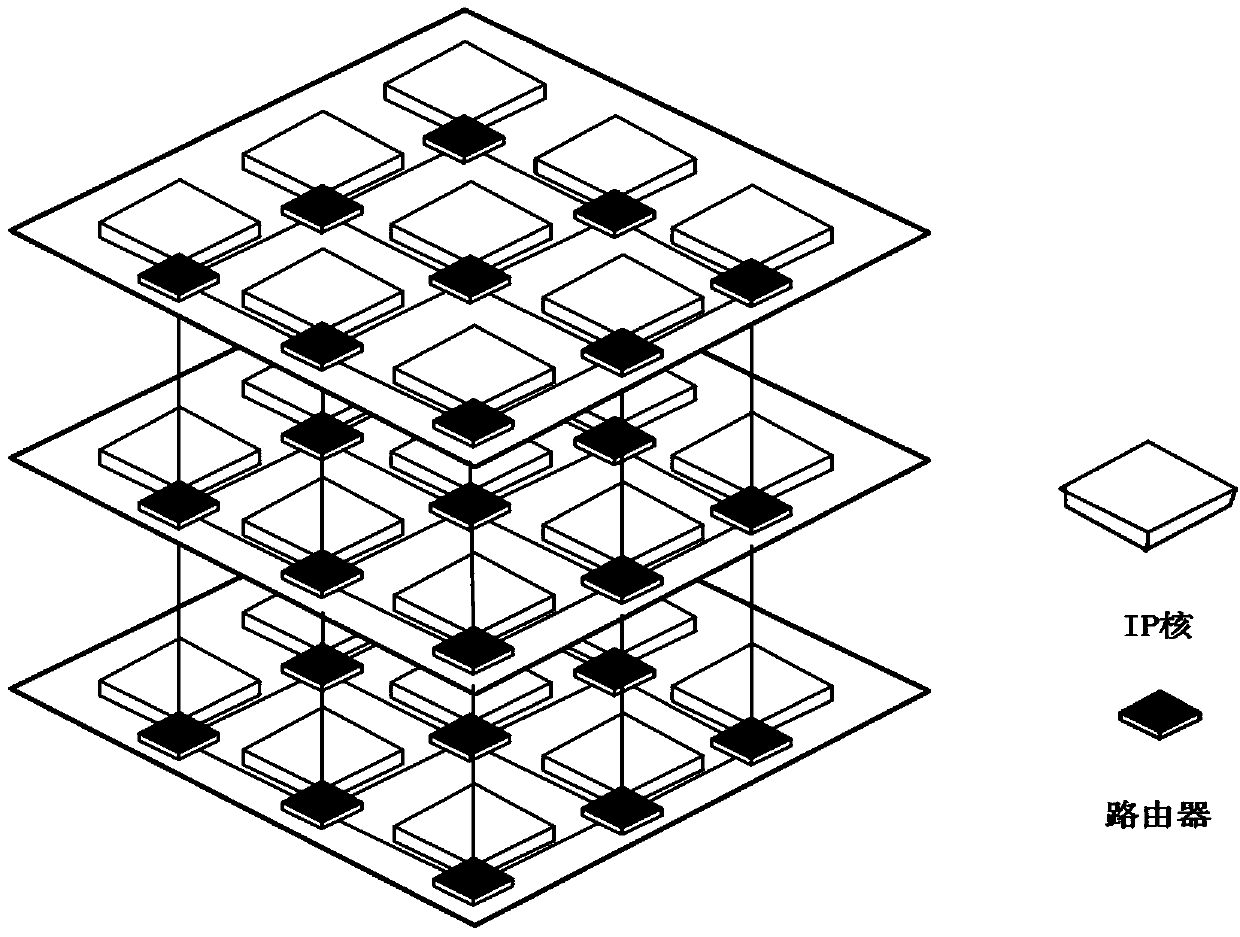

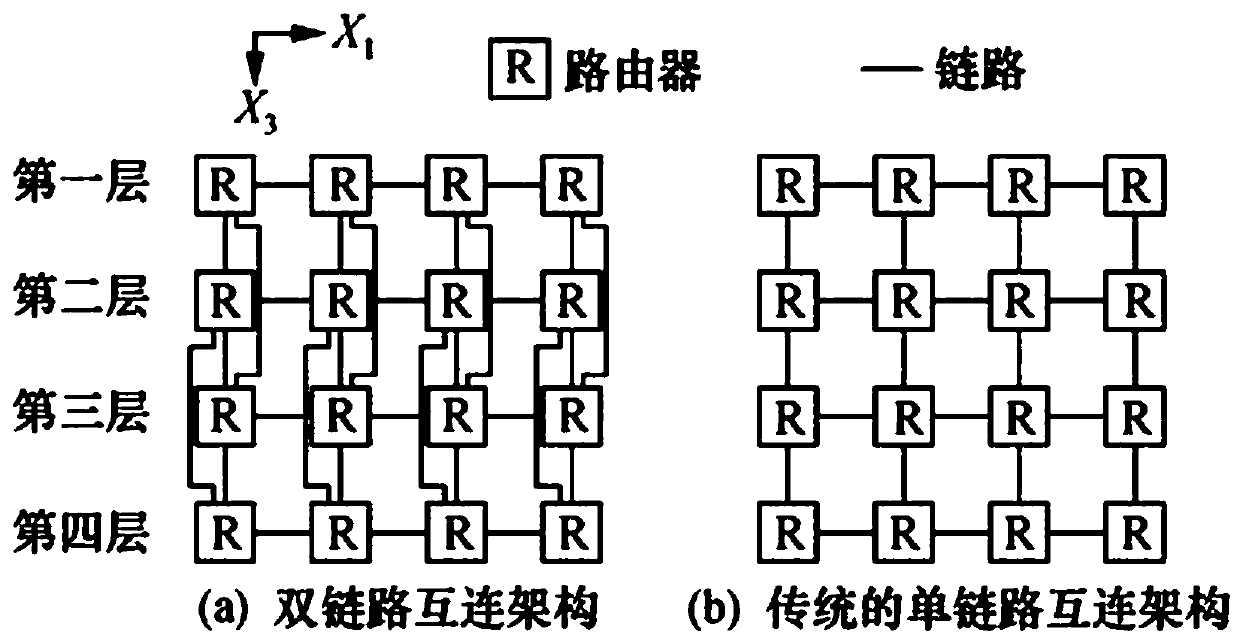

[0018] figure 1 Shown is the topological structure diagram of the three-dimensional Mesh network on chip, which has the characteristics of low signal delay and crosstalk, low energy consumption and high integration. The three-dimensional network-on-chip topology combines the network-on-chip with three-dimensional integrated circuit technology, distributes the IP cores on different physical layers of the chip, and uses the three-dimensional structure to realize the communication between the IP cores, and is used to build a low-energy, short-latency on-chip network system. Due to the extremely short vertical communication distance of vias interconnected between layers, this topology will enhance the communication capability of the entire system. Compared with two-dimensional on-chip networks, three-dimensional on-chip networks have the following advantages: (1) Increased packaging density, reduced chip area and energy consumption, and shortened the time to market of chips; (2) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More