Preparation method of stackable large-area nano wire intersected lattice array resistive switching memory device structure

A technology of silicon nanowire array and resistive variable storage, which is applied in the direction of electrical components and can solve the problems of large-scale integration of memristive units

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

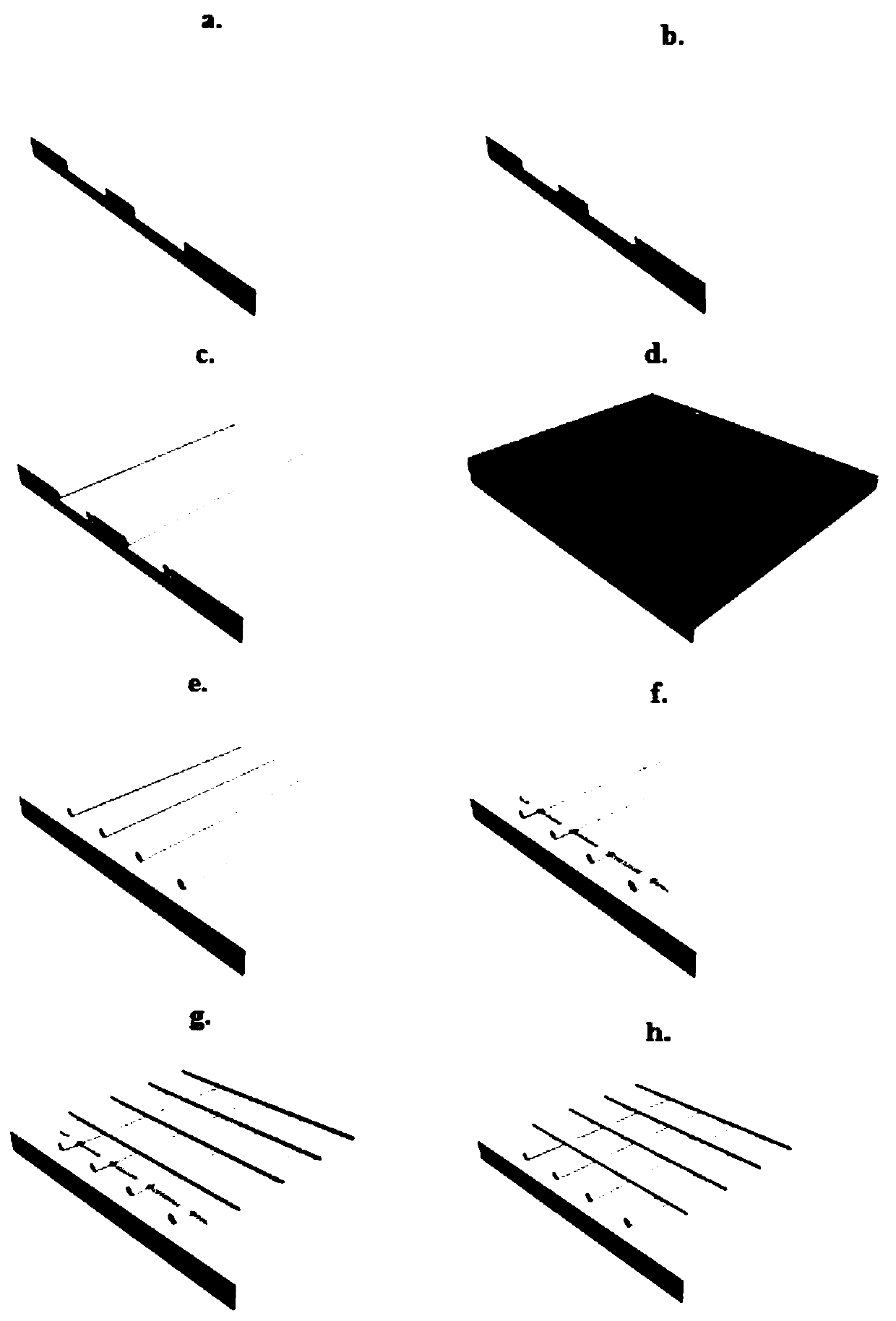

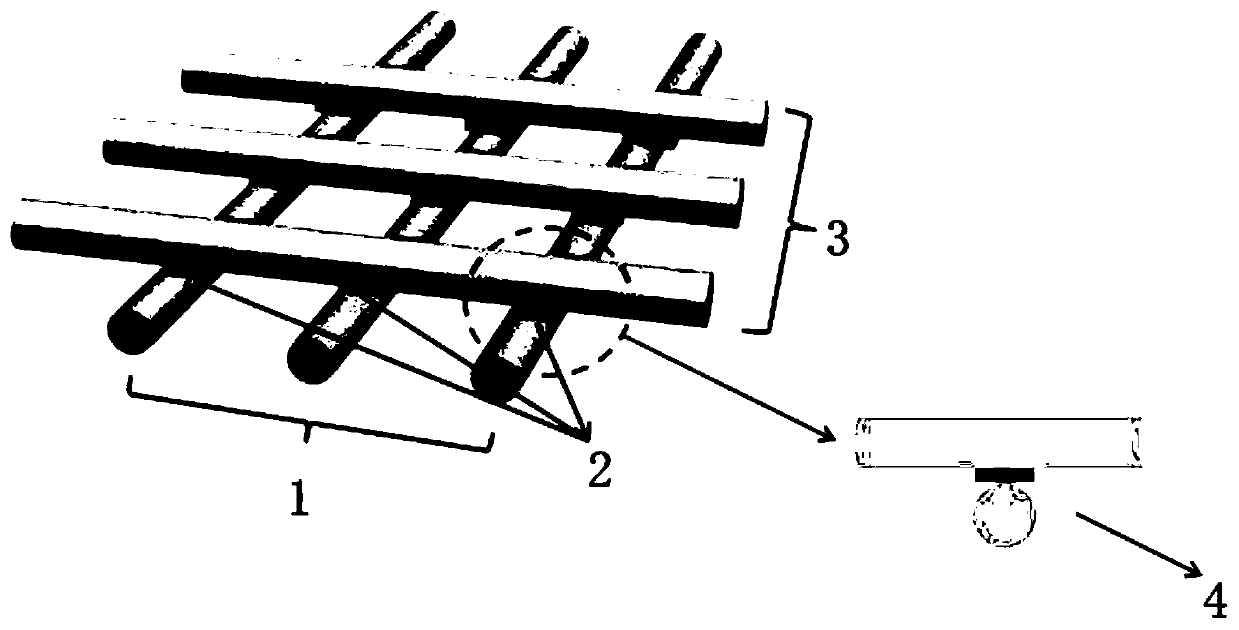

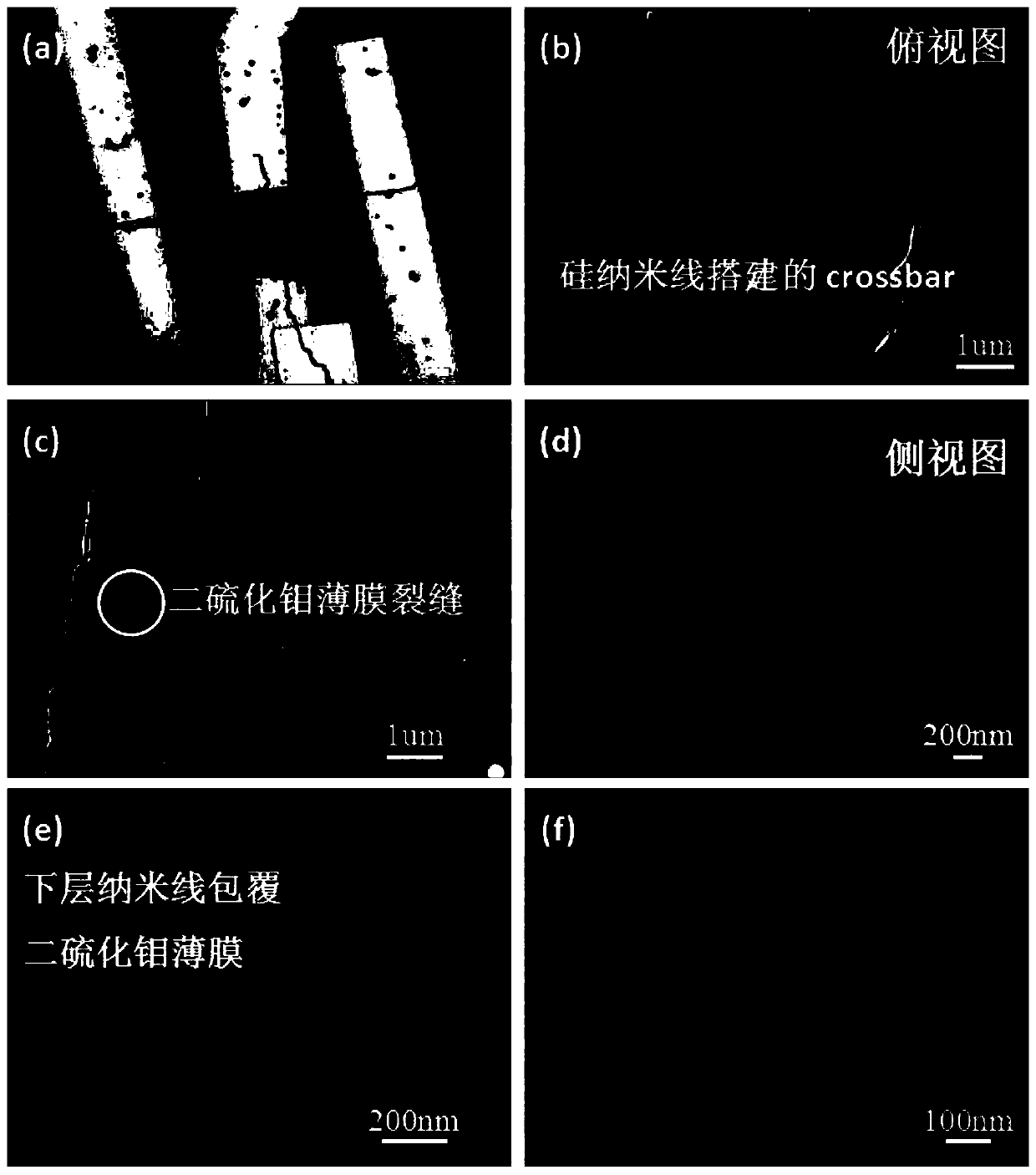

[0032] Such as figure 1 Shown is a method for fabricating a nanowire intersection array resistive memory device structure that can be stacked and prepared in a large area, which specifically includes the following steps:

[0033] 1) Process the pure silicon wafer in PECVD equipment to obtain a silicon oxide wafer covered with a silicon dioxide layer, that is, a silicon-based substrate;

[0034] 2) Define the growth guide channel on the surface of the silicon oxide wafer by means of photolithography, electron beam direct writing (EBL) or mask, and use inductively coupled plasma (ICP) etching or reactive plasma etching (RIE), etc. Technology Dry etching of exposed silicon-based substrates, in which reactive gases with different chemical properties such as SF6, CF4 (or their mixed gases) can be used as etchant to form planar distribution etching channels;...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More